信號完整性(Signal Integrity,SI)是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。

2023-09-28 11:27:47 1003

1003

提供的制造允許誤差和鄰近布線的影響。 在信號完整的理想情況下,所有高速節點應該布線在阻抗控制內層(例如帶狀線),但是實際上,工程師必須經常使用外層進行所有或者部分高速節點的布線。要使SI最佳并保持

2014-12-15 14:01:07

做了電路設計有一段時間,發現信號完整性不僅需要工作經驗,也需要很強的理論指導,壇友能提供一些信號完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

在處理高速印刷電路板(PCB)時,必須理解信號完整性(SI)和電源完整性(PI)的基本原理。如今,速度是評估數字產品功能的主要因素之一。在幾種設計中,PCB布局對整體功能至關重要。對于高速設計,SI

2021-12-30 06:49:16

信號完整性100條經驗規則

2020-12-29 06:55:21

高速設計中的信號完整性和電源完整性分析

2021-04-06 07:10:59

采用的信源及信道編碼技術,如時鐘擴頻、預加重技術等可以改善信號在特定環境中的傳輸性能。 結合信號完整性與電源完整性的定義,對參考端口的選取需要滿足可測性原則,這對于工程實現或調試有著直接的意義。但對

2015-01-07 11:33:53

信號完整性與電源完整性的仿真分析與設計,不看肯定后悔

2021-05-12 06:40:35

其實電源完整性可做的事情有很多,今天就來了解了解吧。信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸

2021-11-15 07:37:08

得講講電源完整性。話不多說,直接上圖:01.區別記得剛接觸信號完整性的時候,對電源完整性(PI)和電源工程師之間的關系是分不清的。后來才漸漸了解這里面的千差萬別。簡單來說,電源的產生與轉化,比如Buck電路,LDO,DC-DC等,源端部分這些是電源工程師來確定的。電源工程師也會進行相關的電源可靠性設

2021-11-15 06:32:45

行業工程技術人員提高在信號完整性分析方面的專業技能,利用仿真工具快速掌握分析SI和PI問題的工具和技巧,為企業培養優秀的SI工程師,提高產品質量和可靠性,增強產品在國內國際的市場競爭力。中國電

2009-11-25 10:13:20

信號完整性關鍵名詞都有什么 ?

2021-03-05 08:09:37

信號完整性資料

2015-09-18 17:26:36

很不錯的一本信號完整性教材。其實EMC、EMI問題最終都是信號完整性問題。

2011-12-09 22:49:23

信號完整性分析與設計信號完整性設計背景???什什么是信號完整D??信信號完整性設計內è??典典型信號完整性問題與對2現在數字電路發展的趨ê??速速率越來越???芯芯片集成度越來越高£PC板板越來越

2009-09-12 10:20:03

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

信號完整性基礎

2013-11-14 22:26:42

信號完整性處理的8個基本原則

2021-01-14 07:19:08

://pan.baidu.com/s/1jG0JbjK信號完整性小結1、信號完整性問題關心的是用什么樣的物理互連線才能確保芯片輸出信號的原始質量。2、信號完整性問題一般分為四種:單一網絡的信號質量、相鄰網絡間的串

2015-12-12 10:30:56

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

信號完整性的話題一直是專家們研究和突破的話題,我們今天就說說那些主要的信號完整性的測試手段(波形測試、眼圖測試、抖動測試)。目前應用比較廣泛的信號完整性測試手段應該是波形測試,即使用示波器測試波形

2020-04-10 10:33:00

請問一下信號完整性的價值是什么?

2021-04-09 06:15:23

、Sigrity,對于信號完整性工程師來講至少要熟悉一種仿真軟件。這樣才能增加你設計的信心。本資料系統整合了相關資料,工程師們可根據自身情況選擇適合自己的學習資料,以下為資料截圖:參與以下活動還可以獲得精美書籍:【送書福利】不懂PDN談何電源完整性?請收下這本PDN設計指導硬核書

2019-09-03 17:54:59

印制板)和系統的核心技術就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發展表明:互連正在取代器件,躍升為高速電路設計的主角。信號完整性分析是高速互連設計的支撐與保障。要想精通高速

2010-05-29 13:29:11

很小的差異導致高速系統設計的失敗; 在電子產品向高密和高速電路設計方向發展的今天,解決一系列信號完整性的問題,成為當前每一個電子設計者所必須面對的問題。業界通常會采用在PCB制板前期,通過信號完整性

2015-12-28 22:25:04

Cadenc高速電路設計SI PI 信號完整性電源完整性仿真視頻教程下載鏈接地址:鏈接:http://pan.baidu.com/s/1pJiPpzl密碼:3yjv

2015-07-30 21:44:10

EMC工程師需要具備那些技能?從企業產品需要進行設計、整改認證的過程看,EMC工程師必須具備以下八大技能:1、EMC的基本測試項目以及測試過程掌握;2、產品對應EMC的標準掌握;3、產品的EMC整改

2012-05-08 15:31:12

EMC工程師需要具備那些技能?從企業產品進行需求設計,整改認證的過程來看,EMC工程師必須具備以下八大技能:

2019-05-30 06:28:39

在一定條件下的運行情況,來判斷電路的正確性。經常使用的動態觀測技術包括各種漏斗測試和信號探針。

仿真是FPGA工程師進行測試驗證工作的重要方法。仿真可以幫助工程師確定是否有設計缺陷、時序問題或電流漏失等

2023-11-09 11:03:52

PCB Layout and SI 信號完整性 問答專家解答以及相關經典資料18篇,附件太多,只上傳一個經典的,其他需要學習的自己下了.PCB Layout and SI 問答專家解答(經典資料

2008-12-25 09:49:59

信號完整性(Signal Integrity, SI)是指信號在信號線上的質量,即信號在電路中以正確的時序和電壓作出響應的能力。如果電路中信號能夠以要求的時序、持續時間和電壓幅度到達接收器,則可

2018-11-27 15:22:34

多個元件和網絡的PCB獨立或分工進行合理和各功能板塊布局和布線,能在布局布線過程中隨時考慮熱 設計、結構設計、SI、PI、EMC、美觀、可制造性等方面的要求并提出解決方案,能對入門級和初級PCB工程師

2015-01-23 10:31:26

原理圖的設計、PCB設計,因而電子研發工程師所面臨的PCB設計挑戰也不斷增加:信號完整性(SI),電源完整性(PI)、EMC/EMI以及熱分析、可制造性等等問題。那咋解決了?嘿嘿,別擔心,電子發燒友網即將舉辦

2015-03-31 17:16:48

的影響。 在信號完整的理想情況下,所有高速節點應該布線在阻抗控制內層(例如帶狀線),但是實際上,工程師必須經常使用外層進行所有或者部分高速節點的布線。要使SI最佳并保持電路板去耦,就應該盡可能將接地層/電源層

2014-11-19 13:46:37

VNA是如何測量高速器件的信號完整性(SI)?

2021-05-11 06:49:40

工程技術人員提高在信號完整性分析方面的專業技能,利用仿真工具快速掌握分析SI和PI問題的工具和技巧,為企業培養優秀的SI工程師,提高產品質量和可靠性,增強產品在國內國際的市場競爭力。中國電

2009-11-18 17:28:42

allegro_SI_信號完整性仿真

2014-05-16 10:43:51

:1.2016或2017屆本科以上學歷,電子、信號與通訊類專業,碩士優先;2.一年以上工作經驗,有硬件、測試經驗者優先;3.有很好的數/模電路基礎、信號完整性和微波理論基礎,對SI/PI/EMI有一定認識

2017-11-17 11:40:28

本帖最后由 KnightZhang 于 2016-8-24 10:38 編輯

【信號完整性工程師】1. 高速信號完整性測試2. 使用過以下SI 工具之一: Cadence

2016-08-24 10:35:38

`編輯推薦《國外電子與通信教材系列:信號完整性與電源完整性分析(第二版)》強調直覺理解、實用工具和工程素養。作者以實踐專家的視角指出造成信號完整性問題的根源,并特別給出了設計階段前期的問題解決

2017-09-19 18:21:05

功能混亂。PCB信號完整性的步驟在信號完整的理想情況下,所有高速節點應該布線在阻抗控制內層(例如帶狀線)。要使SI最佳并保持電路板去耦,就應該盡可能將接地層/電源層成對布放。如果只能有一對接地層/電源層

2019-09-25 07:30:00

`于博士首本結合了工程實踐經驗,深度剖析信號完整性設計理論基礎的著作,大多為十余年的SI工程設計經驗匯總,非常值得借鑒學習。`

2021-04-06 11:01:41

,當把其位置調整合適后將會變成藍色,表示信號在器件之間的延時已經滿足Propdelay規定的范圍了。文章連載>>【轉載】Allegro SI 高速信號完整性仿真連載之二(附

2019-11-19 18:55:31

、鉆孔數據文件。 后仿真驗證: 信號完整性(SI)后仿真,電源完整性(PI)后仿真,電磁兼容性(EMI)后仿真。 以下將逐個介紹如何在Cadence的高速設計流程中實現這些仿真條件,通過仿真分析,得到

2019-11-19 19:14:25

工作經驗,熟練使用CADENCE ALLEGRO16.6、CAM350、SI9000等相關EDA設計軟件;3、了解PCB的生產加工工藝和PCBA制造流程,對PCB的DFM設計和EMC設計,信號完整性有

2016-02-16 20:02:48

`9年IC布局工程師來做客,聊聊PADS、信號完整性【高手問答】第18期 小編導讀:本期高手問答(12.5~12.19)邀請到了9年工作經驗的IC布線設計師覃工,覃工擅長手機PCB設計,工控行業

2014-12-08 10:32:39

提升工程師的設計能力。本課程詳細介紹了信號完整性(SI)和電源完整性(PI)知識體系中重要的知識點,以及經常導致設計失敗的隱藏的風險點。圍繞這些知識點,通過一個個案例逐步展開系統化設計方法的理念、思路

2016-05-05 14:26:26

什么時候需要進行信號完整性分析

2014-12-10 10:30:11

想了解什么是信號完整性的朋友,可以進來看看

2013-04-24 14:11:10

首先我們定義下什么是電源和信號完整性?信號完整性 信號完整性(SI)分析集中在發射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側重于電源分配網絡 (PDN) 提供恒定

2021-12-30 06:33:36

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

各位大俠,請問大家用什么工具來做電源信號完整性仿真,cadence中有其SI 和 PI工具,為什么有些教程是在allegro中嵌入Ansoft 的siwave工具來仿真 這兩者有很大區別嗎?另外做完后仿真后,如果性能不佳 怎么整改?只能重新布線?

2016-08-12 13:42:28

資深硬件工程師的高速信號完整性仿真實例操作,用的是allegro,很有價值。[hide][/hide]

2020-07-13 23:18:49

分享資深硬件工程師視頻講解信號完整性原理,學PCB設計和SI仿真的值得一看。

2020-07-04 00:58:42

基于信號完整性分析的PCB設計流程如圖所示。 主要包含以下步驟: 圖 基于信號完整性分析的高速PCB設計流程 (1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立

2018-09-03 11:18:54

空間,最后在解空間的基礎上來完成PCB板的設計和校驗。 隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。元器件和PCB板的參數、元器件在

2018-08-29 16:28:48

空間,最后在解空間的基礎上來完成PCB板的設計和校驗。 隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。元器件和PCB板的參數、元器件在

2008-06-14 09:14:27

如何保證脈沖信號傳輸的完整性,減少信號在傳輸過程中產生的反射和失真,已成為當前高速電路設計中不可忽視的問題。

2021-04-07 06:53:25

布線必須考慮的關鍵因素。因為時序要求嚴格,這種節點通常必須采用端接器件才能達到最佳SI質量。要預先確定這些節點,同時將調節元器件放置和布線所需要的時間加以計劃,以便調整信號完整性設計的指針。5、技術

2018-07-31 17:12:43

高速數字PCB設計信號完整性解決方法

2021-03-29 08:12:25

極大限制了阻抗控制的作用。此外,布線層少將加劇串擾,同時信號線間距還必須最小以布放更多的印制線。另一方面,設計工程師必須采用最新和最好的CPU、內存和視頻總線設計,這些設計就必須考慮SI問題。關于布線

2014-12-22 14:49:59

何為信號完整性?信號完整性包括哪些?干擾信號完整性的因素有哪些?如何去解決?

2021-05-06 07:00:23

高速PCB頻發故障,使得信號完整性問題越來越受到工程師的重視。有關高速PCB信號完整性的相關內容網絡上有很多,這方面的知識點很容易找到資源學習,我本人也寫過一本拙作《信號完整性揭秘》。但是,學習理論

2017-06-23 11:52:11

我目前處于電子行業學習的初級階段,想從事電子工程師或者硬件工程師行業,請問需要具備哪些知識,要學哪些東西?希望各位能幫助我成長

2013-04-25 11:24:31

。測試必須徹底,并且具有足夠快的速度能跟上產品上市的步伐,還必須符合緊縮的預算。測試工程師應該采用一種合適的方法來管理多方面的折衷因素,并針對特定情形找出最合適的解決方案。

2021-03-11 07:32:20

時序分析-- 信號完整性問題(SI)

2014-05-16 10:44:11

信號完整性(SI)問題解決得越早,設計的效率就越高,從而可避免在電路板設計完成之后才增加端接器件。SI設計規劃的工具和資源不少,本文主要探索,究竟還有什么辦法可以確保信號完整性?

2019-08-02 07:52:35

設計的始終。電路原理設計是確保高速電路信號完整性的關鍵環節,包括 電路系統、原理框圖及具體電路的設計 。信號完整性工程師必須精通這些基本技能,以實現系統設計的目標。簡言之,電路原理設計在確保信號在傳輸

2024-03-05 17:16:39

對于PCB電路設計、分析,這些信號分析基礎是我們硬件工程師必須知道的,希望對各位工程師有點幫助。

2016-11-29 08:57:51

布線的影響。 在信號完整的理想情況下,所有高速節點應該布線在阻抗控制內層(例如帶狀線),但是實際上,工程師必須經常使用外層進行所有或者部分高速節點的布線。要使 SI最佳并保持電路板去耦,就應該盡可能

2015-01-07 11:44:45

。此外,布線層少將加劇串擾,同時信號線間距還必須最小以布放更多的印制線。另一方面,設計工程師必須采用最新和最好的 CPU 、內存和視頻總線設計,這些設計就必須考慮 SI 問題。 關于布線、拓撲結構和端接

2014-11-18 10:20:50

。此外,布線層少將加劇串擾,同時信號線間距還必須最小以布放更多的印制線。另一方面,設計工程師必須采用最新和最好的CPU、內存和視頻總線設計,這些設計就必須考慮SI問題。 &

2009-05-24 23:02:49

,布線層少將加劇串擾,同時信號線間距還必須最小以布放更多的印制線。另一方面,設計工程師必須采用最新和最好的 CPU 、內存和視頻總線設計,這些設計就必須考慮 SI 問題。 關于布線、拓撲結構和端接方式

2018-08-23 08:42:59

信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸的1在接收器中看起來就像 1(對0同樣如此)。在電源

2021-11-15 06:31:24

高級硬件工程師-深圳崗位職責:1. 負責硬件方案制定、原理圖設計及PCB協作。2. 負責硬件測試及可靠性測試。3. 負責單板轉產與維護。任職要求:1. 本科以上學歷,電子、機械、自動化等相關專業,有

2015-01-13 09:53:20

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

年,中國電子電器可靠性工程協會分期組織召開了4期“高速PCB與系統互連設計中信號完整性(SI)分析技術”高級研修班,課程的深度和廣度以及李教授精辟講解受到學員一致好評,應廣大客戶建議,中國電

2010-11-09 14:21:09

在高速PCB電路板的設計和制造過程中,工程師需要從布線、元件設置等方面入手,以確保這一PCB板具有良好的信號傳輸完整性。在今天的文章中,我們將會為各位新人工程師們介紹PCB信號完整性設計中常

2018-11-27 09:57:50

在高速PCB設計中,信號完整性問題對于電路設計的可靠性影響越來越明顯,為了解決信號完整性問題,設計工程師將更多的時間和精力投入到電路板設計的約束條件定義階段。通過在設計早期使用面向設計的信號分析

2018-09-10 16:37:21

隨著通信系統中高速板設計復雜性的日益提高,依賴某一種特定的CAD工具已經無法在可接受的精度范圍內完成整個設計仿真。PCB設計工程師和信號完整性(SI)設計工程師需要采用各種仿真工具。除了價格、性能

2014-12-12 16:14:49

28小時從數字電路工程師到信號完整性工程師:這篇文章講述如何培訓數字電路工程師在信號完整性設計過的成長過渡課程。加強數字電路工程師在

2009-10-27 17:38:35 0

0 信號完整性工程師工作職責,負責單板硬件及互連設計的信號完整性和電源完整性分析,定制芯片級/單板級/系統級設計約束,編寫相關設計要求文檔,負責單板SI設計的正確性

2011-11-30 11:26:49 2717

2717 《信號完整性工程師的最佳伴侶》涵蓋了從可行性研究到檢驗,從仿真到測試的整個生命周期,為針對高速數字設計進行現代信號完整性的測試測量提供了實用指南

2011-11-30 11:30:33 2319

2319 信號完整性工程師總結的精華100例,下面是一位信號完整性工程師總結的SI方面的精華,給大家分享一下

2011-11-30 11:32:55 3108

3108 信號完整性工程師_SI工程師前景分析

2011-11-30 11:37:13 9886

9886 電子發燒友網為你提供這9大招信號完整性工程師必須掌握資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-07 08:55:50 17

17 DK-SI-5SGXEA7N信號完整性套件原理圖

2021-04-29 15:46:15 3

3 DK-SI-5SGXEA7N信號完整性套件BOM

2021-05-10 10:18:10 3

3 DK-SI-5SGTMC7N信號完整性套件BOM

2021-05-13 15:22:48 2

2 DK-SI-5SGTMC7N信號完整性套件原理圖

2021-05-24 11:19:49 2

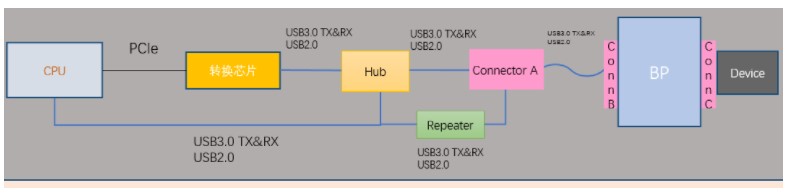

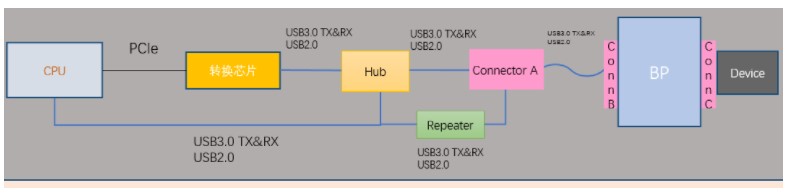

2 需要信號完整性工程師評估USB 接口擺放位置是否符合。是否符合取決于鏈路的情況,也就是鏈路評估。

2022-08-15 09:27:16 2163

2163

定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2022-11-16 14:56:00 1778

1778

電子發燒友App

電子發燒友App

評論