本文主要詳解PCI總線與PXI總線有什么區別,首先介紹了PCI 總線結構圖、特點及PCI總線性能,其次闡述了PXI總線的特性,最后介紹了PCI總線與PXI總線的區別。

2018-05-24 09:15:23 13958

13958

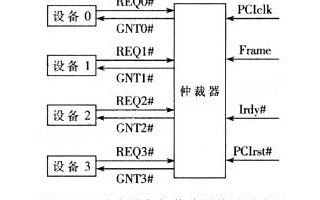

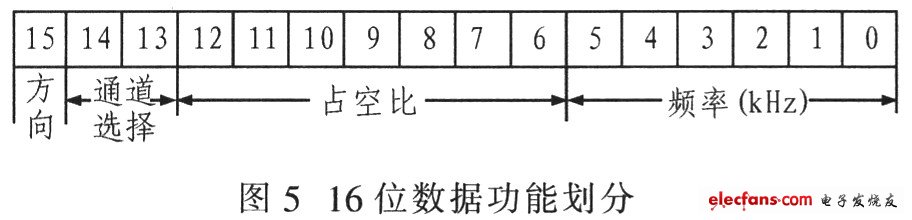

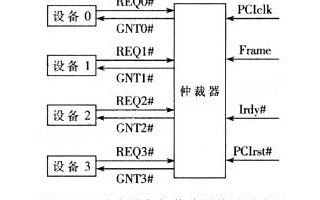

,為了使PCI設備能夠更方便地應用在嵌入式系統中,本文介紹了一種基于CPLD(復雜可編程邏輯器件)的PCI總線仲裁器的設計方法,此方法可以為系統量身定制適合于系統本身的PCI總線仲裁器。而不必局限于特定的芯片要求,在體積、功能、成本等諸多方面都有很好的應用前景。

2020-06-26 09:30:00 928

928

PCIe總線是繼承了PCI總線而設計而來的,理解PCIe總線先從學習PCI的知識切入。PCI(Peripheral ComponentInterconnect)總線的誕生與 PC(Personal

2022-09-08 14:26:30 4173

4173 或I/O映射可直接使PCI總線與ISA總線相連,從而將ISA總線快速地轉換到PCI總線上。在我們的數控測井系統中,原來的通信控制模塊是基于ISA總線的插件,端口地址為0X100~0X10F,總線

2018-12-17 11:23:00

PCI總線PCB布線有什么要求嗎?

2015-10-23 15:46:31

9050支持突發存儲器映射和I/O映射方式在PCI總線和局部總線存取數據。雙向FIFO可以用于零等待狀態突發操作。PCI總線總是工作在突發方式,局部總線可以設置成突發方式或者連續單周期方式。 (2)產生中

2018-11-29 14:52:52

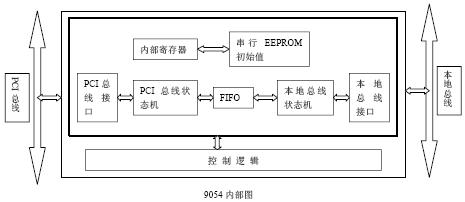

字節。在配置存儲器中存放了廠家標志、設備標志以及本地總線的基地址空間、I/O空間和中斷控制信號等信息。初始化時,系統自動將串行EEPROM中的配置參數裝入PCI配置寄存器,并根據本地總線對內存、I/O

2018-12-05 10:12:42

,PCI9054既是PCI總線的主控器又是Local總線的主控器。Scatter/Gather DMA要求主機在PCI空間或Local空間設定Descriptor模塊,模塊包括PCI和Local的起始地址、傳輸

2008-10-09 11:23:38

的數據奇偶錯,以及其他可能引起災難性后果的系統錯誤。它可由任何設備發出。6.中斷信號 在PCI總線中,中斷是可選項,不一定必須具有。 INTA# O/D:用于請求中斷。 INTB# O/D

2012-04-06 14:37:24

PCI總線特點是什么?PCI接口開發現狀如何?如何去設計PCI接口?

2021-04-29 07:09:04

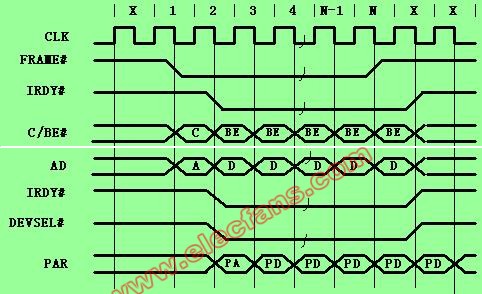

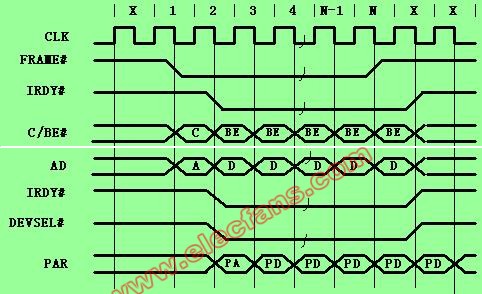

不同于ISA總線,PCI總線的地址總線與數據總線是分時復用的。這樣做的好處是,一方面可以節省接插件的管腳數,另一方面便于實現突發數據傳輸。在做數據傳輸時,由一個PCI設備做發起者(主控

2019-10-16 09:02:10

PCI總線的信號定義PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數據信號、控制信號、仲裁信號、中斷信號...

2022-02-16 06:48:12

最近用PCI9052、IDT7025,DSP2812設計PCI總線,看了很多論文也找不出好的設計方案,希望各位指導一下。特別是電平轉換,主從選擇、防沖突、高速通信。。。謝謝各位了。

2012-05-13 19:45:44

PCI總線鎖定上傳視頻本詞條由“科普中國”科學百科詞條編寫與應用工作項目 審核 。PCI是Peripheral Component Interconnect(外設部件互連標準)的縮寫,它是目前

2021-11-24 07:20:59

最近在研究總線擴展IO口,查了很多資料都查不到實現的原理,都是各種介紹PCI協議或者引腳的,我想了很久說下我的猜測希望有知道的人幫我指點一下,對于32位的的PCI總線,總線里面AD0到AD31分成4

2017-01-17 18:43:47

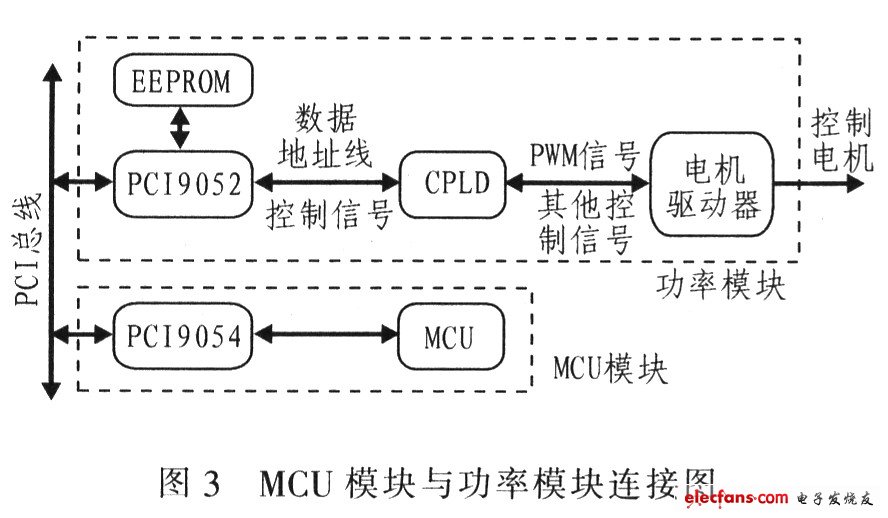

引言 8位單片機在嵌入式系統中應用廣泛,然而讓它直接與PCI總線設備打交道卻有其固有缺陷。8位單片機只有16位地址線,8位數據端口,而PCI總線2.0規范中,除了有32位地址數據復用AD[3~0]外

2019-04-24 07:00:09

cpld與8051的總線接口vhdl設計源碼cpld 與8051的總線接口VHDL源碼關于cpldbus51.VHD的說明: 很久之前我也想在網上找一份cpld與8051的總線方式接口的VHD源碼

2012-08-10 18:56:47

pci總線的含義是什么90年代,隨著圖形處理技術和多媒體技術的廣泛應用,在以Windows為代表的圖形用戶接口(GUI)進入PC機之后,要求有高速的圖形描繪能力和I/O處理能力。這不僅要求圖形適配卡

2008-12-09 13:46:13

CPLD技術在PCI總線開關中的應用使用CPLD技術開發PCI板卡有什么優點

2021-04-08 06:47:28

DSP通信驅動程序主要模塊的設計方法和編程注意要點。 1 硬件設計1.1 PCI總線控制芯片PCI2040 PCI總線是一種不依附于某個具體處理器的局部總線,它支持32位或64位的總線寬度,頻率

2019-09-24 22:18:02

基于CPLD的系統中I2C總線的設計

2012-08-17 11:17:28

。 1 PCI接口的實現 在PCI總線適配卡的設計中,采用專用的PCI接口芯片來實現PCI接口,設計者不需要將精力投入到復雜的PCI接口功能設計和驗證測試上。專用的接口芯片可以實現完整的PCI主控

2009-04-20 10:51:10

校驗值送給奇偶校驗模塊。數據通道為PCI訪問配置空間和用戶設備提供了一個地址和數據接口。2.5 奇偶校驗奇偶校驗主要用來確定主設備是否成功的尋址到它希望的目標設備,以及數據傳輸的正確與否,在總線交易中

2019-05-29 05:00:02

。HPI寄存器的選擇由HCNTL[1:0]腳在PCI總線地址有效期實現,說明如表1所示:在主機訪問DSP片內RAM過程中,主機首先根據訪問類型對HPIC寄存器進行初始化操作,然后再對HPIA寄存器進行操作

2018-12-17 11:29:06

基于FPGA的PCI總線接口設計

2017-09-30 09:12:46

基于FPGA的PCI總線接口設計

2020-03-15 11:43:10

PCI核的功能則相對較弱。 根據VoIP、CDMA等先進的通訊系統對PCI總線接口的實際需求,我們通過評估比較,決定采用Altera公司的64位66MHz PCI Core,在VERIBEST

2019-04-17 07:00:06

PCI核的功能則相對較弱。 根據VoIP、CDMA等先進的通訊系統對PCI總線接口的實際需求,我們通過評估比較,決定采用Altera公司的64位66MHz PCI Core,在VERIBEST

2019-04-12 07:00:11

PCI總線接口主要是使用兩種方式:(1)采用專用接口芯片,如AMCC公司的S5933和PLX公司的9054、9080。使用接口芯片開發人員可以不考慮PCI接口的實現問題,但是在實際應用中通常只用到接口芯片

2018-12-04 10:35:21

一種可行的方案就是利用CPLD作為溝通單片機與PCI設備間的橋梁,充分利用CPLD中I/O資源豐富,用戶可自定制邏輯的優勢,來幫助單片機完成與PCI設備間的通信任務。

2021-04-29 06:28:43

一種可行的方案就是利用CPLD作為溝通單片機與PCI設備間的橋梁,充分利用CPLD中I/O資源豐富、用戶可自定制邏輯的優勢,來幫助單片機完成與PCI設備間的通信任務。

2021-04-30 06:59:19

PCI總線是什么?有什么特點?如何利用FPGA去設計PCI總線的接口電路?設計PCI總線接口時應注意哪些問題?

2021-05-31 06:37:24

什么是PCI總線?它有什么特點?如何利用FPGA設計PCI總線的接口電路?設計PCI總線接口時應注意哪些問題?

2021-04-29 06:10:31

如何去采用PCI9030芯片實現從ISA總線到PCI總線的轉接卡的設計?有哪些方法?其過程是怎樣的?

2021-07-01 08:00:36

BGA 封裝,本地總線可以設置為 8 位、16 位、32 位復用和非復用模式。在我們原來的性能測試系統中,功率計模塊是基于ISA總線的插件,端口地址是ox100-ox107,數據總線寬度是8位,具有

2019-05-05 09:29:33

PCI總線特點及開發現狀PCI接口配置空間的實現求一款在PCI總線上利用FPGA技術設計PCI總線接口的設計方案

2021-04-15 06:17:20

PCI總線的中斷機制PCI總線使用INTA#、INTB#、INTC#和INTD#信號向處理器發出中斷請求。這些中斷請求信號為低電平有效,并與處理器的中斷控制器連接。在PCI體系結構中,這些...

2022-02-16 06:31:43

DN155- 熱插拔PCI總線

2019-05-28 12:21:24

設計應用中有很大的局限性。因此,使用通用型CPLD器件設計簡易型PCI接口有很大的現實意義。在Compact接口的CPLD設計中,筆者根據PCI總線傳輸時序來進行狀態機構造,并使用VHDL語言進行功能

2019-06-17 05:00:11

PCI9030是什么?PCI9030主要有哪些特點?設計PCI總線接口有哪些步驟流程?

2021-04-15 06:57:46

送給奇偶校驗模塊。數據通道為PCI訪問配置空間和用戶設備提供了一個地址和數據接口。2.5 奇偶校驗奇偶校驗主要用來確定主設備是否成功的尋址到它希望的目標設備,以及數據傳輸的正確與否,在總線交易中,任何

2019-06-20 05:00:03

采用PCI總線流水式高速數據采集系統設計摘要:目前基于PCI總線的高速數據采集系統,大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能

2009-10-30 15:09:49

的是PCI總線。PCI(Peripheral Component Interconnect)是一種由NI公司于1997年發布的基于計算機測量和自動化平臺的一種全新的開放性、模塊化儀器總線規范。PCI

2019-05-30 05:00:02

總線規范相同,而配置空間是PCI所特有的。配置空間使系統處理器能夠枚舉PCI總線上的各種設備,并根據設備要求自動配置存儲器和I/O的地址空間。操作系統在自檢的過程中檢測所有PCI設備,讀取設備的配置

2019-04-29 07:00:09

PCI總線漸漸地取代了ISA總線。它有許多優點,比如即插即用(Plug and Play)、中斷共享等。在這里我們對PCI總線做一個深入的介紹。 從數據寬度上看,PCI總線有32bit、64bi

2008-06-16 14:24:07 147

147 基于CPLD的系統中I2C總線的設計 摘要: 在介紹I2C總線協議的基礎上,討論了基于CPLD的系統中I2C總線的設計技術,并結合工程實例設計了I2C總線IP核,

2008-08-13 13:43:38 31

31 pci總線協議:

This document contains the formal specifications of the protocol, electrical

2008-12-09 14:00:29 36

36 目前基于PCI總線的高速數據采集系統,大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能很好地發揮PCI總線的性能。針對這些不足,在分析

2009-03-16 18:02:05 10

10 介紹 PCI 總線的特點,對現有的 PCI 總線的接口設計方法進行分析;介紹 PCI 接口芯片CY7C09449PV的結構及其與數字信號處理器TMS320C32之間接口電路的設計,提出一種基于PCI和 C32的數據

2009-04-08 09:53:42 26

26 詳細闡述一種利用CPLD 實現的8 位單片機與PCI 設備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實踐中檢驗通過。

2009-04-14 17:32:19 34

34 采用可編程邏輯器件CPLD,分四個模塊——控制寄存器模塊、PCI控制器狀態機模塊、SRAM 控制器模塊和仲裁器模塊,分別完成通信并解析PCI總線、PCI狀態的控制和翻轉、負責SRAM接口數

2009-06-01 14:25:22 16

16 基于FPGA的PCI總線接口設計::PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接

2009-06-25 08:17:18 48

48 PCI總線傳輸的終止方式探析:探討了PCI 總線傳輸的終止方式。PCI 總線的主設備和目標設備都可以終止PCI 傳輸。主設備和目標設備在終止一次傳輸的同時還以信號的電平組合告知主

2009-06-28 19:32:07 22

22 本文在結合嵌入式實時操作系統VxWorks 和PCI總線的特點的基礎上,介紹了PCI總線驅動設計的過程,并從充分應用VxWorks 卓越的實時性和PCI總線靈活的擴展性的角度出發,給出了有一定

2009-08-10 09:02:36 24

24 本文簡要介紹了PCI 總線的仲裁機制, 完成了PCI 總線仲裁器核心的設計、實現。通過ModelSim 進行了軟件仿真,最后在XILINX 公司的FPGA 上加以了驗證。

2009-09-03 08:18:29 27

27 本文在PCI2.2 總線規范的基礎上,給出了一種PCI 總線目標控制器的設計方案。重點從控制邏輯和數據通路的建立上闡述了目標控制器的設計:用狀態機實現總線訪問操作的復雜時

2009-12-12 16:58:25 33

33 由高速圖像采集子系統和GPS 精密授時子系統構成,為圖像采集提供精確的時間基準。設計并實現了基于PCI 總線的GPS 時間獲取板卡,并完成了一系列軟件的設計開發。首先通過CPLD

2009-12-19 14:01:07 21

21 本文重點分析了PCI 總線設備控制器的設計方案。以PCI 總線協議的分析和理解為基礎,對PCI 總線設備控制器進行了功能分析和結構劃分,對PCI 總線從設備控制器的設計思路和各個

2010-01-13 16:57:37 49

49 PCI局部總線 BIOS 規范

2010-07-31 17:57:06 33

33 詳細介紹了PCI9052接口器件的功能、結構和使用方法,并結合實際給出了基于PCI9052器件開發PCI總線接口卡的應用實例。

Abstract:

The main functions,structu

2010-12-25 16:19:14 61

61 摘 要: 本文采用Altera的CPLD實現了PCI總線至UTOPIA接口的邏輯轉換控制,為低成本實現ATM終端奠定了基礎。

2006-03-11 13:16:50 864

864

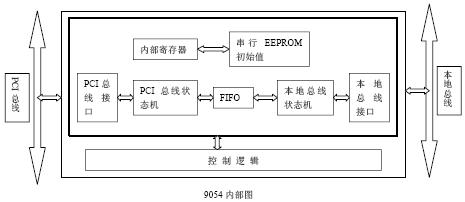

PCI總線接口芯片PCI9054及其應用PCI9054是PLX公司推出的一種PCI主模式橋芯片。本文主要介紹了它的特性、功能及應用,說明了以PC

2008-10-09 11:18:03 7642

7642

PCI總線原理

PCI總線的特點:數據總線32位,可擴充到64位。可進行突發(burst)式傳輸。總線操作與處

2008-12-09 11:30:05 13510

13510

PCI總線定義

PCI 是 Peripheral Component Interconnect 的縮寫。接口卡的外觀:PCI 標準 32位/64位 接口卡

2009-02-12 10:37:58 1455

1455

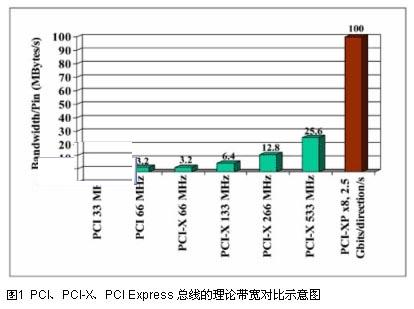

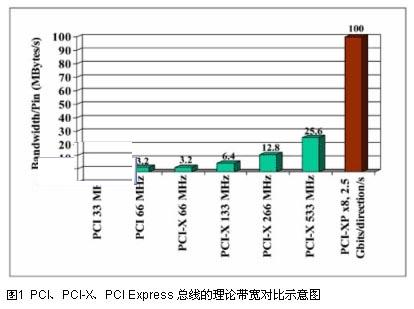

儀器控制總線比較(GPIB、USB、PCI、PCI Express和以太網/LAN/LXI)

GPIB 我們研究的第一個總線是IEEE 488總線,較為熟悉的稱謂是GPIB(通用接口總

2009-02-26 00:06:42 8599

8599 摘 要 :PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接口的

2009-06-20 13:13:28 936

936

摘要:詳細闡述一種利用CPLD實現的8位單片機與PCI設備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實踐中檢驗通過。

關鍵詞:單片機 CPLD PCI

8位單片

2009-06-20 13:31:29 869

869

摘 要: 以自行研制開發的PCI高速總線背板為背景,系統地論述了PCI總線的仲裁機制、總線的缺省占用、仲裁信號協定及優先級仲裁算法,給出了采用EPLD實現仲裁器功能的編程設計

2009-06-20 13:32:20 961

961

基于CPLD的單片機與PCI接口設計解決方案

8位單片機在嵌入式系統中應用廣泛,然而讓它直接與PCI總線設備打交道卻有其固有缺陷。8位單片機只有16位

2009-09-26 17:41:20 825

825

PCI Express總線技術白皮書

1.1 PCI Express總線的起源和現狀 2001年春季的IDF上Intel正式公布PCI Express,是取代PCI總線的第三代IO技術,也稱為

2009-10-04 09:39:14 1031

1031

一種基于CPLD的單片機與PCI接口設計方案

0 引言

8位單片機在嵌入式系統中應用廣泛,然而讓它直接與PCI總線設備打交道卻有其固有缺陷。8

2009-11-12 09:56:50 582

582 PCI Express總線

其實,PCI Express是一個計算機系統總線的名稱,不過大家聽得最多的還是“接口”這個詞,也沒錯,PCI Express的確是下一

2010-01-22 11:21:51 627

627 PCI總線目標接口芯片PCI9052及其應用

摘要:PCI9052是PLX公司繼PCI9050之后新推出的一種低成本的PCI總線目標接口芯片,它傳輸速率高,數據吞吐量大,

2010-03-03 19:21:58 2492

2492

提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設計方案,并給出了PCI總線接口芯片

2011-01-07 12:13:03 1891

1891

為了實現把軟件仿真的數據通過PCI總線DMA傳輸、處理后轉換成高速視頻串行數據流(LVDS數據流),設計出了基于PCI9054的數據轉換模塊。通過介紹PCI總線接口協議芯片PCI9054的性能、特點,分析了windows的WDM驅動程序的特點,在軟硬件設計中采用把數據緩存器設

2011-01-14 17:32:07 50

50 探討了PCI 總線傳輸的終止方式。PCI 總線的主設備和目標設備都可以終止PCI 傳輸。主設備和目標設備在終止一次傳輸的同時還以信號的電平組合告知主設備其不同的終止狀態。主設備啟

2011-05-18 16:43:46 28

28 PCI總線 作為計算機與外部設備的一個重要連接總線,數據傳輸穩定、靈活、傳輸速度快,還具有即插即用和良好的擴展性等優點,被廣泛應用在各種與計算機互聯的設備中。 考慮到P

2011-06-21 16:38:10 50

50 出了一種PCI總線從設備的CPLD實現方法。該方法遵從PCI規范2.2版,實現了資源自動配置并且支持數據突發傳輸。試驗證明該方法的有效性,其突發傳輸速率可達20 MBs -1 。

2011-11-30 17:06:11 60

60 本文將對PLX公司的PCI9052總線目標接口芯片的功能及其在PCI板卡設計中的應用進行介紹,PCI9052是PLX公司繼PCI9050之后新推出的、可用于低成本適配器的總線目標接口芯片。

2011-12-29 09:42:51 3083

3083

文中主要介紹了采用CPLD實現32 bit 33 MHzPCI從設備接口的設計方法,該從設備接口模塊遵從PCI規范2.2版,實現了資源的自動配置,支持突發傳輸,并為用戶提供了一個簡單的接口。設計完成

2012-08-06 15:18:22 1788

1788

基于CPLD的SGPIO總線實現及應用

2017-01-24 16:00:51 75

75 PCI總線的應用資料

2017-10-31 09:10:56 9

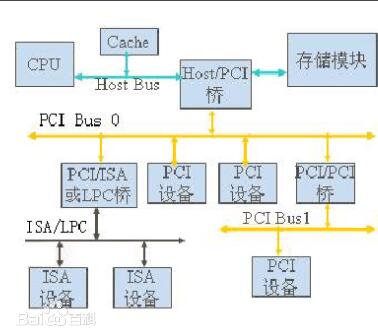

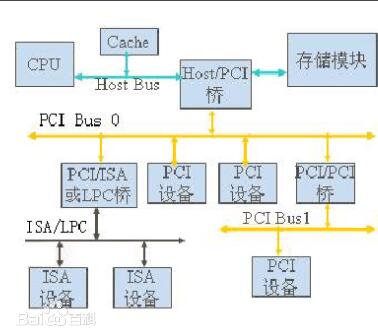

9 PCI總線是一種樹型結構,并且獨立于CPU總線,可以和CPU總線并行操作。PCI總線上可以掛接PCI設備和PCI橋片,PCI總線上只允許有一個PCI主設備,其他的均為PCI 從設備,而且讀寫操作只能在主從設備之間進行,從設備之間的數據交換需要通過主設備中轉。

2018-06-07 15:02:00 3581

3581

PCI(PeripheralCompornentInterconnect,即外圍部件互連)總線是一種先進的高性能32/64位地址數據復用局部總線,該總線是以INTEL為首的多家集團設計的,PCI

2018-08-11 11:35:00 14447

14447 PCI9052是PLX技術公司繼PCI9050之后推出的低成本、低功耗、高性能總線接口芯片,通過該芯片可以使多種局部總線快速轉換到PCI總線上。

2019-10-22 16:46:53 3510

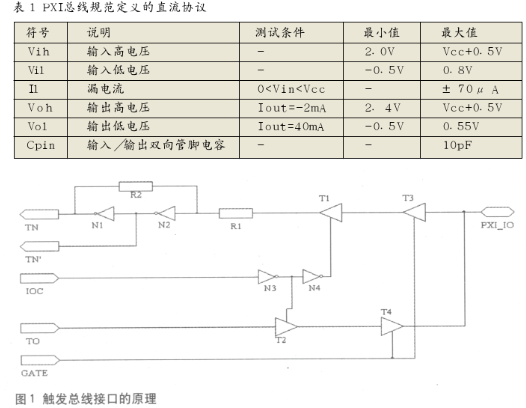

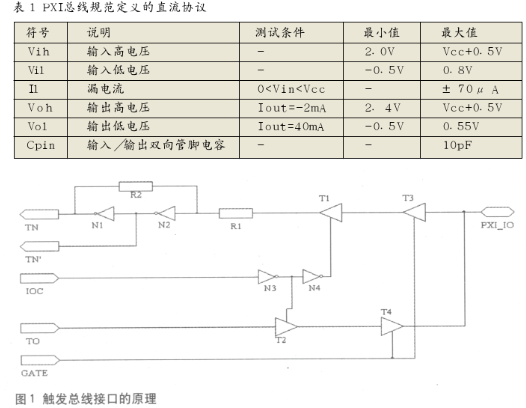

3510 pxi是pci extensiON for inSTrumentation的縮寫,是為了將pci總線擴展到測試儀器領域而推出的以pci計算機局部總線為基礎的模塊儀器結構。pxi相對于cpci系統的一個重要特點是定義了8根觸發總線,這可以實現系統中各模塊間的同步和通信。

2020-04-04 10:36:00 1557

1557

PCI總線的信號定義 PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數據信號、控制信號、仲裁信號、中斷信號等多種

2021-07-18 09:55:32 1981

1981 PCI總線的存儲器讀寫總線事務 總線的基本任務是實現數據傳送,將一組數據從一個設備傳送到另一個設備,當然總線也可以將一個設備的數據廣播到多個設備。在處理器系統中,這些數據傳送都要依賴一定的規則

2021-07-18 10:06:12 2274

2274 PCI總線的中斷機制 PCI總線使用INTA#、INTB#、INTC#和INTD#信號向處理器發出中斷請求。這些中斷請求信號為低電平有效,并與處理器的中斷控制器連接。在PCI體系結構中,這些中斷信號

2021-07-18 10:10:40 2450

2450 PCI總線協議非常復雜,目前實現PCI接口的有效方案分為兩種:即使用可編程邏輯器件和使用專用總線接口的器件,可編程邏輯器件實現PCI接口比較靈活,可以利用的器件比較多,現在有許多生產可編程邏輯器件的廠商(如Xilinx的Logicore和Alerra的AMPP)都提供經過嚴格測試的PCI接口功能模塊

2023-08-01 14:37:19 553

553 怎樣把PCI總線速度鎖定? PCI總線速度鎖定是指限制PCI總線傳輸速度的方法。當系統中出現某些硬件兼容性問題或者不穩定性問題時,鎖定PCI總線速度可能是一個有效的解決方案。在本文中,我們將詳細介紹

2023-09-02 15:12:39 1194

1194

電子發燒友App

電子發燒友App

評論