電子發(fā)燒友網(wǎng)訊 :Arria V GZ拓展了Altera中端FPGA系列,滿足廣播和通信系統(tǒng)日益增長的帶寬需求。隨著Arria V GZ型號的推出,進(jìn)一步拓展了公司的28 nm系列產(chǎn)品。 Altera公司 (NASDAQ: ALTR)

2012-10-16 12:53:18 1298

1298 近日,***進(jìn)一步削減其2013年上網(wǎng)電價(jià)補(bǔ)貼,削減幅度為9.23%至11.88%,而同時(shí)將其太陽能發(fā)電裝機(jī)容量目標(biāo)提高30%。 據(jù)***媒體報(bào)道,***經(jīng)濟(jì)部能源局(BureauofEnergy

2012-12-04 19:50:52

的描述,進(jìn)程和函數(shù)的應(yīng)用。一步一步的講解設(shè)計(jì)過程中的每個(gè)語句和注意事項(xiàng),同時(shí)包括編寫后如何查找和修改錯(cuò)誤。教程介紹:第一講:主要講解CPLD 系統(tǒng)開發(fā)的基本概念,介紹了CPLD 和FPGA 的各自特點(diǎn)

2020-05-14 14:50:30

ALTERA器件選型手冊目錄 1、 MAX7000系列器件 ………………………………………………………………………………………….1 2、 MAX3000A系列器件

2012-08-10 18:24:17

Altera FPGA/CPLD設(shè)計(jì)與Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程從網(wǎng)上找到了一些Altera FPGA/CPLD經(jīng)典教材,包含夏宇聞老師的Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版)Altera FPGA/CPLD設(shè)計(jì)與Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程

2014-02-17 09:22:18

、MAX7000 系列、Mercury、FELX10KE、APEX20KE、APEX20KC、ACEX1K、APEX II和 Stratix 等。 其開發(fā)工具 MAX+PLUS II 是較成功

2019-03-04 14:10:13

Max+plusⅡ是Altera公司提供的FPGA/CPLD開發(fā)集成環(huán)境,Altera是世界上最大可編程邏輯器件的供應(yīng)商之一。Max+plusⅡ界面友好,使用便捷,被譽(yù)為業(yè)界最易用易學(xué)的EDA軟件

2009-10-09 17:14:29

一步一步教你使用uCOS-II組合

2013-08-27 18:01:31

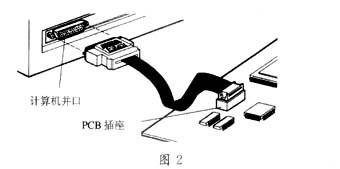

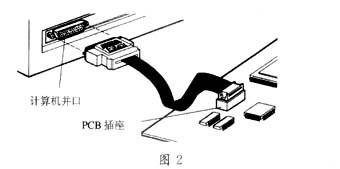

及設(shè)備用電安全的需要,更進(jìn)一步提高電源的可靠性,及時(shí)發(fā)現(xiàn)供電隱患,提高設(shè)備的運(yùn)行壽命,對電源進(jìn)行在線管理已經(jīng)成為普遍的需求。針對早期的UPS電源的RS232標(biāo)準(zhǔn),已經(jīng)無法滿足目前計(jì)算機(jī)硬件及軟件技...

2021-12-28 08:05:27

進(jìn)一步理解量子力學(xué)經(jīng)典理論與應(yīng)用 多方面豐富相關(guān)圖表為了進(jìn)一步深入理解量子力學(xué)理論經(jīng)典及其應(yīng)用,從多個(gè)方面豐富內(nèi)容,附圖頁碼一致,符合國際標(biāo)準(zhǔn)。聲學(xué),聲波自然現(xiàn)象,以及經(jīng)典原子理論的應(yīng)用等對理解量子力學(xué)經(jīng)典之波的概念有益。大灣區(qū)2020-8-2

2020-08-02 07:05:50

讓我們進(jìn)一步聆聽大師對量子力學(xué)歸屬的現(xiàn)代物理的解說,及其常用圖表iii(待續(xù)3)“現(xiàn)代物理”術(shù)語通常指的是二十世紀(jì)物理學(xué)快速的概念發(fā)展。相對的,在1900年之前艱辛地發(fā)明的所有的物理學(xué)都標(biāo)記

2020-06-28 17:48:16

已經(jīng)在友好的ARM中開發(fā)了android布局,以顯示M24LR內(nèi)存中的溫度和消息。我想知道如何進(jìn)一步開發(fā)工作應(yīng)用程序。 是CR95HF DLL文件有幫助嗎。 我們檢查了PC軟件,NFC& amp;的可用代碼。數(shù)據(jù)記錄器應(yīng)用程序。#software#raspberry-pi#cr95hf

2019-08-22 11:10:49

適合對C語言有一定基礎(chǔ)積累的童鞋 想進(jìn)一步學(xué)習(xí)C語言的 可以看哈

2012-09-10 22:26:29

專家:1、這個(gè)指標(biāo)的紋波是否在設(shè)計(jì)許可的范圍之內(nèi)?在一般情況下,DC-DC電源轉(zhuǎn)換的紋波在一個(gè)什么范圍內(nèi)可以認(rèn)為是正常的?2、從原理圖上,pcb圖上,這個(gè)設(shè)計(jì)是否還能夠進(jìn)一步優(yōu)化降低紋波?還請指出。

2014-10-28 15:59:25

你好E4406A有問題----當(dāng)我啟動(dòng)時(shí) - 設(shè)備按我的意愿啟動(dòng)自動(dòng)對齊,但是當(dāng)它達(dá)到adc對齊時(shí)它不會(huì)更進(jìn)一步。根本沒有消息。可以用abort終止它,并且分析儀似乎正常工作---- ??我可以用

2018-12-28 16:06:57

我有一個(gè)設(shè)計(jì),生成一堆以下消息:錯(cuò)誤:包:1107- 包無法將下面列出的符號組合成單個(gè)IOB組件,因?yàn)樗x的站點(diǎn)類型不兼容。但他們沒有進(jìn)一步的信息說明哪些符號。我還有一堆尚未連接的符號。是否由于斷開

2018-10-15 11:45:18

FPGA與CPLD的辨別和分類主要是根據(jù)其結(jié)構(gòu)特點(diǎn)和工作原理。通常的分類方法是:將以乘積項(xiàng)結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

您以最高效的方式達(dá)到設(shè)計(jì)目的,前所未有的提高了設(shè)計(jì)效能。 采用Quartus II軟件v13.1,編譯時(shí)間平均縮短了30%,對于小規(guī)模設(shè)計(jì)改動(dòng),又進(jìn)一步平均縮短了50%,更快的完成設(shè)計(jì)修改,產(chǎn)品更迅速

2013-11-13 15:34:26

的大部分功能,以及設(shè)計(jì)Altera最新CPLD和低成本FPGA系列所需的一切。Quartus II網(wǎng)絡(luò)版軟件還支持Altera高密度系列中的入門級產(chǎn)品。Quartus II訂購版軟件提供:支持所有

2012-08-15 12:30:03

SOP位移傳感器防水功能將進(jìn)一步提高位移傳感器應(yīng)用的行業(yè)越來越廣,使用的環(huán)境也是各種各樣,SOP位移傳感器有些系列可以適用于潮濕、油污、灰塵等各種惡劣環(huán)境,但是有好些客戶問咱們的位移傳感器防水

2019-08-20 16:40:48

有什么方法可以進(jìn)一步降低待機(jī)模式的功耗

2023-10-12 07:23:28

你好,我有一個(gè)小問題。我使用100m時(shí)鐘芯片。每個(gè)時(shí)鐘只有10ns,ad9106寄存器的最小輸出波形只有100Hz。如何將波形頻率設(shè)置為進(jìn)一步降低到10Hz?我已將配置設(shè)置為相關(guān)寄存器的最大值。拍

2023-12-01 06:12:19

imx_pll1416x_tbl 還報(bào)告了額外的時(shí)鐘頻率。

是否可以在 opp-table 中引入這些額外的頻率以進(jìn)一步降低時(shí)鐘頻率?

如果是,哪些值應(yīng)該用于屬性 opp-microvolts、opp-supported-hw、clock-latency-ns?

2023-04-23 11:14:12

各位大俠,小弟CPLD/FPGA新手,遇到燒錄不保存問題,詳細(xì)描述如下:芯片型號:Altera MAX V 5M160ZE64Quartus版本:Quartus II 14.1問題描述:1

2015-07-21 10:40:23

借這個(gè)機(jī)會(huì),申請這塊開發(fā)版,便于日常學(xué)習(xí),而且我即將大四了,希望用這塊開發(fā)版能更進(jìn)一步的學(xué)習(xí),一則方便之后的課設(shè),二則便于找工作,三則嵌入式也是自己敢興趣。衷心希望能獲得這次機(jī)會(huì),謝謝。項(xiàng)目描述:之前

2015-06-24 17:06:36

【OK210試用體驗(yàn)】u-boot篇 -- u-boot進(jìn)一步定制 從u-boot單板的自定義,到SPL的移植,都還沒有完全定制出自己的S5PV210單板信息,還是摻雜著S5PC100

2015-09-07 11:38:52

項(xiàng)目名稱:進(jìn)一步深入學(xué)習(xí)紫外線的檢測試用計(jì)劃:我以前自己動(dòng)手做過紫外線的檢測傳感器,可是制作出來的傳感器受干擾十分嚴(yán)重,通過光譜分析之后發(fā)現(xiàn),是因?yàn)槲宜x用的濾光片達(dá)不到要求性能。所以一直想找個(gè)機(jī)會(huì)重新學(xué)習(xí)一下,對紫外線的檢測原理。細(xì)致的完成整個(gè)系統(tǒng)的分析,進(jìn)而吸收這個(gè)板子所含的學(xué)問。謝謝。

2017-04-10 15:41:43

、采用查找表的FPGA的工作原理第三節(jié) Altera系列CPLD介紹一、MAX7000系列器件簡介二、MAX7000系列器件的結(jié)構(gòu)三、MAX7000系列器件功能描述第四節(jié) Xilinx系列CPLD介紹······下載鏈接:`

2018-03-30 15:07:50

項(xiàng)目名稱:進(jìn)行進(jìn)一步學(xué)習(xí)和研究試用計(jì)劃:此前一直從事單片機(jī)開發(fā),想進(jìn)一步深入學(xué)習(xí)各種MCU,看到有此活動(dòng),特來申請。也為下一步項(xiàng)目無人機(jī)攝像頭驅(qū)動(dòng)選擇合適的芯片。

2020-04-23 10:36:17

【單片機(jī)開發(fā)300問】怎樣進(jìn)一步降低功耗功耗,在電池供電的儀器儀表中是一個(gè)重要的考慮因素。PIC16C××系列單片機(jī)本身的功耗較低(在5V,4MHz振蕩頻率時(shí)工作電流小于2mA)。為進(jìn)一步降低

2011-12-07 13:59:56

初學(xué)linux,安裝了Ubuntu系統(tǒng)界面,請教該如何進(jìn)一步快速學(xué)習(xí),大家有什么好的初學(xué)的資料分享一下,謝謝啦

2015-08-24 18:39:29

初學(xué)者除了學(xué)好書本上的基本知識(shí)外,如何能進(jìn)一步學(xué)習(xí)Protel

2017-03-03 09:19:29

替代品的需求日益高漲。那么,首先簡單介紹一下疊層陶瓷電容器的結(jié)構(gòu)。如圖所示,涂有粉狀陶瓷材料的片狀電介質(zhì)與電極組成重疊交替的結(jié)構(gòu)。為使大家進(jìn)一步了解結(jié)構(gòu)與靜電電容的關(guān)系,使用以下公式來說明。從公式中可以

2018-12-03 14:35:18

,具有很強(qiáng)的實(shí)用價(jià)值。如果再結(jié)合其他濾波預(yù)處理方法,則可以進(jìn)一步提高其濾除噪聲的能力,更好地改善圖像質(zhì)量。

2021-04-23 06:00:55

(使用FPGA引腳和DAC)任何人都可以給出一些答案如何進(jìn)一步使用以上兩個(gè)文件查看DSO上的輸出 提前感謝你Counter.v 3 KB以上來自于谷歌翻譯以下為原文Hello to all

2019-07-03 08:41:24

各位大俠好,最近公司要求將CC2640R2模塊的功耗進(jìn)一步縮減,我應(yīng)公司要求做了一個(gè)最簡電路,目前外圍電阻、電位器、LED等繁雜的元件已盡數(shù)砍掉,現(xiàn)在測量出僅中心的綠板CC2640R2模塊待機(jī)功耗在

2019-10-21 10:02:32

如何進(jìn)一步加強(qiáng)對RFID的安全隱私保護(hù)?

2021-05-26 06:09:27

時(shí)間為9:00到11:00),也可以刷卡打開閘機(jī)。閘機(jī)配有發(fā)卡器和讀卡器。請問附件中的通訊協(xié)議是屬于TCP/IP協(xié)議嗎?如果方便遠(yuǎn)端的計(jì)算機(jī)控制閘機(jī),是不是要進(jìn)一步封裝附件中的通訊協(xié)議呢?例如,建立一個(gè)

2017-12-08 00:26:24

GN1302 晶振引腳連接 2 個(gè) 30pf 電容,每天大約慢 4 秒,如何進(jìn)一步提高精度?時(shí)鐘每天慢 4 秒是因?yàn)榫д竦耐獠控?fù)載電容過大,即 30pf 電容過大。如果使用的晶振的負(fù)載電容參數(shù)為

2022-12-29 17:36:43

一、引言內(nèi)存是嵌入式系統(tǒng)中的關(guān)鍵資源,內(nèi)存占用主要是指軟件系統(tǒng)的內(nèi)存使用情況。本篇博客將介紹如何分析內(nèi)存使用以便進(jìn)行進(jìn)一步優(yōu)化內(nèi)存占用相關(guān)的基礎(chǔ)概念和相關(guān)工具。二、內(nèi)存占用內(nèi)存占用是應(yīng)用程序運(yùn)行時(shí)

2021-12-15 06:05:33

本設(shè)計(jì)實(shí)例進(jìn)一步拓展了以前將步進(jìn)電機(jī)驅(qū)動(dòng)器集成到CPLD中的設(shè)計(jì)。

2021-05-06 07:01:05

如何讓計(jì)算機(jī)視覺更進(jìn)一步接近人類視覺?

2021-06-01 06:27:08

傳感器為震動(dòng)速度傳感器,待提取信號頻率0.1~200Hz ,幅度幾十uV,原來采用AD620放大,現(xiàn)在希望進(jìn)一步降低功耗與噪聲,采用什么片子好?

2018-10-25 09:25:24

常見的電流測量方法有哪些,其各自的優(yōu)點(diǎn)是什么?如何解決電流檢測難題?如何進(jìn)一步了解現(xiàn)代電流檢測放大器?

2021-04-08 06:51:41

網(wǎng)絡(luò)時(shí)間協(xié)議NTP是什么意思?NTP授時(shí)的原理是什么?怎樣去進(jìn)一步提高NTP的授時(shí)精度呢?

2021-11-01 07:12:40

、電視手機(jī)。這些采用多種RF技 術(shù)的手機(jī)在提供便利的同時(shí)也使得手機(jī)的設(shè)計(jì)變得復(fù)雜,如何進(jìn)一步集成射頻元件也變得至關(guān)重要。

2019-08-27 08:33:19

怎樣一步一步去建立STM32工程呢?其過程是怎樣的?

2021-10-28 08:53:27

級放大再加給AD7714時(shí),測得人分辨率還要低一些。由于是用干電池得到AD7714的輸入信號,該信號相對來說很穩(wěn)定,而且板上的噪聲也不是太大。請問各位大蝦,還有什么方法可以進(jìn)一步提高AD7714的分辨率啊?不勝感激!

2023-12-25 06:33:32

軟件還遠(yuǎn)遠(yuǎn)不夠。。。它的性能被進(jìn)一步提升,使用起來比之前任何時(shí)候都要簡單。首先,在WEBENCH? Filter Designer登錄頁內(nèi),你可以輕松進(jìn)入濾波器設(shè)計(jì)工具軟件。圖1顯示的是你的第一個(gè)濾波器

2018-09-04 14:59:10

C6748通過攝像頭采集的圖像如何進(jìn)一步處理,比如如何導(dǎo)入到MATLAB里面處理??

2018-07-25 06:23:56

如何進(jìn)一步減小DTC控制系統(tǒng)的轉(zhuǎn)矩脈動(dòng)?

2023-10-18 06:53:31

` 本帖最后由 sheniquhong 于 2017-7-6 15:41 編輯

開發(fā)板正面圖Altera Strati***板上竟然還有MAX系列的CPLD芯片NIOS II 6.0的flash rom背面圖2006年官方開發(fā)板`

2017-07-06 15:41:46

轉(zhuǎn)載:一步一步教你使用uCOS-II 資料整理

2012-08-04 11:14:38

《Altera FPGA/CPLD設(shè)計(jì)(高級篇)》結(jié)合作者多年工作經(jīng)驗(yàn),深入地討論了Altera FPGA/CPLD的設(shè)計(jì)、優(yōu)化技巧。在討論FPGA/CPLD設(shè)計(jì)指導(dǎo)原則的基礎(chǔ)上,介紹了Altera器件的高級應(yīng)用;引領(lǐng)讀者

2009-02-12 09:19:12 4799

4799 altera fpga/cpld設(shè)計(jì) 基礎(chǔ)篇結(jié)合作者多年工作經(jīng)驗(yàn),系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計(jì)方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera主流FPGA/CPLD的結(jié)構(gòu)與特點(diǎn),并通過豐富的實(shí)例講解

2009-07-10 17:35:45 57

57 EPM1270F256C4N,ALTERA/阿爾特拉,介紹MAX?II系列即時(shí)開啟非易失性CPLD基于0.18-μ,6層金屬閃存工藝,密度從240到2210個(gè)邏輯元件(LE)(128至22

2023-10-24 15:38:16

Altera MAX+plus II 介紹

一、軟件功能簡介MAX+plusⅡ(Multiple Array and Programming Logic User System)開發(fā)工具是美國Altera 公司推出的一種EDA

2008-09-24 10:15:36 6852

6852

【摘 要】 介紹利用MAX+PLUSⅡ軟件對Altera公司的CPLD進(jìn)行圖形設(shè)計(jì)、編譯以及在系統(tǒng)編程的基本方法和步驟。 關(guān)鍵詞:MAX+

2009-05-15 21:56:09 844

844

Altera新Cyclone IV FPGA拓展了Cyclone FPGA系列

Altera拓展其成功的Cyclone FPGA系列并延續(xù)其收發(fā)器技術(shù)領(lǐng)先優(yōu)勢,于今天發(fā)布Cyclone IV FPGA新系列。在移動(dòng)視頻

2009-11-04 08:46:38 1221

1221 Altera發(fā)布Quartus II軟件9.1,延續(xù)了2到3倍的編譯時(shí)間優(yōu)勢

Altera公司宣布推出QuartusII軟件9.1——在CPLD、FPGA和HardCopy ASIC設(shè)計(jì)方面,業(yè)界性能和效能最好的軟件。與以前的軟

2009-11-05 09:42:59 958

958 供電元件關(guān)斷和接通(也稱為閃斷)功能需要很少的系統(tǒng)干預(yù),是非常有用的節(jié)電技術(shù)。Altera MAX II CPLD支持簡潔的上電排序,提供專用功能,非常適合實(shí)現(xiàn)這類技術(shù)。本應(yīng)用筆記討論利用

2011-04-13 14:17:53 46

46 了30%,最大達(dá)到70%,進(jìn)一步擴(kuò)展了在軟件效能方面的業(yè)界領(lǐng)先優(yōu)勢。軟件還包括最新的快速重新編譯特性,適用于客戶對Altera Stratix? V FPGA設(shè)計(jì)進(jìn)行少量源代碼改動(dòng)的情形。采用快速重新編譯特性,客戶可以重新使用以前的編譯結(jié)果,從而保持性能,不需要前端設(shè)計(jì)劃分,進(jìn)一步將編譯時(shí)間縮短了50%。

2013-11-06 15:15:43 2685

2685 e絡(luò)盟日前宣布新增來自全球半導(dǎo)體和系統(tǒng)解決方案領(lǐng)先提供商英飛凌的CoolMOS?與OptiMOS?系列產(chǎn)品,進(jìn)一步擴(kuò)充其功率MOSFET產(chǎn)品組合。

2015-03-02 17:37:38 1391

1391 AEM收購芬蘭MEMS測試解決方案領(lǐng)先供應(yīng)商Afore。通過此次并購,AEM的全球解決方案供應(yīng)能力,將從邏輯IC測試機(jī)和RF(射頻)測量測試,進(jìn)一步拓展至完整的MEMS測試解決方案。

2018-02-05 12:34:40 6551

6551 雷神公司將進(jìn)一步拓展其在密西西比州Forest基地的制造中心。在基地的新建筑將成為測試、整合和生產(chǎn)S波段雷達(dá)的中心——包括美國海軍的下一代SPY-6空中和導(dǎo)彈防御雷達(dá)計(jì)劃。

2018-06-05 14:52:42 2972

2972 管理技術(shù),在Enpirion PowerSoC器件中集成高級多模式數(shù)字控制(MMDC)電源功能。由數(shù)字電源專家組成的設(shè)計(jì)團(tuán)隊(duì)將重點(diǎn)關(guān)注Enpirion PowerSoC的擴(kuò)展功能、適用性和低功耗特性,進(jìn)一步提高Altera FPGA和SoC的功效。

2018-08-16 11:26:00 749

749 單芯片SoC降低了系統(tǒng)成本,R-Car系列產(chǎn)品的擴(kuò)展性進(jìn)一步增強(qiáng),更加適合集成式儀表盤和車載信息娛樂系統(tǒng)的應(yīng)用 。

2018-10-17 13:09:56 6269

6269 Xilinx CoolRunner?-II CPLD提供與XC9500/XL/XV CPLD系列相關(guān)的高速和易用性,在單個(gè)CPLD中具有極低功率的XPLA3系列多功能性。這意味著,完全相同的部件

2019-02-22 17:25:50 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之ALTERA的CPLD與FPGA器件的詳細(xì)資料說明主要內(nèi)容包括了:一、Altera器件一般介紹,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、邊界掃描測試

2019-02-27 17:27:31 15

15 近日,海克斯康制造智能宣布與愛立信合作,綜合雙方在智能制造領(lǐng)域的優(yōu)勢,集成多智能傳感技術(shù)與5G技術(shù),進(jìn)一步增強(qiáng)建設(shè)自主連接智能工廠的能力。

2019-05-09 14:19:36 2596

2596 Altera公司今天宣布,NEC將使用Altera的 28nm FPGA,進(jìn)一步提高了其長期發(fā)展(LTE)基站的性能,支持無線服務(wù)供應(yīng)商高效的管理他們的網(wǎng)絡(luò)。

2019-05-14 15:34:45 774

774 MAX II具有傳統(tǒng)CPLD設(shè)計(jì)的低成本特性,MAX II CPLD還進(jìn)一步提高了高密度產(chǎn)品的功耗和成本優(yōu)勢,可以使用MAX II CPLD來替代高功耗和高成本ASSP以及標(biāo)準(zhǔn)邏輯CPLD。

2019-12-18 07:04:00 3059

3059

Altera的MAX? II 系列在所有CPLD系列中,其單位I/O引腳的功耗和成本都是最低的。不但具有傳統(tǒng)CPLD設(shè)計(jì)的低成本特性,MAX II CPLD還進(jìn)一步提高了高密度產(chǎn)品的功耗和成本優(yōu)勢,這樣,您可以使用MAX II CPLD來替代高功耗和高成本ASSP以及標(biāo)準(zhǔn)邏輯CPLD。

2019-12-16 07:08:00 2238

2238

Altera的MAX? II 系列在所有CPLD系列中,其單位I/O引腳的功耗和成本都是最低的。MAX II CPLD支持高級功能集成,以降低系統(tǒng)設(shè)計(jì)成本。

2019-12-12 07:02:00 2421

2421

近兩年來,英飛特加大拓展海外業(yè)務(wù),積極開展對外設(shè)立子公司、向子公司增資等一系列動(dòng)作。昨(6)日,該公司又接連發(fā)布公告宣布向子公司增資,以提升相關(guān)產(chǎn)能,進(jìn)一步開拓海外市場。

2020-04-07 16:05:31 9082

9082 Quartus II軟件為使用Altera?FPGA和CPLD設(shè)備進(jìn)行設(shè)計(jì)的系統(tǒng)設(shè)計(jì)師提供了一個(gè)完整的軟件解決方案。Quartus II程序員是Quartus II軟件包的一部分,它允許您編程

2020-09-17 14:41:00 32

32 Altera FPGA CPLD學(xué)習(xí)筆記(肇慶理士電源技術(shù)有限)-Altera FPGA CPLD學(xué)習(xí)筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79 安富利旗下全球電子元器件產(chǎn)品與解決方案分銷商e絡(luò)盟進(jìn)一步加大投入拓展Traco Power產(chǎn)品陣容,以提供充足現(xiàn)貨庫存來應(yīng)對供應(yīng)鏈挑戰(zhàn)。客戶現(xiàn)可通過e絡(luò)盟選購Traco Power的暢銷系列產(chǎn)品,包括高性能DC/DC轉(zhuǎn)換器、AC/DC電源和DIN導(dǎo)軌產(chǎn)品,且所有產(chǎn)品均為現(xiàn)貨。

2022-11-03 11:23:48 908

908 CPLD的MAX系列器件庫max-13.0.1.232

2022-12-21 17:26:11 4

4 電子發(fā)燒友網(wǎng)站提供《利用MAX II CPLD實(shí)現(xiàn)LCD控制器.pdf》資料免費(fèi)下載

2023-11-10 09:36:39 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論