先進半導體的工藝會給芯片成本帶來多少變化?

先進工藝制程成本的變化是一個有些爭議的問題。成本問題是一個復雜的問題,有許多因素會影響半導體制程成本。本文將討論關于半導體制程的種種因素以及預期。

晶圓成本

影響半導體工藝制程成本的第一個因素是晶圓成本。

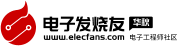

毫無疑問,晶圓成本在不斷上升。制程的金屬層數隨著工藝的演進不斷上升,在130nm時典型的制程有六層金屬,而到了5nm節點則預期至少會有14層金屬。

從90nm節點開始開始引入應力技術以繼續增強晶體管的性能,這也會增加制程的成本。從45nm到28nm節點,半導體制程引入了high-k柵技術以增強性能。

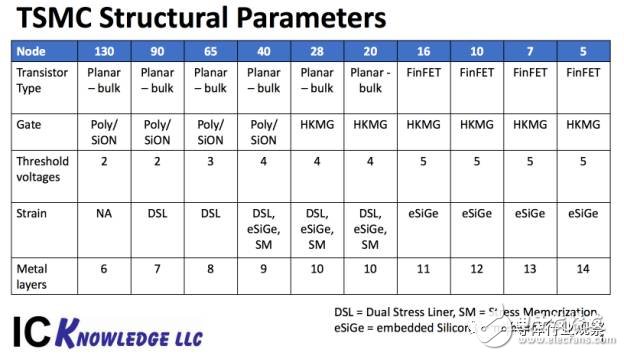

另一個變化是晶體管閾值電壓數目的變化。在130nm節點,晶體管只有兩種閾值(常規閾值RVT管與低閾值LVT管),而到了16nm之后,有了多達五種閾值(超高閾值UHVT,高閾值HVT,常規閾值RVT,低閾值LVT與超低閾值ULVT)。這是因為,從40nm到16/14nm FinFET,短溝道效應越來越明顯,為了控制漏電流必須引入多種閾值的器件。顯然,這也會增加掩膜成本。

在先進半導體制程中,還會引入新的技術,如在16/14nm節點引入的FinFET技術,在5nm引入的堆疊橫向納米線(stacked horizontal nanowire )技術。

?

?

上圖顯示了不同工藝節點用到的技術,據此不同的工藝節點用到的掩膜層數如下圖所示:

?

?

新的光刻技術

從20nm節點開始,為了使用傳統光刻技術實現更小的特征尺寸,半導體制程引入了多重pattern技術。光刻機在28nm的時候只需要一次的光刻曝光就可以實現了。

但到了22nm/20nm,單次曝光有時候就不能給臨界層提供足夠的分辨率。芯片制造商就通過多重pattern的方式解決問題。這也就是增加了一個簡單的兩步流程。這當中的主要的挑戰就是刻這些細線圖案。

為了達到目標,芯片制造商只好使用雙重pattern技術。在這個步驟里會需要兩次光刻和刻蝕步驟去確定一個單層。使用這種雙重pattern技術,可以減小30%的pitch,而三重pattern則需要三次曝光,也就是需要三次刻蝕步驟。

除此之外,業界在10nm和7nm還會碰到其他問題。在45nm和40nm的時候,設計的時候需要用到40層光罩,而到了14nm和10nm,光罩的需求量則上升到60層。“如果沒有EUV,只是靠沉浸式去實現三倍甚至四倍pattern,那么我們認為在7nm的時候,光罩數量會上升到80到85層之間”。三星的晶圓制造資深主管Kelvin Low表示。

光罩層數的增加,也就代表著成本的水漲船高。同時覆蓋物也將會成為Fab的災難。覆蓋物需要把光罩層有秩序的精確地放置在彼此的身上。而隨著mask的增加,覆蓋層也就會成為噩夢。如果沒對齊,覆蓋層問題就夠你喝一壺了。

另外,現在做一層光罩需要1到1.5天,在7nm的時候使用多重pattern,那就需要差不多五個月的時間才能做好晶圓。這就意味著如果繼續使用多重pattern,會導致晶圓成本高到無法接受。

除了多重pattern之外,另一種新的光刻技術是EUV。然而,EUV的掩膜制造也十分困難。EUV掩膜在很多方面與傳統193nm光刻的掩膜不一樣。因為它有很大的改變,對于每個產品的特性或者功能,在供應鏈中會產生很大影響,其中包括光刻膠、掩膜及中間掩膜,也涉及制造設備,如采用電子束寫入設備以及軟件。

在5納米時,掩膜的寫入時間是最大的挑戰。因為今天的單電子束寫入設備在做復雜圖形時的出貨不夠快,費時太久。從己經出爐的報告來看,由于技術原因,設備的研發用了比預期長得多的時間。事實上,任何突破性的創新技術從研發到成功,再達到量產水平,都是如此。

另外,即使使用EUV,多重pattern也是必須的。只有在真正的關鍵層才需要采用EUV,而其他層仍然用多重pattern。可以說,在未來這樣的混合模式光刻是趨勢。

而且,當EUV延伸至7納米以下時,作為一種提高光刻機放大倍率的方法,需要大數值孔徑的鏡頭(NA),為此ASML已經開發了一種變形鏡頭。它的兩軸EUV鏡頭在掃描模式下能支持8倍放大,而在其他模式下也有4倍,因此NA要達0.5至0.6。

由此帶來的問題是EUV光刻機的吞吐量矛盾,它的曝光硅片僅為全場尺寸的一半,與今天EUV光刻機能進行全場尺寸的曝光不一樣。最新 EUV 機器的價格超過 1 億歐元,是現有常規 193nm 光刻機價格的二倍多。

數字門密度與數字門成本

特征尺寸縮小最大的動力就是大規模ASIC中數字門尺寸縮小,從而在相同的芯片面積上可以放下更多的性能更好的標準單元。最終ASIC的成本應當同時考慮晶圓的成本以及門單元的密度。

數字門單元的尺寸在橫向上決定于多晶硅以及多晶硅通孔的間距,而在縱向上則等于金屬間最小間距乘以track數目。Track數越小,門尺寸越小,但是布線也越困難。

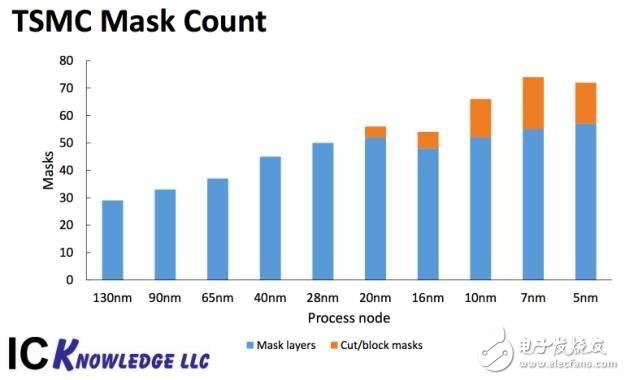

晶圓成本,數字門密度與數字門成本如下圖左所示。在130nm到65nm之間,晶圓成本上升的速度較慢,此后在40nm到20nm之間,晶圓成本上升由于加入了更多閾值電壓的晶體管而加快上升。在20nm之后,晶圓成本上升速度再次加快,這次是因為多重pattern。

數字門密度如下圖中所示,密度以指數趨勢上升,該趨勢與摩爾定律相符。單位數字門成本如下圖右所示,可見從130nm到20nm節點之間單位門成本下降較快,但是20nm之后單位門成本下降速度減緩。

Dark Silicon

目前芯片設計都有嚴格的功耗指標。隨著門單元密度隨指數上升,單位面積的功率密度也隨指數上升,但是芯片散熱能力上升卻沒這么快。為了解決散熱問題,在芯片上出現了Dark Silicon,即芯片上部分晶體管在大多數時候是不上電的,僅僅在用到的時候才會啟動。

這些Dark Silicon面積包括各類加速器,舉例來說手機SoC里面的視頻編解碼模塊的電源在不播放視頻的時候是關掉的。這些Dark Silicon在大部分時間是不起作用的,從另一個角度說Dark Silicon也增加了芯片的成本。

?

?

設計成本

在先進工藝設計成本可謂是一飛沖天。這就導致了在先進工藝下,芯片出貨量需要非常大才能抵消NRE成本。如今,越來越少的設計可以滿足如此大的出貨量,因此很多設計出于經濟上的考量不再使用最先進的工藝。

結語

盡管先進工藝的晶圓成本不斷攀升,門單元的成本卻能夠保持下降。然而,過高的設計成本卻成了一個問題,只有出貨量非常大的芯片才有機會使用最新工藝。

非常好我支持^.^

(1) 100%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 怎樣解決霍爾搖桿耗電量大的問題?揭秘霍爾芯片的選型要求 2023-10-24

- [電子說] Blackwell GB100能否在超級計算機和AI市場保持領先優勢? 2023-10-24

- [電子說] 淺析BUCK芯片在電路中的應用及特點 2023-10-24

- [電子說] OTA語音芯片NV040C在智能電動牙刷的應用 2023-10-24

- [電子說] 金川蘭新電子半導體封裝新材料生產線項目主體封頂 2023-10-24

- [電子說] 新思科技面向臺積公司N5A工藝技術推出領先的廣泛車規級IP組合 2023-10-24

- [電子說] 使用半大馬士革工藝流程研究后段器件集成的工藝 2023-10-24

- [電子說] 國產運放和溫度傳感器介紹 2023-10-24

( 發表人:steve )