系統硬件結構 - 基于dMAX和EMIF接口的數據傳輸

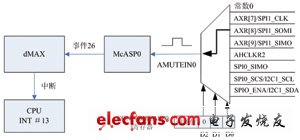

C6727B和其他DSP有一個較大的區別,就是C6727B不再提供專門的外部中斷引腳,而是采用GPIO引腳和dMAX配合使用,通過寄存器的設置將GPIO引腳配置成外部中斷引腳。本文為了實現FIFO的實時操作,一旦外設向FIFO寫入數據,即發出中斷信號到DSP的CPU,通知CPU讀取數據。為此,需要使用1個外部中斷引腳,將C6727B的音頻串口的AXR[8]配置成通用的GPIO引腳,并在dMAX中設置成中斷引腳。此時需要將音頻串口的CONFIGMACSP0寄存器設置為0x0001,如圖3所示。此時音頻串口不能再作為普通的音頻口使用,而是配置成IO接口。

?

圖3 中斷功能設置框圖

從圖3中可以看出,配置好音頻串口后,一旦AXR[8]引腳有上升沿到,則McASP0激活dMAX的事件26,向CPU發送內部中斷13。McASP的與中斷相關的寄存器配置是實現以上方案的重點。使用PFUNC寄存器將其配置成通用IO引腳;PDIR寄存器控制IO引腳的方向;如果是輸出引腳則由POUT引腳輸出高低電平,如果是輸入引腳,則由PDIN寄存器讀出該引腳的狀態;此外,可以使用PDCLR和PSET寄存器清除或者設置輸出引腳的狀態。

系統軟件設計

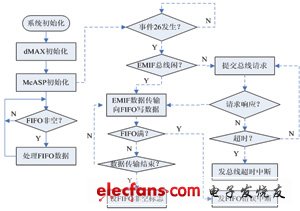

系統軟件設計主要包括McASP的初始化、dMAX的初始化、FIFO的初始化、中斷使能等。系統主程序只需要等待中斷進行相應的處理,主要的數據傳輸工作都是dMAX按照軟件配置自動完成,不需要CPU參與。圖4是實現由外設寫FIFO,DSP讀取FIFO數據的流程。圖中虛線部分表示由dMAX獨立完成的工作,實線部分表示由CPU完成的工作。兩者之間通過內部中斷方式實現狀態的交流。

?

圖4 系統軟件流程

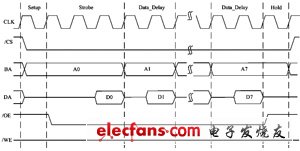

為了提高FIFO的讀寫速率,一般采用突發方式進行讀寫。突發方式的讀時序如圖5所示。寫時序和讀時序類似。突發方式一次最多只能讀寫8個數據,也可以一次突發讀寫4個或者2個數據。突發讀寫時數據的建立和保持時間最少可以設置成1個時鐘周期,如圖中所示。但為了通信可靠,一般采用2個時鐘周期。突發方式最大的節省時間是連續的其他數據將不再需要建立和保持周期,而是直接進行讀寫,一般只需要兩個時鐘周期就可以完成一個數據的讀寫。最快情況下,突發讀寫8個數據只需要20個時鐘周期,讀寫速率達到53.2M×32b/s,滿足大部分設備的要求。

?

圖5 突發讀時序圖

總結

dMAX的特有結構使得其可以實現嵌入式FIFO。本文介紹了基于C6727B的dMAX的基本結構以及基于dMAX的嵌入式FIFO軟硬件設計,設置通用GPIO引腳作為中斷,為了加快FIFO的傳輸速率,使用突發讀寫方式進行數據傳輸。嵌入式FIFO的實現,使得DSP和外部設備的通信更加方便和快捷,而且不需要CPU的參與,減輕了CPU的負擔,CPU可以專注于復雜的算法處理。

- 第 1 頁:基于dMAX和EMIF接口的數據傳輸

- 第 2 頁:系統硬件結構

本文導航

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 服務器硬盤通用基礎知識 2023-10-24

- [電子說] 暢行全球,美格智能SLM750模組鍛造出海核心優勢 2023-10-23

- [電子說] 蜂窩物聯4G DTU數據采集傳輸終端 2023-10-23

- [接口/總線/驅動] 一文詳解USB通信協議技術 2023-10-23

- [電子說] 英特爾? DSA 助力云軸科技網絡性能提升,海量數據傳輸游刃有余 2023-10-21

- [電子說] 簡單闡述一下光纖的一些區別 2023-10-20

- [電子說] 無人機遙控中應用的2.4GHz無線芯片 2023-10-19

- [電子說] 用于大容量數據傳輸的新型光子芯片 2023-10-19

( 發表人:葉子 )