概述

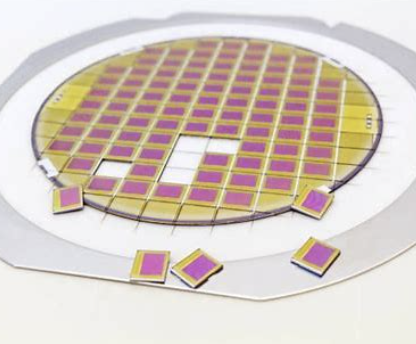

集成電路是由硅晶圓(wafer)切割出來的芯片(die)組成的。每個晶圓可以切割出數百個芯片。

ASIC是指針對特定應用而設計的集成電路(Application Specific Integrated Circuit),與通用的存儲器、微處理器等不同。ASIC有以下幾種類型:

全定制ASIC(Full-Custom ASIC):這種類型的ASIC是完全手工設計的,沒有使用預先設計好的邏輯門,而是自己繪制芯片的版圖(layout)。

標準單元ASIC(Standard Cell ASIC):這種類型的ASIC是使用預先設計好的邏輯門,例如AND,NOR等,來構建電路。這些邏輯門被稱為標準單元(Standard Cell)。標準單元ASIC的優點是設計者可以節省時間、金錢和風險,因為標準單元庫已經過設計和測試。每個標準單元都是用全定制的方法設計的,可以進行單獨的優化。

設計ASIC時,需要平衡以下幾個目標:

速度(Speed):指芯片運行的時鐘頻率和響應時間,影響芯片的性能和效率。

面積(Area):指芯片占用的硅晶圓面積,影響芯片的成本和產量。

功耗(Power):指芯片運行時消耗的電能,影響芯片的可靠性和散熱。

上市時間(Time to Market):指從設計開始到產品上市所需的時間,影響芯片的競爭力和市場占有率。

為了實現這些目標,設計者需要熟悉CMOS工藝,即使用互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor)制造芯片的技術。

CMOS工藝

1.1 CMOS工藝

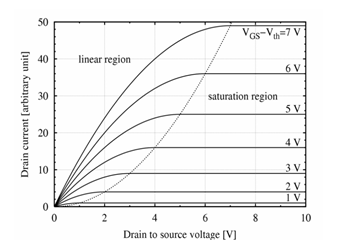

CMOS工藝是目前最常用的芯片制造技術,它利用互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor)來構建電路。CMOS電路由NMOS和PMOS兩種類型的MOSFET晶體管組成。

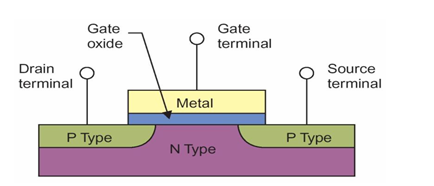

1.2 MOSFET晶體管

MOSFET是金屬氧化物半導體場效應晶體管(Metal Oxide Semiconductor Field Effect Transistor)的簡稱,它是一種電壓控制的開關器件,也是數字集成電路設計中的基本單元。MOSFET的結構和工作原理如下圖所示。

?

CMOS工藝利用NMOS和PMOS兩種MOSFET來實現高密度、復雜的數字集成電路,主要用于信號處理。CMOS工藝的優點是低功耗、高速度和易于集成等。在數字IC中,MOSFET可以看作是簡單的開關。例如:CMOS反相器只需要一個PMOS和一個NMOS晶體管。

當輸入為邏輯“0”時,PMOS導通,NMOS截止,輸出負載電容被充電,輸出為邏輯“1”。

當輸入為邏輯“1”時,PMOS截止,NMOS導通,輸出負載電容被放電,輸出為邏輯“0”。

邏輯門的輸出負載電容由兩部分組成:本征電容和外部電容(走線、扇出等)。PMOS和NMOS的載流子分別是空穴和電子。由于電子的遷移率比空穴高出一倍多,導致輸出上升時間和下降時間不對稱。

為了平衡這種差異,通常讓PMOS的寬長比(W/L)比NMOS的大一些。這樣可以使PMOS和NMOS具有相近的驅動能力(drive strength)。

在標準單元庫中,晶體管的長度L一般是固定的,而寬度W則根據不同門的驅動需求進行調整。

1.3 CMOS集成電路的功耗

CMOS集成電路的功耗主要有以下三個來源:

動態功耗:由于電路負載電容在開關過程中的充放電而產生。給定頻率f,動態功耗為:負載電容* Vdd * Vdd * f

短路功耗:由于PMOS和NMOS在開關過程中同時導通而形成短路路徑而產生。

靜態功耗:由于晶體管存在漏電流而產生。

1.4 CMOS傳輸門

將PMOS和NMOS并聯起來就形成了傳輸門。傳輸門可以將輸入信號傳遞到輸出端。

1.5 時序元件

在CMOS中,可以通過反饋回路來實現邏輯值的存儲,這樣的元件被稱為時序元件。最簡單的時序元件就是兩個反相器相互連接。基于這種結構,可以有兩種基本的時序元件,分別是:

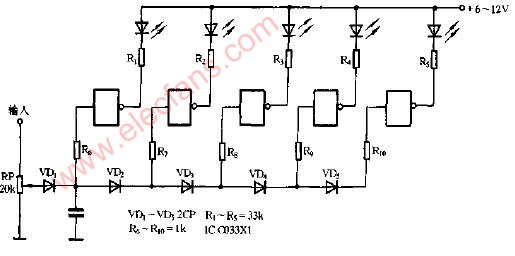

1、鎖存器(Latch):鎖存器是在兩個反相器之間加入一個傳輸門來控制數據的輸入和輸出。

當傳輸門的控制信號為邏輯“1”時,傳輸門打開,輸入信號“D”可以傳遞到輸出端。

當控制信號為邏輯“0”時,傳輸門關閉,輸出端保持原來的值不變。??

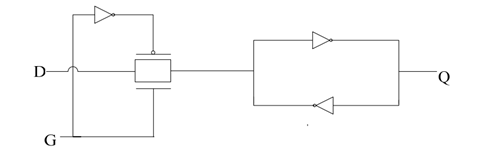

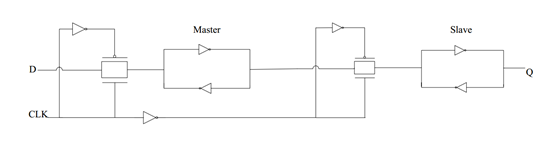

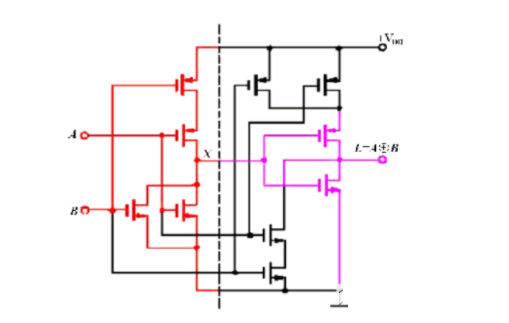

2、觸發器(Flip-Flop):觸發器是由兩個鎖存器串聯而成的。第一個鎖存器叫做主鎖存器(Master latch),第二個鎖存器叫做從鎖存器(Slave latch)。

在這種情況下,傳輸門的控制信號就是時鐘信號(Clock)。時鐘信號經過反相后送到從鎖存器的傳輸門。

當時鐘信號為高電平時,主鎖存器的傳輸門打開,輸入信號“D”可以被兩個反相器鎖定。同時,由于時鐘信號反相,從鎖存器的傳輸門關閉,輸出信號“Q”保持原來的值不變。

當時鐘信號為低電平時,從鎖存器的傳輸門打開,輸出信號“Q”更新為主鎖存器鎖定的值。此時,輸出信號“Q”與輸入信號“D”的變化無關。

由于觸發器只在時鐘信號由低變高的上升沿更新數據,所以這種類型的觸發器叫做正邊沿觸發器。如果觸發器只在時鐘信號由高變低的下降沿更新數據,則叫做負邊沿觸發器。??

芯片設計的過程

要設計芯片,首先需要有一個清晰的設計目標和功能需求(Idea)。

在ASIC設計流程中,這個Idea會不斷地轉化為不同的表現形式。

ASIC設計流程的第一步就是把Idea寫成詳細的規格說明書(Specifications)。規格說明書包括:

設計的目標和約束條件。

設計的功能描述。

設計的性能指標,如速度和功耗。

設計的面積預估。

設計的制造工藝和設計方法選擇。

傳統意義上,ASIC設計流程如下所示:

1、給出設計的結構和功能分解(Structural and Functional Description)。這意味著要確定使用什么樣的設計架構,例如 RISC / CISC,ALU,流水線等,并且將整個系統劃分為若干個子模塊。每個子模塊的功能也要在規格說明書中明確定義。

2、確定了系統層次結構之后,就要開始用具體的邏輯元素來實現設計的功能。這一步稱為RTL級邏輯設計(Register Transfer Level)。RTL設計通常用硬件描述語言(Verilog、VHDL)來編寫。硬件描述語言(HDL)是一種用于描述數字系統的語言,可以用來表示邏輯門、微處理器、存儲器、觸發器等任何級別的硬件。在這個階段,要對設計進行功能驗證,以確保設計符合規格說明書的要求。

3、功能驗證

4、邏輯綜合(Logic synthesis),使用Design Compiler (Synopsys),Genus(Cadence)等綜合工具,將 RTL代碼轉換為優化后的門級網表(Gate Level Netlist)。綜合工具需要輸入RTL代碼和標準單元庫(Standard cell library),輸出門級網表。標準單元庫是集成電路設計中常用的基本邏輯模塊的集合。綜合工具在進行邏輯綜合時,要考慮各種約束(Constraints),如時序、面積、可測性和功耗等。綜合工具會根據不同的優化策略和代價函數(cost function),來尋找滿足約束條件的最佳實現方案。邏輯綜合完成之后,會得到一個只包含結構信息而不包含行為信息的門級網表。

5、對門級網表進行功能驗證,以檢查是否與RTL代碼一致。

6、門級網表的物理實現(Physical Implementation)。這一步是將門級網表映射到芯片上的具體位置和連線。物理實現需要考慮制造工藝對布局布線(Layout)的限制條件,如DRC規則等。物理實現步驟包括三個子步驟:Floor planning->Placement->Routing。物理實現的輸出是GDSII文件。這是芯片制造廠所需要的文件格式。物理實現可以由IC Compiler (Synopsys)、Innovus (Cadence)等軟件完成。

7、進行物理驗證(Physical Verification),以檢查是否滿足DRC規則、LVS規則等。?

8、時序分析。對于任何有特定時鐘頻率要求的設計,都必須進行時序分析(timing analysis)。我們需要檢查設計是否滿足規格說明書中的時序要求。這是通過靜態時序分析(Static Timing Analysis)工具完成的,例如Primetime(Synopsys)。它會檢查設計中所有的時序路徑,來驗證設計是否存在時序違規(timing violations)。例如:建立時間(setup)、保持時間(hold)等。

9、在物理實現和時序分析都通過之后,設計就可以交付給制造廠進行制造(Fabrication)了。制造完成之后,芯片會被切割、封裝和測試。

最后,值得思考的是,我們是否一定要遵從這種瀑布式開發流程???能否盡可能地流程左移。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論