選擇越多,選擇越難。

芯片制造商開始將多種類型和風格的 DRAM 整合到同一個先進封裝中,為日益分布式的內存但更加復雜的設計奠定了基礎。盡管多年來預測 DRAM 將被其他類型的內存取代,但它仍然是幾乎所有計算中的重要組成部分。它的足跡非但沒有消失,反而在增加,選擇的數量也在增加。

有幾個因素推動了這種擴張。

首先,系統中計算元素的數量和密度不斷增加,以更快地處理更多數據,特別是對于人工智能/機器學習和數據中心應用程序。更多的核心需要更多的內存,因為需要有一個地方來存儲數據并處理數據。

其次,通常情況下,大部分數據都會在緩存中處理,而 SRAM 一直是 L1 到 L3 緩存的首選內存。但 SRAM 的擴展速度不再與數字邏輯相同。因此,它在芯片上占用了更大的空間,并且 DRAM 速度的提高使得某些類型適合 L3 緩存。

最后,來回移動數據移動受到帶寬和距離的限制,因此僅在一個物理位置添加更多內存并不一定會提高性能。事實上,它可能會起到相反的作用。

由于這些原因,芯片制造商正在使用更多的 DRAM。在某些情況下,DRAM(尤其是HBM)正在取代一些 SRAM。DRAM 擁有久經考驗的耐用性記錄以及成熟的工藝,而且比 SRAM 便宜得多。Objective Analysis 總經理 Jim Handy 表示,根據原始數據,相同容量的 SRAM 成本可能比 DRAM 高出 2,500 倍以上,具體取決于 DRAM 的類型。

當然,DRAM有多種類型可供選擇。有些速度非常快,如HBM,但也很昂貴。其他類型速度較慢,但價格便宜,如基本的DDR DIMM。然而,變化的是,在異構架構中,兩者都可以發揮重要作用,以及多種其他DRAM類型和更狹義的存儲器,如MRAM或ReRAM。

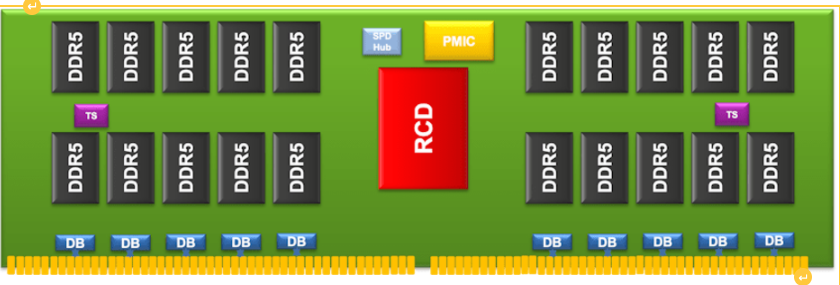

“我們正在考慮更多的混合模型,在同一系統中使用不同的 DRAM 技術,”Cadence 高級技術營銷經理 Kos Gitchev說。“如果您確實需要非常高的性能,并且愿意為此付費,那么您可能會選擇 HBM。您可以將其用于 L3 緩存,或者您需要立即訪問的任何其他內容。如果您仍然需要更多內存,但延遲稍長,則可以在RDIMM(注冊雙列直插內存模塊)或 MRDIMM (多路復用器級 DIMM)中使用 DRAM。如果您正在尋找大容量,那么您可能會考慮CXL后面的 DRAM。該技術開始針對非常具體的應用程序,具有真正的高帶寬和低功耗、更大的內存占用,但延遲稍多。將所有這些混合在一起是每個人解決這些問題的方向。”

與先進節點或先進封裝的幾乎每一項改進一樣,解決一個問題可能會導致另一個問題。盡管如此,基本理論是合理的,并且當今市場上也有證據。例如,保持某些功能(例如人工智能)以最大速度運行可能至關重要,這將使高帶寬內存成為最佳選擇。但并非所有功能都是必需的,并且它們并不都需要這種級別的性能。在某些情況下,GDDR5 或 GDDR6 可能就足夠了。在其他情況下,可能是 LPDDR,在其他情況下可能是 DDR4。所有這些都有不同的成本,這些成本可以用來回移動數據的資源以及存儲芯片的貨幣價值來衡量。

另一方面,并不是所有的DRAM都是一樣的,在沒有充分了解不同類型的 DRAM 會如何影響其他組件的情況下,僅添加不同類型的 DRAM 可能會導致問題。重要的是要以避免未來問題的方式將它們集成起來,這包括復雜的布局規劃,以避免信號完整性和防止熱問題。眾所周知,DRAM和散熱不太好。但也有一堆以前從未認真考慮過的新問題。

“DRAM 向前發展的重大問題分為兩類——常見的問題(更多的帶寬和容量、管理功率)和一些新的問題(更具挑戰性的可靠性,這導致了片上 ECC 和 RowHammer 保護等問題), ” Rambus的杰出發明家 Steven Woo 說道。“為了應對新的挑戰,在芯片上放置更多的電容器會增加片上錯誤的發生,因此今天的 DRAM 在數據返回到控制器之前會進行一定量的片上錯誤糾正。像 RowHammer 這樣的相鄰單元干擾問題的發生是因為這些單元彼此非常接近,訪問一組單元可能會導致鄰近單元的位翻轉。”

什么地方最有效

選擇的數量不斷增加,也讓我們很難決定使用哪些存儲器。通常根據性能、功耗、成本、可靠性(糾錯碼以及經過全面測試和供應鏈安全)和容量來選擇 DRAM。因此,如果 DRAM 將用于 L3 緩存,則可能需要高性能和低功耗。如果要用于高級封裝中的低級功能,則它可能是標準 DIMM。

但這些選擇中的每一個也會影響整體芯片或系統級封裝設計,并伴隨著特定的設計考慮。

“過去,DDR4 和 LPDDR4 并沒有那么復雜,”Synopsys 產品營銷高級經理 Graham Allan表示。“一個客戶將啟用 DDR4,另一個客戶將啟用 LPDDR4,并且存在重疊。隨著我們進入 DDR5 和 LPDDR5 及更高版本,這些應用空間確實發生了分化,接口協議和物理信令也發生了變化。DDR5 通常需要與大量 DRAM(大容量)通信,因此您主要與寄存器 DIMM 連接。使用 LPDDR,您通常會與一個封裝或設備通信,并且該設備中最多有兩個負載。LPDDR 也是接地端接的。DDR 端接到正電壓軌。這些是非常不同的物理接口和協議,這意味著客戶需要選擇其中之一。”

還有一些中間選項可以幫助在多個應用程序中使用相同的設計。例如,MRDIMM 可用于將容量加倍或將帶寬加倍,具體取決于工作負載。“多路復用器級 DIMM 的容量和速度是 SDRAM(同步 DRAM)的兩倍,”Allan 說。“它的美妙之處在于 DRAM 不會改變。它以兩種不同的模式運行。它的運行方式類似于負載減少的 DIMM,但速度不會加倍。這將是一種使用它來獲得更高容量的模式。或者它以多路復用排序模式運行,這使得 DRAM 和外部接口之間的帶寬加倍。”

這是圖片的一部分。另一部分是 PHY,即物理層,它提供與內存的物理接口。PHY 因所使用的 DRAM 類型而異,隨著數據量的增加和設計變得越來越異構,它們變得尤為重要。

PHY 還可以鏈接在一起形成一種主堆棧,以便管理復雜設備中的內存資源,無論是 GDDR6 還是 LPDDR4。這樣,所有類型的 DRAM 都可以被視為可用資源并進行集中管理。

“通過某種類型的結構來管理帶寬,所有內容都是可見且可尋址的,”瑞薩電子基礎設施業務部公司副總裁兼總經理 Balaji Kanigicherla 說道。“這不僅僅是提高密度或存儲器的物理原理,這是材料科學。存儲器的應用架構是產業發展的方向。密度需要提高,因為您希望在相同的帶寬下獲得更多的容量。我們可以根據每美元或每 GB 的路徑進行混合和匹配,并且可以在 SSD、DRAM 和本地片上 SRAM 緩存之間使用分層。這正在轉向整個系統的 TCO,并考慮我們將為每一層支付的成本。”

這本質上提高了內存管理的抽象級別。Kanigicherla 表示:“您可以從當前模型發展到在全球范圍內解決內存問題,并基本上創建足夠有效的互連來管理緩存或減少延遲。” “這就像全局可尋址內存的一個分區。顯然,您需要提供帶寬。但好消息是,對于人工智能工作負載,它們對延遲的敏感度稍低,對帶寬的敏感度更高。所以你可以利用這項技術來擴大規模。在 CXL 和 UCIe 之間,應該有一種更漸進的方法來分解存儲器,可能包括光學互連,并實現存儲器的完整全局視圖。但這需要整個行業的努力才能實現。這并不簡單。”

內存池是另一種選擇,并且在數據中心中越來越受歡迎。內存池對于 DRAM 的作用就像超擴展對于處理器核心的作用一樣。當需要額外的內存時,可以像使用額外的計算核心一樣使用它,通常是通過 CXL 接口。

Rambus 說:“池化背后的想法是,如果我有一組服務器,并且每臺服務器都有內存,那么每臺服務器不太可能同時使用所有內存容量。” Woo 最近在CASPA活動中的一次演講中說道。“更有意義的是將其中一些容量放入外部機箱中,并將其視為池資源。當處理器需要的內存超過機箱內的內存時,它們可以在短時間內檢查并配置一些內存,將其用于計算,然后將其返回到池中。這是讓很多業內人士興奮不已的新功能之一。更遠一點,一旦你做了這些類型的事情,你就可以開始考慮通過交換機附加內存和池。CXL標準還允許多級切換。這種靈活性將有助于提高各種應用程序的性能和總擁有成本。”

其他存儲方法

除了更傳統的方法之外,DRAM 還向多種方向發展。部分原因是轉向異構集成和高級封裝以及更多特定領域的設計,部分原因是更接近數據源進行處理的好處。

“與計算和 DRAM 相比,我們使用 17% 的能量進行計算,并使用 63% 的能量將數據從一個點移動到另一個點,”Siemens Digital Industries Software 的內存技術專家 Jongsin Yun說道。“這是大量的能量。我們可以節省這一點并提高速度和電源效率。當前的解決方案是向緩存中添加更多內存,但這是一個昂貴的解決方案。我們不需要將所有數據移動到 DRAM。我們可以在內存中進行一些計算,或者使用一些基于 GPU 的 AI 卷積,這樣我們就可以在不進行內存傳輸的情況下進行計算。”

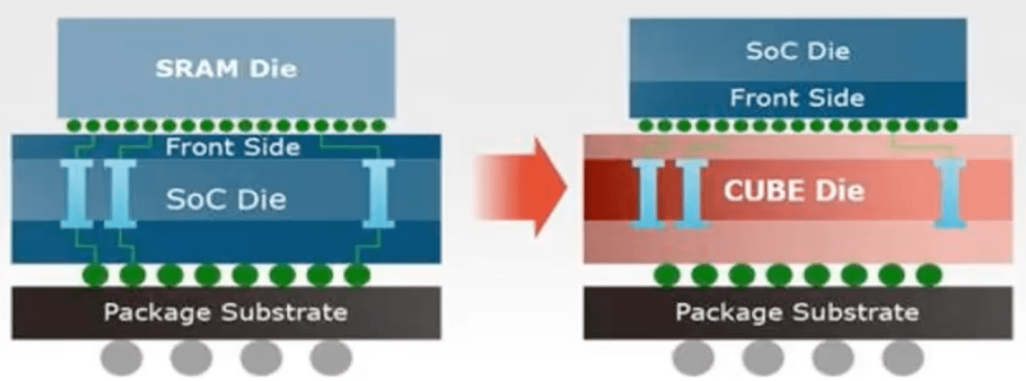

今天的選擇比以往任何時候都多,而且還有更多的選擇處于開發階段。例如,華邦電子開發了幾種基于 DRAM 的內存解決方案,但超越了經典的 DRAM 使用模型。一是該公司的單芯片CUBE(定制超帶寬元件)架構。另一種是偽靜態 DRAM,它介于 SRAM 和 DRAM 之間,無需外部數據重寫。這兩者都針對特定市場,例如可穿戴設備和邊緣服務器。

“現在最熱門的話題是生成式人工智能,”華邦電子美國公司營銷主管 CS Lin 說。“但是數據中心發生的情況與我們關注的地方有不同的要求,而且密度也有很大不同。我們專注于 16 GB/秒及以下的密度,但該解決方案可擴展到 256 KB/秒。它的運行速度非常接近 HBM2 帶寬,但具有功耗極低的優勢。”

CUBE 方法,延遲約為 25 納秒,單位密度比 14 納米 SRAM 高 5 倍。來源:華邦電子

Lin 表示,這種方法的好處是能夠使用標準 DRAM 來提高性能,而不是依賴最先進的工藝節點。通常,較高的密度會產生延遲,但 CUBE 架構使用數千個硅通孔來移動數據,并根據更多帶寬或更高速度的需求靈活分配這些通孔。這允許更細粒度的系統架構,以及更小的占地面積。

另一種方法是均衡。這個計劃已經醞釀了一段時間,但似乎終于獲得了關注。“均衡可以改善您在通道末端接收到的數據,”Synopsys 的 Allan 解釋道。“簡單來說,這就像符號間干擾。當一系列比特通過通道傳輸時,當一個比特完成時,它實際上已經進入下一個比特的時域。信號上升和下降以及從 1 到 0 的切換需要比一個單位間隔更長的時間。你并不是從穩定的低潛力狀態開始的。你是從一個更高的狀態開始的。使用決策反饋均衡來偏移輸入接收器中的采樣點。那么我現在如何優化我的輸入接收器,以便對一和零檢測具有相似的余量?我并沒有真正感覺到有什么東西可以將參考電壓精確地放在中間。”

內存計算也即將出現。雖然已經有幾種使用 MRAM 的商業方法,但普林斯頓大學的研究人員在 2019 年的一篇論文中展示了 FPGA 中的外部 DRAM 控制器,可以與現成的 DRAM 一起使用來創建大規模并行計算。研究人員聲稱,這種方法克服了所謂的內存墻,即邏輯性能已經超過了內存帶寬。

權衡

那么,與DRAM相比,SRAM的使用量是多少?對此沒有簡單的公式,因為這不是同類比較。

Flex Logix首席技術官兼聯合創始人 Cheng Wang 表示:“確實沒有什么神奇的方法可以做到這一點。”我們的大部分設計權衡來自于對 SRAM 帶寬、SRAM 容量和 DRAM 帶寬進行建模的性能估計。這是我們的三個主要旋鈕。基本上,我們有四種標準的計算規模,為我們的標準 IP 產品提供不同數量的 SRAM 和 DRAM 帶寬。這是基于我們運行模型的經驗數據來確定哪種效果更好。如果我們有 2 倍的 SRAM 容量,某些模型可以運行得更好。如果您可以通過將 SRAM 加倍來使性能幾乎翻倍,并且再用 20% 的面積來實現 2 倍的性能,那就太好了。但還有很多其他型號無法從額外的 SRAM 中受益,那么您就白白添加了該區域。這就是為什么進行周期準確的性能估計很重要。在我們的例子中,它的精確度不能精確到單個周期,但可以精確到 8%,這超出了我們的需要。然后,您可以對適當的 SRAM/DRAM 計算權衡進行大量架構分析,這可能因工作負載類型而異。”

這是復雜的數學,并且隨著系統被分解為異構元素(例如小芯片),它變得更加復雜。“SRAM 每一位需要更多晶體管才能實現。它比 DRAM 密度更低、更昂貴,并且在讀取和寫入過程中具有更高的功耗。” Ansys首席產品經理 Takeo Tomine 說道。“目前,SRAM 是在 CPU 通常設計的先進 finFET 技術節點上設計的,而 finFET 器件由于器件的熱阻較高,更容易產生熱效應(自熱)。”

在某些情況下,使用什么類型的內存以及在何處使用它可能取決于設備的預期使用壽命。“有兩個主要的可靠性問題會導致存儲器的壽命縮短,”Tomine說。“其中之一是,互連可靠性與技術節點縮小會導致存儲器的使用壽命縮短,因為自熱會導致嚴重的電遷移(EM),這是最關鍵的可靠性問題之一。材料和工藝技術以及技術擴展不斷提高電磁壽命。其次是不同架構的設備帶來的可靠性挑戰。在將器件架構從 finFET 轉移到納米片再到 CFET 的過程中,熱阻急劇增加,這意味著器件通道的 Delta T 值更高。器件自熱將與金屬焦耳熱耦合。器件的自熱會影響柵極氧化物擊穿(時間相關的電介質擊穿),并且還會降低 HCI(熱載流子注入)性能,從而使器件的 BTI(偏置溫度不穩定性)惡化。”

可靠性是衡量存儲設備在給定時間內無故障運行的能力的指標。智能手機的預期壽命為 4 年,而汽車、軍事或金融服務器應用的預期壽命為 10 至 15 年(或更長),這一時間范圍可能非常不同。能夠理解可能影響存儲器壽命的潛在相互作用至關重要,它們可能因架構、存儲器類型和使用情況而異。

這也會影響使用哪種內存以及整個系統架構。因此,如果記憶可以被替換,那么與將這些記憶嵌入某種類型的高級封裝中并密封起來相比,壽命就不那么重要了。“這就像擁有一個 DRAM卡池,現在就可以升級,”瑞薩電子的 Kanigicherla 說道。“使用 HBM,如果出現問題,你將無能為力,因此你將扔掉非常昂貴的芯片。在CPU方面,服務器之間的聯系非常緊密,你無法做太多的事情來升級任何東西。這就是全局共享內存概念起作用的原因。其中一些解決方案是自動出現的。”

延遲增加了另一個權衡。“特別是使用 HBM,可以將處理器和 DRAM 非常緊密地結合在一起,”Cadence IP 集團產品營銷總監 Frank Ferro 說道。“這樣做有很多好處。HBM 一直在快速發展。我們幾乎每兩年就會看到性能的改進。所以這條曲線很陡。但從系統設計的角度來看,2.5D仍然是一個挑戰。優化中介層并幫助客戶設計這確實是對話的關鍵部分。”

結論

自 1967 年發明以來,DRAM 一直是計算的關鍵。盡管多年來無數存儲技術對其提出了挑戰,但沒有任何技術可以取代它。鑒于圍繞這項技術的狂熱活動,在可預見的未來沒有任何東西可以取代它。

DRAM 現在不再是一種類型,而是有多種類型,并且每種類型都在不斷發展并催生新的想法。從內存到處理元件的物理連接,到服務器機架外部的內存池,各個層面都有創新。目前正在努力縮短信號在內存和處理器內核之間傳輸的距離,這將減少移動數據所需的功耗以及每個周期所需的時間。

從長遠來看,DRAM 仍然是一個充滿活力和創新的領域,并且即將出現更多的創新和不同的方式來組合內存解決方案,這些解決方案可以對性能、成本、可靠性和壽命產生重大影響。

編輯:黃飛

電子發燒友App

電子發燒友App

評論