作為全球技術(shù)最先進(jìn)的廠(chǎng)商之一,英特爾在10nm工藝上的一再拖延已經(jīng)讓業(yè)界對(duì)其Tick-Tock更新頻率的質(zhì)疑,乃至擔(dān)心摩爾定律是否繼續(xù)延續(xù)。但日前,Intel一口氣推出了10nm的各項(xiàng)細(xì)則,并對(duì)10nm寄于了厚望,也發(fā)布了22nm FDSOI工藝,叫板Globalfoundries。我們來(lái)看一下全球半導(dǎo)體巨頭的“大動(dòng)作”。

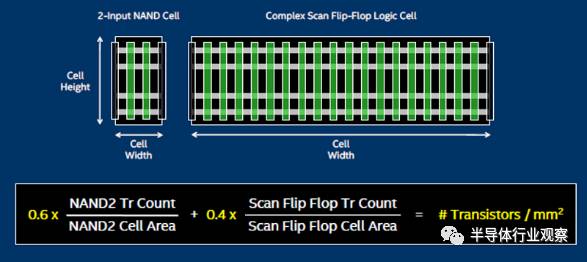

提議的晶體管密度度量方法

英特爾今年將開(kāi)始制造10nm芯片,它提出了一種引領(lǐng)行業(yè)晶體管密度度量方式,迫使競(jìng)爭(zhēng)對(duì)手采用。另外,它宣布推出一款22nm低功耗FinFET(鰭式場(chǎng)效應(yīng)晶體管)節(jié)點(diǎn),通過(guò)全耗盡型絕緣層上硅技術(shù)(FD-SOI)與Globalfoundries等對(duì)手競(jìng)爭(zhēng)代工業(yè)務(wù)。

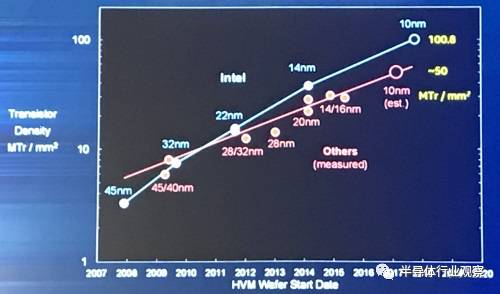

英特爾的10nm工藝每平方毫米將封裝10080萬(wàn)個(gè)晶體管。據(jù)估計(jì),目前臺(tái)積電和三星生產(chǎn)10nm工藝,晶體管密度只有它的一半。

英特爾度量方法的平均密度是指小型和大型邏輯單元的密度。具體而言,它使用的是有兩個(gè)有源柵極的雙輸入與非單元,以及一個(gè)有多達(dá)25個(gè)有源柵極的掃描觸發(fā)器單元。

工藝架構(gòu)與整合的資深研究員兼總監(jiān)Mark Bohr說(shuō):“我認(rèn)為這是一個(gè)全面、量化和誠(chéng)實(shí)的指標(biāo)。我認(rèn)為,臺(tái)積電和三星過(guò)去曾采用它,但我猜他們不太好再用這個(gè)度量了。”

英特爾建議競(jìng)爭(zhēng)對(duì)手重新使用這個(gè)密度度量方法來(lái)定義節(jié)點(diǎn)。

乘法門(mén)間距和單元高度的現(xiàn)有度量體現(xiàn)了節(jié)點(diǎn)相對(duì)數(shù)量的增加,而不是節(jié)點(diǎn)能力絕對(duì)數(shù)值的提升。此外,它不包括英特爾提出的密度度量方法所包含的各種因素。Bohr補(bǔ)充道。

無(wú)論是哪種度量方法,英特爾表示,都將在今年下半年開(kāi)始制造10nm Cannonlake芯片,這在它推出14nm工藝的三年后。預(yù)計(jì)升級(jí)10nm工藝將繼續(xù)著為期三年的節(jié)奏,兩次年度升級(jí)可稱(chēng)為10+和10++。

英特爾晶圓廠(chǎng)和銷(xiāo)售團(tuán)隊(duì)執(zhí)行副總裁Stacy Smith表示:“即使節(jié)點(diǎn)之間的升級(jí)時(shí)間較長(zhǎng),我們也將保持與晶體管曲線(xiàn)相同的成本,我們預(yù)計(jì)10nm這一代仍將繼續(xù)這種情況。”

有趣的是,英特爾的14nm++表現(xiàn)出的性能高于它最初的10nm工藝。然而10nm節(jié)點(diǎn)可以提供低功耗、高密度。

英特爾對(duì)于其10nm節(jié)點(diǎn)透露了比以往更多的細(xì)節(jié)。x86巨頭需要通過(guò)對(duì)比競(jìng)爭(zhēng)對(duì)手臺(tái)積電和三星正在進(jìn)行的10nm工藝,更進(jìn)一步地展示其優(yōu)勢(shì),

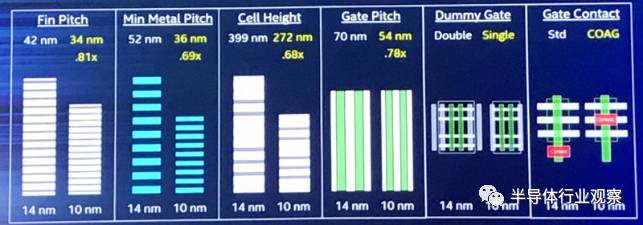

具體而言,英特爾的10nm節(jié)點(diǎn)包括:

34nm鰭片間距

53nm 鰭片高度

36nm 最小金屬間距

272nm 單元高度

54nm 柵極間距

英特爾聲稱(chēng),節(jié)點(diǎn)展現(xiàn)了行業(yè)中最緊密的柵極間距和金屬間距,標(biāo)志著行業(yè)首次使用自對(duì)準(zhǔn)四重圖案成形技術(shù)(self-align quad patterning)。相比于14nm節(jié)點(diǎn)時(shí),F(xiàn)inFET(鰭式場(chǎng)效應(yīng)晶體管)的高度和密度提高了25%。

英特爾描述了晶體管的兩個(gè)創(chuàng)新,以補(bǔ)償更多光刻圖案步驟帶來(lái)的成本上漲。有源柵極上接觸(contact-over-active-gate,COAG)有助于提供額外10%的密度;10nm時(shí),單個(gè)而不是雙虛擬柵極提供了額外的縮放優(yōu)勢(shì)。

英特爾聲稱(chēng)其10nm工藝的節(jié)點(diǎn)密度是其競(jìng)爭(zhēng)對(duì)手的兩倍。(圖片來(lái)源:英特爾)

對(duì)10nm不吝贊美,對(duì)度量方法褒貶不一

分析師對(duì)英特爾的10nm節(jié)點(diǎn)印象深刻,但對(duì)于晶體管密度是否是衡量競(jìng)爭(zhēng)節(jié)點(diǎn)的最佳指標(biāo)褒貶不一。他們表示,在28和16nm競(jìng)爭(zhēng)日益激烈的情況下,現(xiàn)在還不清楚誰(shuí)會(huì)贏得這一重大前沿業(yè)務(wù)。

市場(chǎng)觀察家VLSI研究公司總裁G. Dan Hutcheson表示:“現(xiàn)在是時(shí)候擺脫這些利用節(jié)點(diǎn)名稱(chēng)搞的市場(chǎng)營(yíng)銷(xiāo)手段了,讓大家看看節(jié)點(diǎn)的真面目……摩爾定律總是關(guān)于密度。”

他表示,進(jìn)行芯片級(jí)別拆解的獨(dú)立分析師能夠使用公式來(lái)檢驗(yàn)芯片密度。但是較大的尺寸(例如cm2)將使得對(duì)照更接近真實(shí)SoC的大小。

Gartner半導(dǎo)體集團(tuán)研究副總裁Bob Johnson說(shuō):“我們需要客觀地比較節(jié)點(diǎn)名稱(chēng)的擴(kuò)展,顯示出與它們的名稱(chēng)無(wú)關(guān)的維度。”

臺(tái)積電的一位發(fā)言人說(shuō),先前基于柵極密度的度量方法比現(xiàn)在基于單元高度要好得多。

她表示:“我不知道英特爾如何進(jìn)行新的計(jì)算。它的Broadwell(第一代14nm CPU)每平方毫米有1840萬(wàn)個(gè)晶體管,但在新的度量方法下,每平方毫米突然有了3750萬(wàn)個(gè)晶體管。他們?cè)谕嫖淖钟螒騿幔俊?/p>

臺(tái)積電發(fā)言人還注意到,密度本身并不能直接轉(zhuǎn)化為芯片尺寸。她說(shuō),布局和其他設(shè)計(jì)規(guī)則都是影響芯片尺寸和競(jìng)爭(zhēng)力的重要因素。

分析師Hutcheson表示:“看到英特爾10nm工藝中的數(shù)字,我震驚了。”

Linley集團(tuán)的David Kanter同意這種觀點(diǎn),他表示:“這是令人印象深刻的密度……但英特爾提出的觀點(diǎn)不到生產(chǎn)就無(wú)法證實(shí)。然而,英特爾的制造工藝會(huì)繼續(xù)領(lǐng)先,問(wèn)題是轉(zhuǎn)化到產(chǎn)品中的是什么。”

Kanter 稱(chēng)贊英特爾的COAG晶體管進(jìn)步。然而,直到公司發(fā)布如何制造COAG器件,才能清楚能否將該設(shè)計(jì)作為一種優(yōu)化接觸電阻的新方法,進(jìn)而區(qū)分其工藝。

對(duì)于新的22FFL,Hutcheson指出,Globalfoundries 和英特爾的代工團(tuán)隊(duì)都面臨著來(lái)自競(jìng)爭(zhēng)對(duì)手在IP(知識(shí)產(chǎn)權(quán))方面的挑戰(zhàn),例如臺(tái)積電在28nm的IP。

英特爾對(duì)于其10nm工藝透露了不同以往的大量細(xì)節(jié)。

FinFETs與 FD-SOI之爭(zhēng)

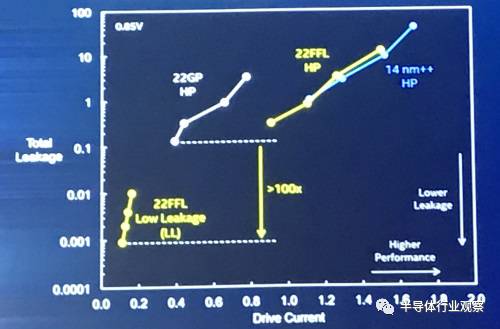

英特爾的22FFL相比于平面28nm具有成本和功耗優(yōu)勢(shì)

英特爾將在今年年底前啟動(dòng)22FFL節(jié)點(diǎn),明確針對(duì)來(lái)自Globalfoundries等公司利用FD-SOI技術(shù)制造的用于移動(dòng)設(shè)備和物聯(lián)網(wǎng)的同類(lèi)芯片。0.5 PDK已經(jīng)準(zhǔn)備就緒,并將出現(xiàn)在6月份的1.0版本中。

相比于同行的28nm,它的工藝包括漏電流小100倍的高性能晶體管和低功耗晶體管。它的目的是通過(guò)簡(jiǎn)化設(shè)計(jì)規(guī)則和用于14nm FinFET的內(nèi)部連接參與28nm的成本競(jìng)爭(zhēng)。

Intel的首席財(cái)務(wù)官Smith最近表示:“我們認(rèn)為這是業(yè)界最簡(jiǎn)單易用的FinFET工藝,服務(wù)大眾的FinFET。”

具體而言,該22FFL工藝支持:

45nm 鰭片間距,

108nm 柵極間距

90nm 采用單一圖案成形技術(shù)的金屬間距

630nm邏輯單元高度

1880 萬(wàn)晶體管/mm2

0.88mm2 SRAM位單元

英特爾的第一代FinFET 22nm節(jié)點(diǎn)的柵極間距和金屬間距明顯松散,分別為90nm和80nm。

Bohr展示了22FFL的漏電流數(shù)據(jù),他提出的包括亞閾值、柵氧化層和結(jié)漏電流。他表示:“所有三個(gè)問(wèn)題都表明節(jié)點(diǎn)對(duì)于任何主流技術(shù)都擁有最小的漏電流。”

英特爾拒絕提供22FL和22nm FD-SOI之間的具體比較。然而,它的內(nèi)部產(chǎn)品有的已經(jīng)被設(shè)計(jì)為22FL,并希望吸引代工客戶(hù)。

英特爾客戶(hù)和物聯(lián)網(wǎng)業(yè)務(wù)和系統(tǒng)架構(gòu)集團(tuán)總裁Murthy Renduchintala說(shuō):“我們今后的路線(xiàn)圖在物聯(lián)網(wǎng)和網(wǎng)絡(luò)等領(lǐng)域?qū)?huì)更加廣闊,這使我們能夠獲得差異化的業(yè)績(jī)。”

Globalfoundries的產(chǎn)品管理高級(jí)副總裁Alain Mutricy回應(yīng)了Intel的22FFL的消息。Mutricy說(shuō):“我們的生產(chǎn)過(guò)程完全符合生產(chǎn)要求,我們看到客戶(hù)需求旺盛,50多個(gè)客戶(hù)積極參與到諸如移動(dòng)設(shè)備、物聯(lián)網(wǎng)和汽車(chē)等高增長(zhǎng)領(lǐng)域。”

在一篇博客中,Mutricy指出,臺(tái)積電和英特爾已經(jīng)宣布了22nm工藝,這發(fā)生在Globalfoundries宣布其FD-SOI計(jì)劃的兩年后。他寫(xiě)道:“這項(xiàng)工作展示了前所未有的創(chuàng)新,它發(fā)生在高級(jí)節(jié)點(diǎn)上,相比于最前沿技術(shù)又邁進(jìn)了一到兩步。”

他補(bǔ)充說(shuō):“德國(guó)德累斯頓的Fab 1工廠(chǎng)完全符合Globalfoundries的22nm工藝生產(chǎn)要求。公司計(jì)劃到2020年將德累斯頓22nm晶圓廠(chǎng)的產(chǎn)能提高40%。”

此外,Globalfoundries于二月份宣布,將于2019年在中國(guó)開(kāi)始合資制造22nm FD-SOI產(chǎn)品,并于去年在德累斯頓進(jìn)行了后續(xù)的12nm FD-SOI工藝計(jì)劃。“我們期望其他公司追隨我們的12FDX領(lǐng)先技術(shù)。”他寫(xiě)道。

臺(tái)積電發(fā)言人說(shuō):“臺(tái)積電的22ULP節(jié)點(diǎn)將推動(dòng)更好的RF元件,它在低功耗物聯(lián)網(wǎng)市場(chǎng)非常具有競(jìng)爭(zhēng)力。”

14nm的更多詳細(xì)信息,代工廠(chǎng)

最后,英特爾提供了關(guān)于其當(dāng)前14nm工藝(即現(xiàn)在的第三個(gè)變種14++)的更多細(xì)節(jié)。英特爾已經(jīng)在14nm節(jié)點(diǎn)生產(chǎn)了三代x86處理器,以及Stratix 10 FPGA。 到今年年底,也將利用14nm節(jié)點(diǎn)生產(chǎn)LTE調(diào)制解調(diào)器。

具體而言,英特爾的14nm節(jié)點(diǎn)使用:

42nm 鰭片間距

52nm 內(nèi)部連接間距

70nm 柵極間距

399nm 單元高度

3750萬(wàn)晶體管mm2

0.050mm2 SRAM單元

英特爾公司互聯(lián)技術(shù)和集成總監(jiān)Ruth Brain表示,英特爾采用自對(duì)準(zhǔn)雙重圖案成形技術(shù),這可以使成本低于使用光刻蝕技術(shù)的其他芯片制造商。

英特爾并沒(méi)有公布任何新客戶(hù)的新生代工服務(wù)。不過(guò),英特爾在代工廠(chǎng)主管領(lǐng)導(dǎo)的活動(dòng)上,在IP和EDA專(zhuān)家小組中間獲得了好評(píng)。

Synopsys首席執(zhí)行官Aart De Geus表示,英特爾的定制代工廠(chǎng)擁有多個(gè)回頭客戶(hù),如果你不能成功交付產(chǎn)品,就永遠(yuǎn)不會(huì)得到它。

“代工廠(chǎng)現(xiàn)在準(zhǔn)備好了迎接黃金時(shí)間”,ARM公司銷(xiāo)售和聯(lián)盟高級(jí)副總裁Will Abbey說(shuō),該公司與英特爾的代工廠(chǎng)合作了大約10個(gè)月。

-

英特爾

+關(guān)注

關(guān)注

61文章

10169瀏覽量

173956 -

摩爾定律

+關(guān)注

關(guān)注

4文章

638瀏覽量

79694 -

晶體管

+關(guān)注

關(guān)注

77文章

9979瀏覽量

140694

發(fā)布評(píng)論請(qǐng)先 登錄

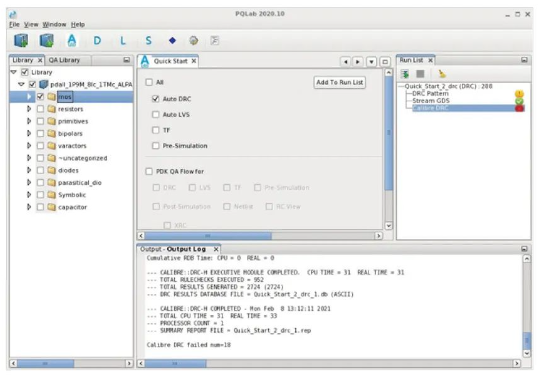

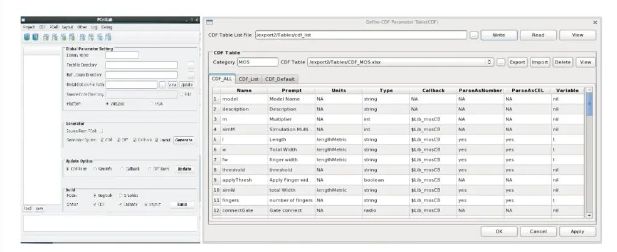

概倫電子先進(jìn)PDK驗(yàn)證平臺(tái)PQLab介紹

概倫電子先進(jìn)參數(shù)化單元庫(kù)開(kāi)發(fā)平臺(tái)PCellLab介紹

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測(cè)

先進(jìn)封裝工藝面臨的挑戰(zhàn)

TRCX應(yīng)用:顯示面板工藝裕量分析

PID發(fā)展趨勢(shì)分析

先進(jìn)陶瓷產(chǎn)業(yè)發(fā)展現(xiàn)狀剖析與發(fā)展建議

先進(jìn)封裝中RDL工藝介紹

CoWoS先進(jìn)封裝技術(shù)介紹

先進(jìn)封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進(jìn)展

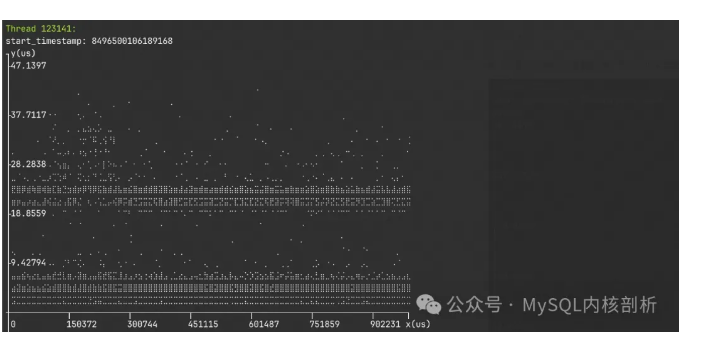

如何使用Intel Processor Trace工具查看任意函數(shù)執(zhí)行時(shí)間

關(guān)于介紹Intel先進(jìn)工藝細(xì)節(jié)的分析和發(fā)展

關(guān)于介紹Intel先進(jìn)工藝細(xì)節(jié)的分析和發(fā)展

評(píng)論