隨著人工智能、高性能計算為代表的新需求的不斷發展,先進封裝技術應運而生,與傳統的后道封裝測試工藝不同,先進封裝的關鍵工藝需要在前道平臺上完成,是前道工序的延伸。CoWoS作為英偉達-這一新晉市值冠軍的GPU中采用的先進封裝技術如今變得愈發重要。

據有關報告稱:CoWoS封裝技術的產能繼續是制約AI芯片供應的最大瓶頸,也是AI芯片需求能否被滿足的關鍵。

DIGITIMES Research最新報告顯示,受云端AI加速器需求旺盛推動,2025年全球對CoWoS及類似封裝產能的需求或將增長113%。

DIGITIMES Research認為,英偉達正在顯著增加高端GPU的出貨量,以滿足其GB200系統的需求,并為臺積電的CoWoS產能下了大量訂單。與此同時,為谷歌和亞馬遜提供ASIC設計服務的博通和Marvell等公司也在不斷增加晶圓訂單。

CoWoS簡介

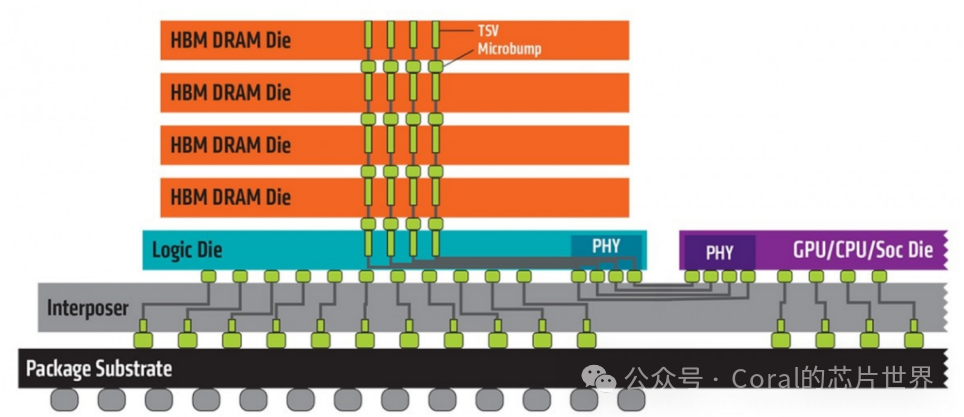

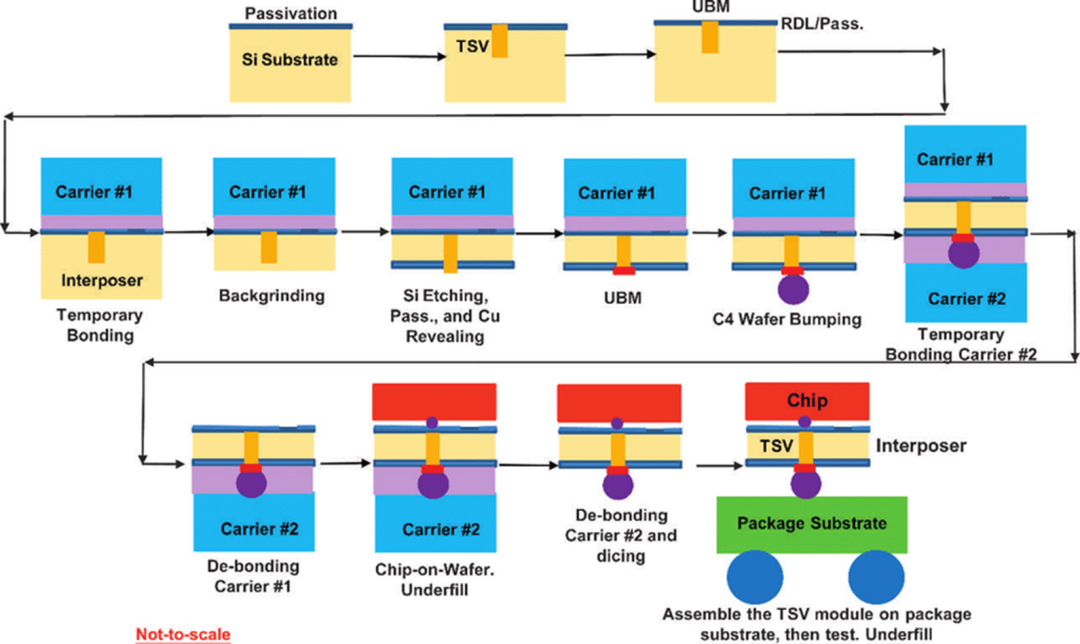

CoWoS 的全稱為Chip on Wafer on Substrate。簡單來說是先將邏輯芯片與存儲芯片一同放在硅中介層上,使用Chip on Wafer(CoW)的封裝制程連接至底層基板上。這種封裝模式可以使多顆芯片可以封裝到一起,通過Si Interposer互聯,達到了封裝體積小,功耗低,引腳少的效果。在高性能計算領域具有巨大的優勢。

目前臺積電提供三種CoWoS封裝服務,分別為CoWoS-S,CoWoS-R,CoWoS-L。隨著英偉達Blackwell系列GPU的大規模生產,臺積電將從2025年第四季度開始從CoWoS-S過渡到CoWoS-L工藝,使CoWoS-L成為臺積電CoWoS技術的主要工藝。

CoWoS S

CoWoS-S平臺為人工智能 (AI) 和超級計算等超高性能計算應用提供一流的封裝技術。該晶圓級系統集成平臺在較大的硅中介層區域上提供高密度互連和深溝槽電容器,以容納各種功能性頂部晶片/晶片,包括邏輯芯片,并在其上堆疊了高帶寬內存 (HBM) 立方體。目前,最大 3.3 倍掩模尺寸(或 ~2700mm2)的中介層已準備好投入生產。對于大于 3.3X 標線尺寸的中介層,建議使用 CoWoS-L和 CoWoS-R 平臺。不同的互連選項提供了更大的集成靈活性,以滿足性能目標。

CoWoS R

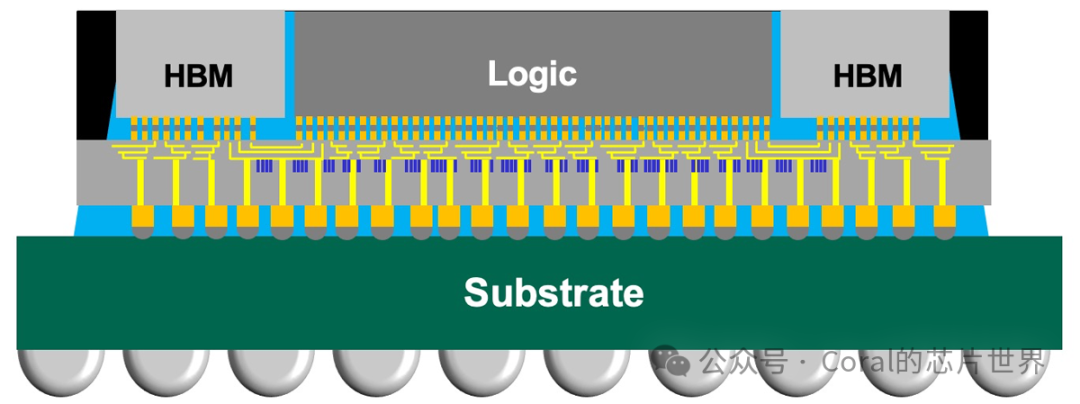

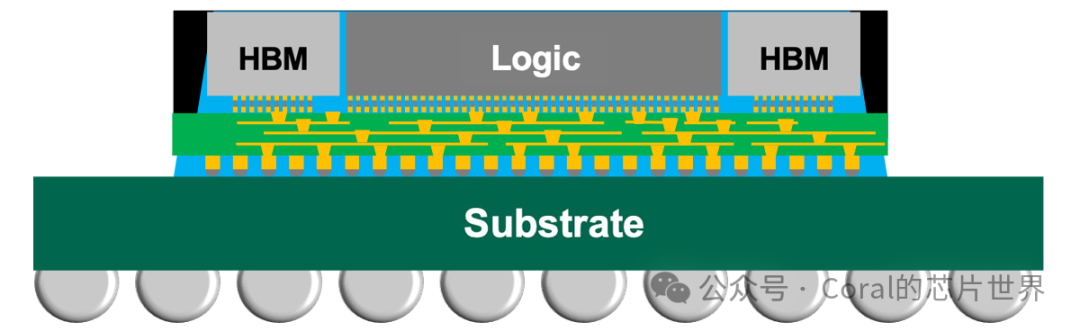

CoWoS-R是 CoWoS先進封裝系列的成員,它利用再分布層 (RDL) 中介層作為片上系統(SoC) 和/或高帶寬內存 (HBM) 之間的互連,以實現異構集成。RDL 中介層由聚合物和銅走線組成,相對靈活。這增強了 C4 接頭的完整性,并允許封裝擴展其尺寸以滿足非常復雜的功能需求。

CoWoS L

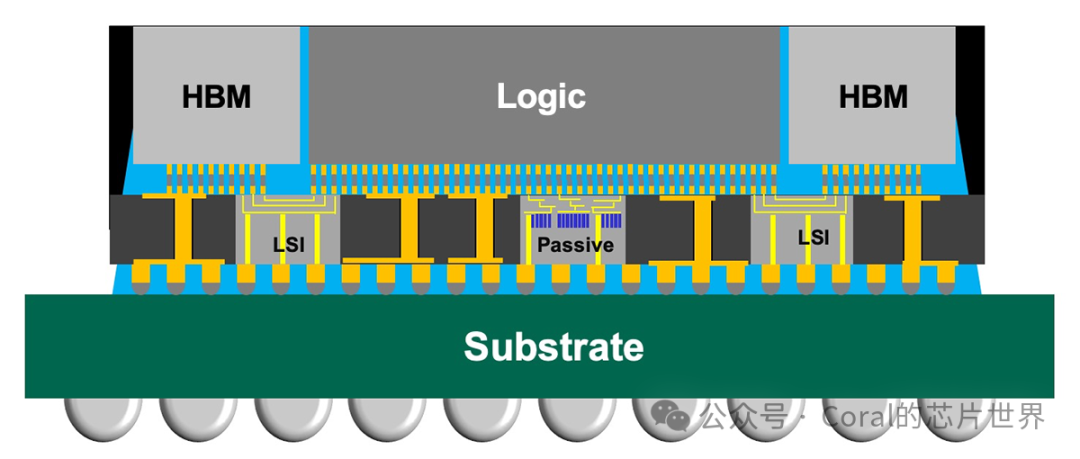

CoWoS-L 是 CoWoS平臺上的后芯片封裝工藝之一。它結合了 CoWoS-S 和 InFO(扇出型)技術的優點,使用中介層和本地硅互連 (LSI) 芯片進行晶粒間互連,并使用 RDL 層進行電源和信號傳輸,從而提供最靈活的集成。

-

CoWoS

+關注

關注

0文章

154瀏覽量

10999 -

先進封裝

+關注

關注

2文章

465瀏覽量

549

原文標題:CoWoS-先進封裝技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

日月光擴大CoWoS先進封裝產能

臺積電超大版CoWoS封裝技術:重塑高性能計算與AI芯片架構

臺積電先進封裝大擴產,CoWoS制程成擴充主力

CoWoS工藝流程說明

CoWoS先進封裝技術介紹

CoWoS先進封裝技術介紹

評論