由于LVDS是一種新技術(shù), 因而在使用時(shí)LVDS和其他邏輯電路的接口設(shè)計(jì)就很重要,設(shè)計(jì)時(shí),應(yīng)注意以下幾個(gè)問題:

(1)根據(jù)系統(tǒng)的工作電源配置情況和需要傳輸?shù)臄?shù)據(jù)電平,合理選用驅(qū)動(dòng)器和接收器芯片,或者根據(jù)接口芯片的情況,對(duì)被傳輸?shù)臄?shù)據(jù)首先進(jìn)行電平轉(zhuǎn)換。

(2) 注意阻抗匹配。根據(jù)接收器輸入端的情況確定是否需要外接100 Ω 電阻,同時(shí)要根據(jù)PCB的板材和參數(shù)合理設(shè)計(jì)驅(qū)動(dòng)器的線輸出阻抗,使其在90~107Ω 范圍內(nèi)。PCB傳輸線要盡可能地短,因?yàn)檫^長(zhǎng)的線路,不但傳輸衰耗加大,降低了傳輸速率,而且阻抗也容易失配,并可能影響到信號(hào)的完整性。

(3) 根據(jù)數(shù)據(jù)傳輸速率和傳輸電纜長(zhǎng)度的關(guān)系,確定合適的電纜長(zhǎng)度以滿足系統(tǒng)的要求。一般地采用LVDS方式傳輸數(shù)據(jù),假定負(fù)載電阻為100Ω,當(dāng)雙絞線長(zhǎng)度為10 m時(shí),傳輸速率可達(dá)400Mb / s;當(dāng)電纜長(zhǎng)度增加為20 m時(shí),速率降為100Mb / s;而當(dāng)電纜長(zhǎng)度為100 m時(shí),速率只能達(dá)到10Mb / s左右。

(4)多數(shù)LVDS接口芯片的使能端在片內(nèi)沒有接上拉或下拉電阻。如果沒有驅(qū)動(dòng)信號(hào)輸入,它們會(huì)不確定地被直接與地或VCC相連,有可能造成邏輯錯(cuò)誤,所以除非有特別說明,接口芯片的使能輸入端不要懸空。

4. 1 LVDS之間的連接

由于LVDS的芯片內(nèi)輸入端一般含有匹配阻抗,因此LVDS驅(qū)動(dòng)器和LVDS接收器可以用一段連接線直接相連。

4. 2 LVPECL 到LVDS的互連

4. 2. 1 直流耦合

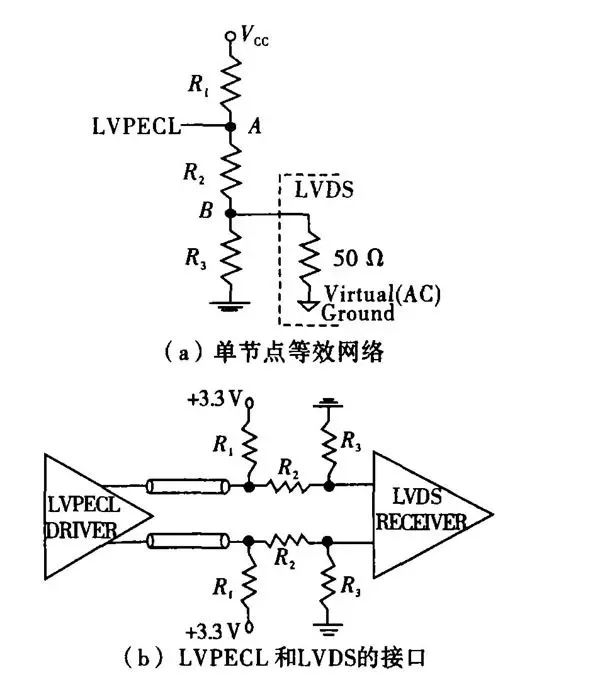

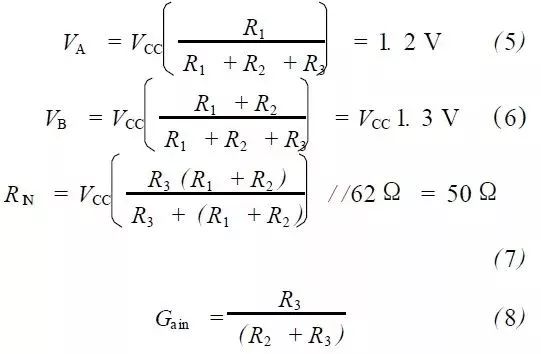

LVDS和LVPECL間的直流耦合要有一個(gè)轉(zhuǎn)移網(wǎng)絡(luò),如圖2所示。首先LVPECL 輸出阻抗最佳是50Ω;另外, LVPECL 電路經(jīng)過衰減網(wǎng)絡(luò)的輸出信號(hào)要在LVDS的輸入范圍內(nèi)。下面的公式可以得到電阻的值。

圖2 LVPECL 和LVDS間的直流耦合

把VCC = 3. 3 V代入(1)式,得R1 = 182Ω, R2= 47. 5Ω, R3 = 47. 5 Ω,另外VA = 1. 13 V, RAC =51. 5Ω, RDC = 62. 4Ω , Gain = 0. 337.若當(dāng)使用該網(wǎng)絡(luò)連接LVPECL 的輸出端和LVDS的輸入端時(shí),那么測(cè)量的共模電壓VA = 2. 1 V, VB =1. 06 V.假定LVPECL 的差分輸出最小是930mV,那么LVDS輸入端的最小電壓就是313 mV,滿足了LVDS 的輸入條件。另一方面, 如果LVPECL的差分輸出最大是1. 9 V,那么LVDS輸入端的最大電壓就是640 mV,同樣滿足LVDS的輸入規(guī)范。

4. 2. 2 交流耦合

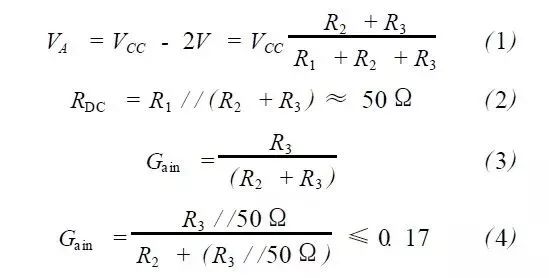

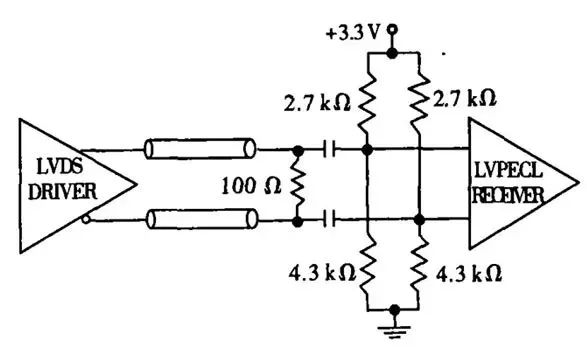

LVPECL 和LVDS間的交流耦合的電路如圖3所示。

圖3 LVPECL 和LVDS間的交流耦合電路

LVPECL輸出通過直流偏置電阻R (142Ω~200Ω )接地。50 Ω 的串聯(lián)電阻來減弱LVPECL的輸出電壓來滿足LVDS的輸入要求。在LVDS輸入端每端接1個(gè)5. 0 kΩ的電阻到地用來減弱共模電壓。

4. 3 LVDS到LVPECL的接口

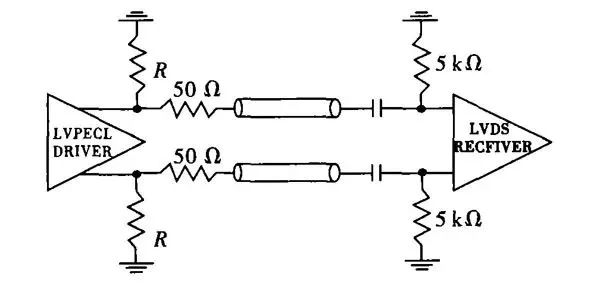

4. 3. 1 直流耦合

直流耦合的電路如圖4所示。

圖4 LVDS到LVPECL 的直流耦合。

這個(gè)電阻網(wǎng)絡(luò)把LVDS直流輸出電壓從1. 2V變到LVPECL的輸入(VCC - 1. 3 V) .這是因?yàn)長(zhǎng)VDS的輸出電壓是參考地,而LVPECL 輸入電壓參考VCC ,這個(gè)網(wǎng)絡(luò)可以使LVDS的輸出不受電壓變化的影響;另外考慮的就是功耗和速度的平衡。

如果R1、R2、R3 選擇低電阻,那么這個(gè)網(wǎng)絡(luò)的時(shí)間常數(shù)和LVPECL的寄生參數(shù)都很小,能夠滿足高速的要求;當(dāng)然由于電阻小了,就有更大的電流流過這些電阻,那么總功耗就大了。這種情況下LVDS的參數(shù)可能會(huì)受到電壓變化的影響。電阻值可以由下列等式求得:

代入VCC = 3. 3 V、R1 = 374Ω、R2 = 249Ω、R3= 402 Ω, 得到VA = 1. 2 V、VB = 2. 0 V、RIN =49Ω, Ga in = 0. 62.LVDS的差分輸出的VP - P =500 mV,信號(hào)在LVPECL輸入端變成310 mVP - P.

電壓變化比PECL的輸入標(biāo)準(zhǔn)小,但滿足LVPECL的輸入要求。

4. 3. 2 交流耦合

LVDS到LVPECL的交流耦合很簡(jiǎn)單,圖5給出了例子,LVPECL的芯片是MAX3867它的片內(nèi)沒有端接電阻。

圖5 LVDS到LVPECL的交流耦合。

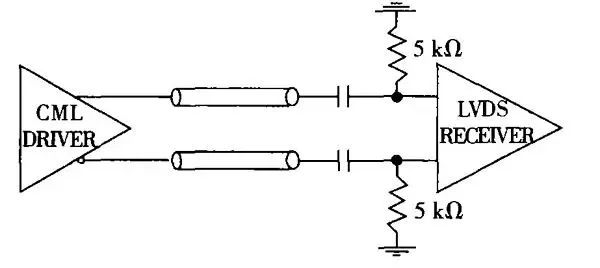

4. 4 CML和LVDS的接口

CML到LVDS的交流耦合如圖6所示,要注意的一點(diǎn)就是CML 的輸出信號(hào)漂移要在LVDS輸入信號(hào)的要求范圍內(nèi)。

圖6 CML到LVDS的交流耦合電路圖。

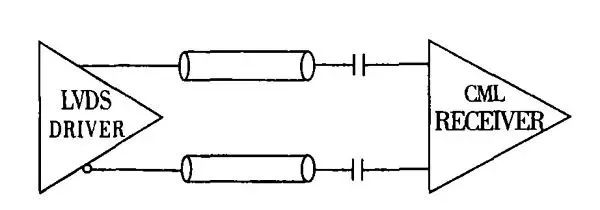

LVDS驅(qū)動(dòng)器連接CML接收器的交流耦合方案如圖7所示。

圖7 LVDS到CML的交流耦合電路圖。

-

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43068 -

lvds

+關(guān)注

關(guān)注

2文章

1076瀏覽量

66859

原文標(biāo)題:華為科普5G雙模手機(jī),一文看懂華為麒麟810

文章出處:【微信號(hào):eda365wx,微信公眾號(hào):EDA365電子論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

邏輯電路芯片-組合邏輯電路芯片-時(shí)序邏輯電路芯片

集成邏輯電路、組合邏輯電路

數(shù)字邏輯電路

同步時(shí)序邏輯電路

異步時(shí)序邏輯電路

數(shù)字邏輯電路

各種邏輯電路簡(jiǎn)介

高速電路信號(hào)完整性分析與設(shè)計(jì)—高速邏輯電路分析

什么是組合邏輯電路,組合邏輯電路的基本特點(diǎn)和種類詳解

組合邏輯電路和時(shí)序邏輯電路比較_組合邏輯電路和時(shí)序邏輯電路有什么區(qū)別

組合邏輯電路和時(shí)序邏輯電路的區(qū)別和聯(lián)系

LVDS與其他幾種邏輯電路的接口設(shè)計(jì)

LVDS與其他幾種邏輯電路的接口設(shè)計(jì)

評(píng)論