米爾XCZU3EG系列開發(fā)板MYD-CZU3EG以超高性能著稱,下面用這款板子做一個演示。

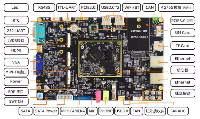

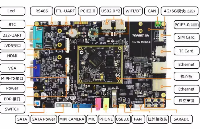

開發(fā)環(huán)境:vivado 2017.4,開發(fā)板型號:米爾MYD-CZU3EG, 主芯片XCZU3EG-1SFVC784。這個系列板子還有4EV,5EV等版本,手里的3EG版本不支持SFP,因此板上相應(yīng)接口(白色部分)是空貼的。

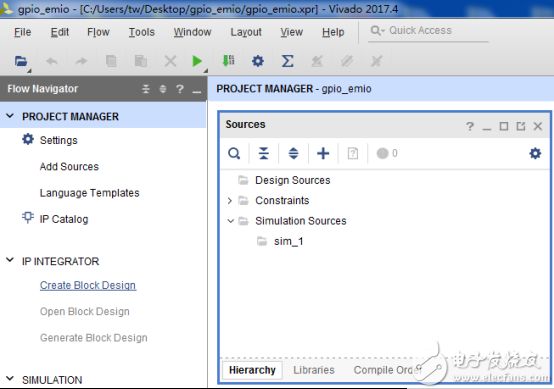

生成的vivado工程(如果不知道如何生成可以參考前面的工程)

Step1新建Block Design

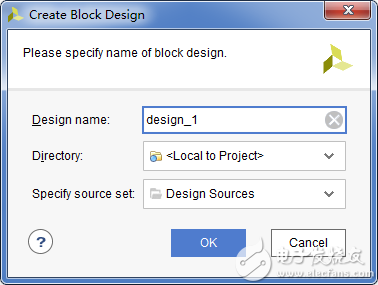

點(diǎn)擊OK

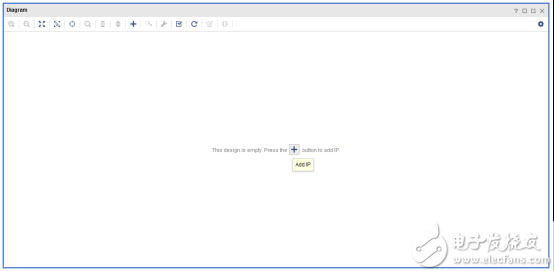

Step2添加PS的IP核并配置

點(diǎn)擊這個Add IP添加IP核

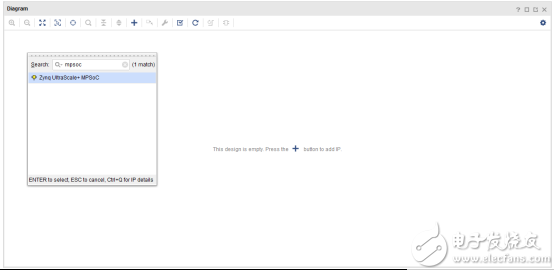

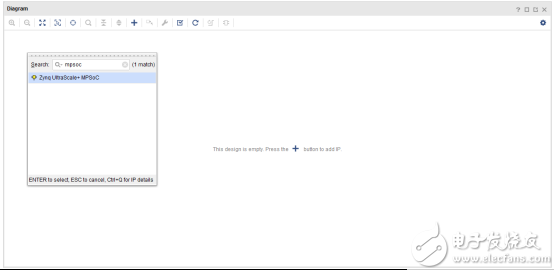

輸入mpsoc,然后雙擊Zynq UltraScale+MPSoC添加mpsoc核

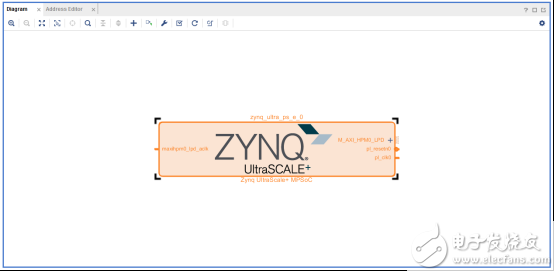

zynq mpsoc核如下圖所示

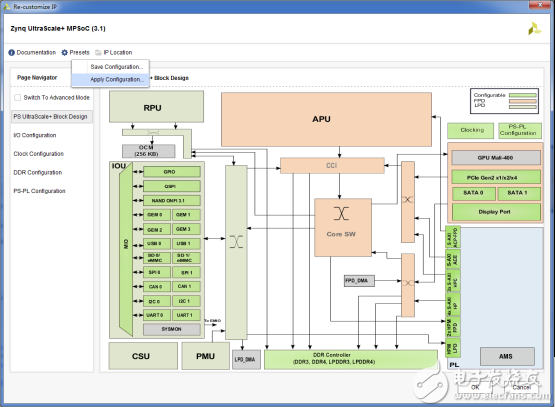

雙擊zynq mpsoc核導(dǎo)入配置文件

Presets-->Apply Configuration

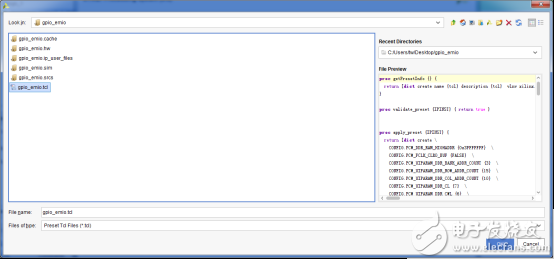

這里導(dǎo)入的是gpio_emio.tcl配置文件

配置完成后,如下圖所示

在gpio管腳上右擊選擇Make External,引出的gpio管腳如下圖所示

……

點(diǎn)擊原文查看具體操作http://www.myir-tech.com/resource/520.asp

發(fā)布評論請先 登錄

XILINX XCZU67DR FPGA完整原理圖

迅為RK3568開發(fā)板驅(qū)動指南GPIO子系統(tǒng)GPIO子系統(tǒng)API函數(shù)的引入

迅為RK3568驅(qū)動指南GPIO子系統(tǒng) GPIO操作函數(shù)實(shí)驗(yàn)

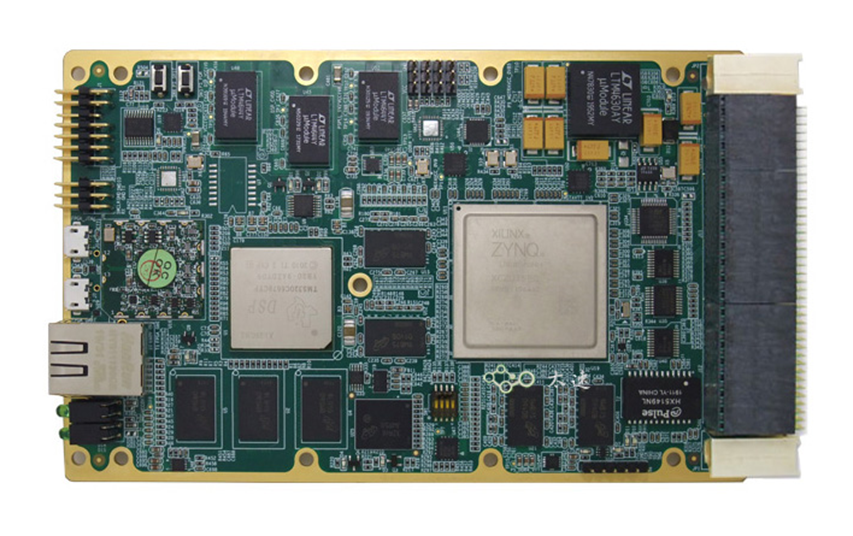

527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

基于小凌派RK2206開發(fā)板:OpenHarmony如何使用IoT接口控制GPIO中斷

基于小凌派RK2206開發(fā)板:OpenHarmony如何使用IoT接口控制GPIO外設(shè)

為什么GPIO配置總是出問題?

單片機(jī)學(xué)習(xí)之GPIO

【北京迅為】iTOP-RK3568OpenHarmony系統(tǒng)南向驅(qū)動開發(fā)GPIO基礎(chǔ)知識

高速圖像處理卡設(shè)計(jì)原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

高速數(shù)據(jù)計(jì)算卡設(shè)計(jì)原理圖:512-基于ZU19EG的4路100G 8路40G的光纖匯流計(jì)算卡

DAC38J84EVM SYNC信號無法通過FMC-LHC接口輸入到FPGA,怎么解決?

SOC GPIO操作

全志模塊設(shè)備開發(fā)之GPIO編程基礎(chǔ)介紹

學(xué)習(xí)資料:520-基于ZU15EG 適配AWR2243的雷達(dá)驗(yàn)證底板 高速信號處理板 AWR2243毫米波板

XCZU3EG開發(fā)筆記之gpio_emio?

XCZU3EG開發(fā)筆記之gpio_emio?

評論