SD存儲卡接口定義了兩種通信模式,SD模式和SPI模式。分析了SD傳輸協議后,給出了一種SD模式設備接口的設計方案。該設計能夠自動解析主機發送的命令并響應,與Flash控制器相連后可以對Flash進行讀寫操作。為了解決數據存取的時序問題,使用了數據緩存技術。FPGA驗證表明,該接口能夠被電腦識別為SD卡,達到了設計目標。

1、引言

SD卡(Secure Digital Card)是“安全數碼存儲卡”的簡稱,于1999年8月由美國SanDisk公司、日本東芝和松下公司共同開發研制成功。隨著數碼產品的廣泛使用,目前SD卡已經成為消費數碼產品設備中最廣泛的一種存儲卡。在手機中,大量的安全增值業務設計就是通過SD接口實現的。SD物理層規范定義了兩種可選擇的通信協議:SD模式和SPI模式。

本文在研究了SD物理層規范的基礎上,實現SD設備接口SD模式的前端設計,并進行了FPGA原型驗證。

2、SD存儲卡接口SD模式介紹的書寫規則

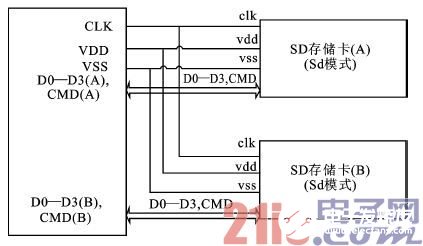

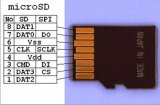

SD卡與控制器之間通過以下9線連接:時鐘CLK、命令CMD、數據D0~D3、電源VDD和兩根地線VSS。其總線拓撲結構如圖1所示。命令和響應在CMD線上傳輸,數據在D0(標準總線模式)或D0~D3(寬總線模式)線上傳輸。

SD卡的所有命令都是6字節長度。一個命令總是以起始位(0)開始,后跟傳輸方向位(1),接下是6位命令索引,然后是32位命令參數,CRC7校驗位,結束位(1)。SD的響應分為R1、R1b、R2、R3、R6、R7六種,其中R1、R1b、R3、R6、R7為6字節長度。R2為17字節長度,用于讀取SD卡的CID/CSD寄存器內容。一個響應總是以起始位(0)開始,后跟一個傳輸方向位(0)。除了R3響應類型,所有的響應都有CRC保護。以一個結束位(1)結束。SD數據傳輸以塊為單位,每個塊總是由數據起始位(0)、數據位、CRC16校驗位和數據結束位(1)組成。

圖1 SD卡SD模式的總線拓撲結構

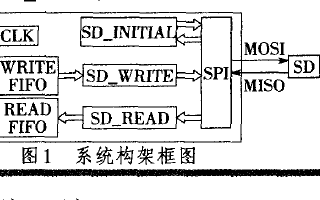

3、整體設計架構

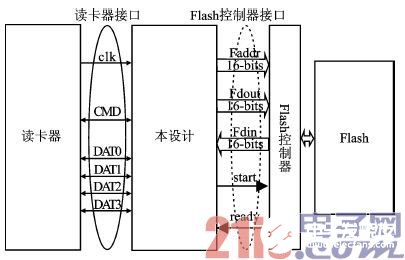

本設計的一端為SD存儲卡標準接口,與讀卡器連接。為了使接口有通用性,另一端與Flash控制器連接,從而達到與不同型號Flash連接的目的。本設計是連接讀卡器和Flash控制器的一個中間模塊。能夠對讀卡器發送的命令進行解析并響應,通過Flash控制器對Flash進行讀寫操作。整體設計方案如圖2所示。

圖2 設計方案

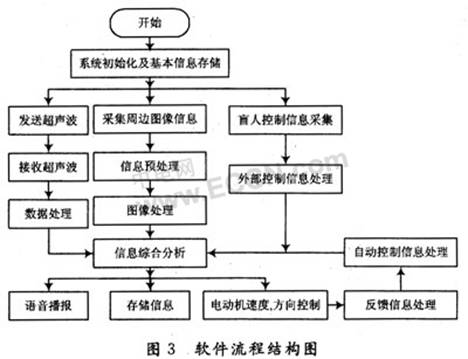

4、 結構設計

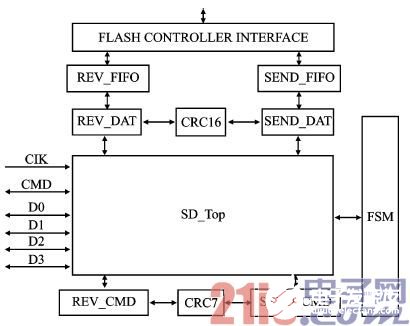

根據SD接口功能,將其進行詳細的劃分,由以下幾個部分組成:命令收發模塊,數據收發模塊,狀態控制模塊和校驗模塊。SD模塊結構如圖3所示。

4.1 命令收發模塊

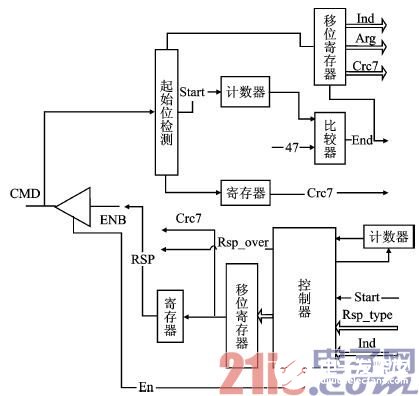

該模塊的結構如圖4所示。命令接收與響應發送都是在命令線CMD上傳輸的,所以該端口為一個三態門,由輸出使能信號En控制是否輸出。命令接收時,首先檢測命令起始位,檢測到起始位后計數器開始工作。當接收完一個完整命令,發出接收完成信號End,分別得到移位寄存器中對應的命令索引,命令參數,命令校驗。命令接收過程中,同時將數據傳給CRC7校驗模塊,用于生成校驗數據。響應發送時,模塊根據狀態控制模塊給出的響應類型產生對應的響應內容,當接收到發送使能信號Start后,給出發送使能信號En,并將響應的內容通過移位寄存器發送出去。響應內容發送完成后給出響應完成信號Rsp_over。

圖3 模塊結構

圖4 命令接收與響應模塊

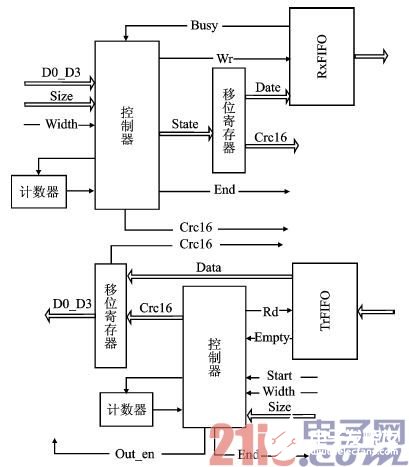

4.2 數據收發模塊

該模塊的結構如圖5所示。數據線也是雙向的。Width信號指明當前數據傳輸模式為標準總線模式或寬總線模式。Size信號指示每個數據塊包含的字節數。該模塊包含兩個數據緩沖,接收緩沖RxFIFO和發送緩沖TrFIFO,數據緩沖位寬16比特,深度為256,這是因為數據塊最大為512字節。數據接收狀態時,首先檢測數據起始位,檢測到起始位后計數器開始工作。接收Size個字節的數據后,接收CRC16校驗位,最后完成數據塊接收,發出接收完成信號End。數據接收過程中,每接收16位數據給出寫入信號Wr,將數據寫入RxFIFO。如果RxFIFO滿,給出Busy信號,主機進入數據發送等待。數據發送狀態時,接收控制器收到Start信號后,開始發出Rd信號讀取TrFIFO數據,并將數據傳給移位寄存器,使能數據輸出控制信號Out_en,移位寄存器根據數據傳輸模式將數據輸出。

圖5 數據收發模塊

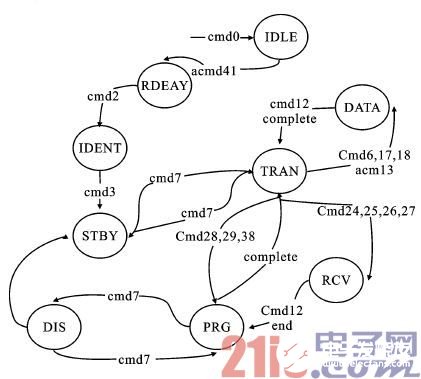

4.3 狀態控制模塊

根據接收模塊傳送的命令編號產生與之對應的命令響應類型,進一步解析接收模塊傳送的命令參數。工作過程共有9個狀態,狀態間的轉移關系如圖6所示。接收到CMD0命令后都會從其它狀態進入到空閑狀態。

圖6 狀態轉移

4.4 校驗模塊

CRC7負責校驗命令收發模塊中的命令和響應;CRC16負責校驗數據收發模塊中的數據。

5、 驗證與測試

開發測試平臺使用的是Altera的CycloneII系列FPGA開發板。開發板上有一個SD接口。測試平臺的實物如圖7所示。開發板可以通過一個PCB板SD接口與電腦SD接口連接,利用電腦對設計進行驗證。

圖7 測試平臺

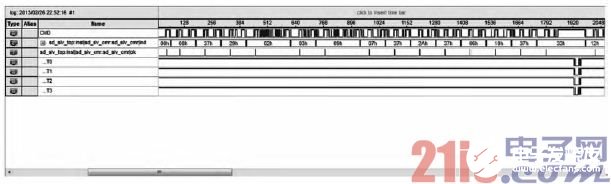

在硬件調試過程中,采用內嵌式邏輯分析儀(SignalTapII)來采集相應的數據波形。圖8是采集到的識別SD卡命令與響應波形圖。從圖中可以看出,該設計可以正確響應主機命令,完成識別過程。

圖9中虛線所圈是將設計下載到FPGA開發板,與電腦相連接后被識別為SD存儲卡標記,可以看出該設計可以被電腦正確識別。

6、結束語

本文實現了一種SD存儲卡接口SD模式IP核的設計與實現。該設計能夠對主機命令進行自動解析和回復,與Flash控制器連接后可以直接對Flash進行讀寫操作。對該設計進行FPGA功能驗證,能夠被電腦識別為SD接口,從而說明的設計的正確性和實用性。利用SYNOPSYS公司的EDA工具對該模塊進行綜合,并進行時序和面積的優化,在SMIC0。18μm工藝下最大工作頻率為100MHz,整個設計綜合后為0.6萬門。

圖8 通信過程

圖9 電腦識別

責任編輯:gt

-

FPGA

+關注

關注

1643文章

21987瀏覽量

615105 -

控制器

+關注

關注

114文章

17019瀏覽量

183261 -

讀卡器

+關注

關注

2文章

432瀏覽量

40137

發布評論請先 登錄

基于FPGA的I2C SLAVE模式總線的設計方案

WIFI無線技術各種熱門設計方案~

基于ARM和FPGA的環形緩沖區接口設計方案

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

求一款在PCI總線上利用FPGA技術設計PCI總線接口的設計方案

采用FPGA技術的智能導盲犬設計方案

多種EDA工具的FPGA設計方案

AT89C52單片機與SD卡實現通訊的設計方案

如何使用FPGA實現SD卡控制器的設計

基于FPGA技術實現SD模式設備接口的設計方案

基于FPGA技術實現SD模式設備接口的設計方案

評論