(文章來源:cnBeta)

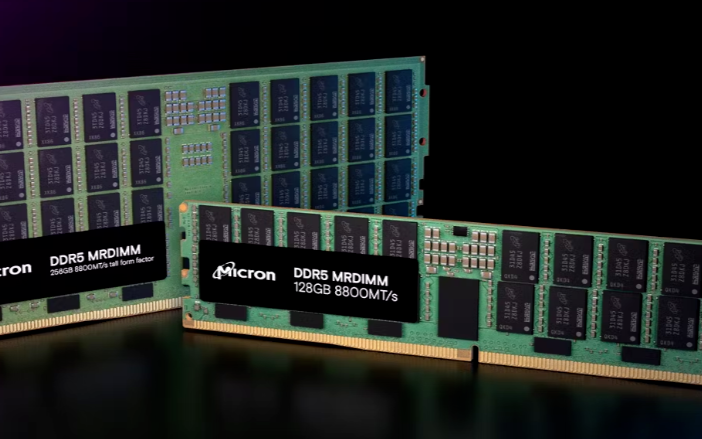

到2024年,美國數據中心市場營收預計將超過 690 億美元。隨著越來越多的企業和個人依賴數據中心的日常使用,軟硬件的可靠性,將成為保持這些服務正常運行的關鍵。實現這一方面的主要目標,就是提高內存的性能。好消息是,美光剛剛宣布已向特定合作伙伴出樣基于 DDR5 的 RDIMM 內存。

作為 DDR4 后續產品,DDR5 意味著“第五代雙倍速率 SDRAM”,并且引入了重大的改進。以同頻的 3200 MT/s 傳輸速率為例,DDR5 的有效帶寬較 DDR4 提升了 1.36 倍。在更高的數據傳輸速率(4800 MT/s)下,DDR5 的性能更是較 DDR4 提升了 1.87 倍。

在快速擴張的數據和計算密集型應用中,以及隨著處理器核心數量的爆發式增長,當前的 DRAM 技術已經面臨嚴重的帶寬短缺。不過美光的最新一代 DDR5 DRAM 技術,能夠將內存性能提升 85%,為應對下一代服務器的工作負荷做好了充分的準備。

在一眾新功能中,占空比調節器(DCA)電路可校正控制器接收的 DQ 和 DQS 信號中出現的小占空比。DQS 間隔振蕩器電路允許控制器監視由于電壓和溫度的變化而導致的 DQS 時鐘延遲變化。輔以改進的 READ 前置、命令和地址訓練模式,芯片選擇、以及寫均衡訓練模式。寫入均衡使得系統能夠補償每個 DRAM 設備的 CK 路徑與 DW 和 DWS 路徑之間的模塊時序差異。借助專用寄存器來讀取訓練模式,并且可獲取命令和地址、芯片選擇和 DQ 引腳內的參考電壓。

現代數據中心還對存儲等部件的可靠性、可用性、可維護性(RAS)提出了更高的要求,但這顆通過 DDR5 的多項功能來實現,比如片上錯誤校正碼(ECC)。

在從 DDR5 器件輸出數據之前,可先在 READ 命令期間執行校正,以減輕系統的錯誤校正負擔。設計伊始,DDR5 就已經考慮到了 Hamming 代碼的 EDD 實現。DDR5 SDRAM ECC 具有錯誤檢查和清除(ECS)功能,可讀取內部數據、并在發生錯誤時寫回校正后的數據,而且支持手動或自動執行。打包后修復(PPR)功能也支持軟(sPPR)或硬(HPPR)模式,分別對應永久性修復和臨時性修復,且 PPR 具有跟蹤資源可用性的能力。啟動時,每個 DRAM 設備可確定各個存儲體中 PPR 資源的可用性,然后設置一組模式寄存器來追蹤信息。

綜上所述,美光為 DDR5 SDRAM 產品組合提供了眾多功能,旨在為數據中心客戶帶來更高的性能和更多的創新。

(責任編輯:fqj)

-

內存

+關注

關注

8文章

3117瀏覽量

75149 -

美光

+關注

關注

5文章

725瀏覽量

52311

發布評論請先 登錄

DDR4漲價20%,DDR5上調5%!

德明利DDR5內存助力AI PC時代存儲性能與市場增長

DDR3、DDR4、DDR5的性能對比

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

美光發布新型CUDIMM與CSODIMM內存產品

Rambus推出DDR5客戶端時鐘驅動器

Rambus推出DDR5客戶端時鐘驅動器,將業界領先的內存接口芯片產品擴展到高性能 PC領域

DRAM大廠第三季DDR5價格大幅上調

DDR5內存面臨漲價潮,存儲巨頭轉向HBM生產

Introspect DDR5/LPDDR5總線協議分析儀

DDR5 MRDIMM內存標準將發,存儲廠商方案先行

0706線下活動 I DDR4/DDR5內存技術高速信號專題設計技術交流活動

美光DDR5技術可助力服務器的內存性能提升85%

美光DDR5技術可助力服務器的內存性能提升85%

評論