能夠顯示開路狀態的邏輯筆(一)

如圖所示為能夠測試和顯示包括高、低電平和開路狀態的邏輯筆。

能夠顯示開路狀態的邏輯筆(二)

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

邏輯筆

+關注

關注

0文章

14瀏覽量

14870 -

開路電路

+關注

關注

0文章

9瀏覽量

7305

發布評論請先 登錄

相關推薦

熱點推薦

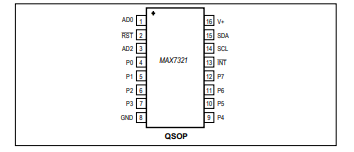

MAX7321 I2C端口擴展器,具有8路漏極開路I/O技術手冊

MAX7321 2線串行接口外設具有8個漏極開路I/O口,可選擇內部上拉和瞬態檢測功能。每個端口均可以配置成邏輯輸入和漏極開路輸出端口。端口具有+6V過壓保護,與電源電壓無關。

器件連續監視

基于BLE技術 智能手寫筆解決方案:改變你的書寫體驗PTR5415

,這種無線連接極大地簡化了使用手寫筆的流程,使用戶能夠輕松將手寫內容傳輸到移動設備上,并進行保存、編輯、共享等操作。

功能特性:

1、高精度書寫:智能手寫筆配備了精準的書寫感應技術,能夠

發表于 03-11 17:50

TAS6424E-Q1: DC為什么開機狀態下,開路時候電阻值這么小?

在車機開機狀態下,斷開喇叭,tas6424的DC診斷寄存器沒有讀到OL開路的錯誤信息,0xc和0xd寄存器,對應OL的標志位沒有被置1.此時量取功放輸出端的電阻,阻值從0-30Ω變化跳動。按照

發表于 09-30 06:32

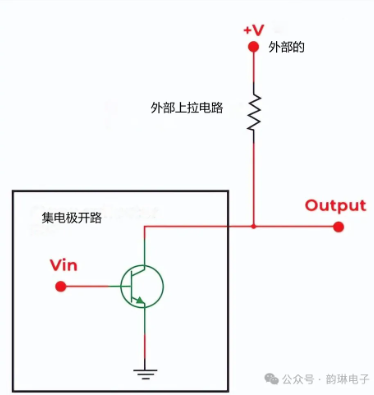

集電極開路的作用有哪些

集電極開路邏輯作為一種獨特的輸出方式,其輸出端可以吸收電流,但無法提供電流。這一特性使得多個集電極開路輸出能夠輕松地連接在同一條公共信號線上,而不會發生相互干擾。這種設計不僅節省了布線

集電極開路的基本概念與原理

,顧名思義,是指晶體管的集電極處于未連接狀態。在這種配置下,集電極開路仿佛一個懸空的開關,既不接地也不直接連接到電源。然而,正是這種“懸浮”狀態,賦予了集電極開路獨特的靈活性和廣泛的應

時序邏輯電路的描述方法有哪些

時序邏輯電路是數字電路中的一種重要類型,它具有存儲功能,能夠根據輸入信號和內部狀態的變化來改變其輸出。時序邏輯電路廣泛應用于計算機、通信、控制等領域。本文將介紹時序

時序邏輯會產生鎖存器嗎

Logic Circuits)不同,它能夠在任何給定時刻的輸出不僅取決于當前的輸入,還取決于電路過去的輸入(即電路的當前狀態)。這種記憶功能使得時序邏輯電路能夠處理更復雜的問題,如存

時序邏輯電路中如何判斷有效狀態和無效狀態

在時序邏輯電路中,有效狀態和無效狀態的判斷是電路分析和設計的重要環節。有效狀態是指電路在實際工作過程中被利用到的狀態,它們構成了電路的有效循

組合邏輯電路輸出狀態取決于哪些因素

組合邏輯電路的輸出狀態主要取決于以下因素: 核心因素 輸入信號的現態 :組合邏輯電路的輸出狀態在任何時刻僅由其當前輸入狀態的

開路電壓除以短路電流是等效電阻嗎

某一點與參考點之間的電壓,當電路處于開路狀態時,即電路中沒有電流流過時,測量得到的電壓值。開路電壓是電路中電源的輸出電壓,它反映了電源的電勢差。 短路電流是指在電路中,當兩個導體之間的電阻為零時,通過這兩個導體

開路電壓和工作電壓的區別是什么

負載(即電路處于開路狀態)時,電路兩端的電壓。這個概念在電源、電池、發電機等能量轉換設備中尤為重要。 1.1 開路電壓的特點 無負載 :開路電壓是在沒有連接任何負載的情況下測量的電壓。

組合邏輯電路邏輯功能的測試方法

一、引言 組合邏輯電路是數字電路中的重要組成部分,它僅由邏輯門電路(如與門、或門、非門等)和輸入/輸出端組成,不包含任何存儲元件。組合邏輯電路的輸出僅取決于當前的輸入信號,與電路的歷史狀態

能夠顯示開路狀態的邏輯筆

能夠顯示開路狀態的邏輯筆

評論