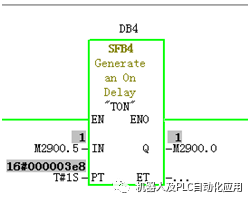

SFB 4 "TON"使信號上升沿延遲時間PT。定時器只在STARTUP和RUN模式下運行。

IN輸入的上升沿會導致時間PT用完后輸出Q出現上升沿。隨后Q將保持置位狀態,直到IN輸入再次變為0。如果IN輸入在時間PT用完前變為0,輸出Q將保持其設置0不變。

ET輸出提供IN輸入的上一上升沿后過去的時間。其最大值為PT輸入的值。IN輸入變為0時將復位ET。

操作系統會在冷啟動期間重置SFB4 "TON"的背景。如果希望在暖啟動后初始化此SFB的背景,必須在OB100中使用PT = 0 ms調用SFB 4。如果此SFB的背景位于另一個塊中,可以,例如通過初始化更高級別的塊,重置這些背景。

例如:

TON_FrgK90_Zutritt(IN:= (ST_BA.K90_AnfoZutritt And FrgK90_Zutritt),PT:=T#2s);

-

信號

+關注

關注

11文章

2851瀏覽量

78204 -

定時器

+關注

關注

23文章

3298瀏覽量

118739

原文標題:SFB 4 "TON"生成接通延遲

文章出處:【微信號:gh_a8b121171b08,微信公眾號:機器人及PLC自動化應用】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

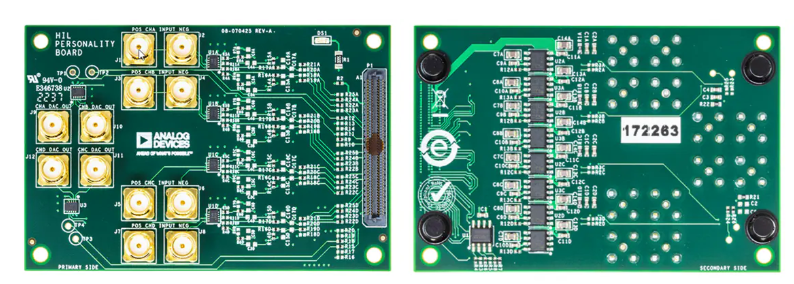

Analog Devices Inc. EVAL-CN0584-EBZ低延遲開發套件(LLDK)特性/布局/框圖

浪涌保護器使用SCB和SFB后備保護模式的分析及應用方案

互連層RC延遲的降低方法

超125款游戲和應用支持DLSS 4多幀生成

求助,為什么在PdStack中檢測到Attach和打開Vbus之間會有很長時間的延遲?

HMC910LC4B寬帶模擬時間延遲器件,采用SMT封裝,DC-24GHz技術手冊

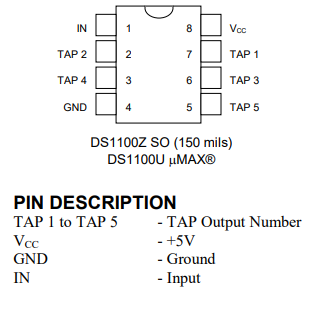

DS1100 5抽頭、經濟型定時單元(延遲線)技術手冊

Python中的迭代器與生成器

PGA900 TEST_MUX_DAC_EN位清零不會”Connects DAC output to TOP/TON pins“,仍然是是2.5V為什么?

PCIe延遲對系統性能的影響

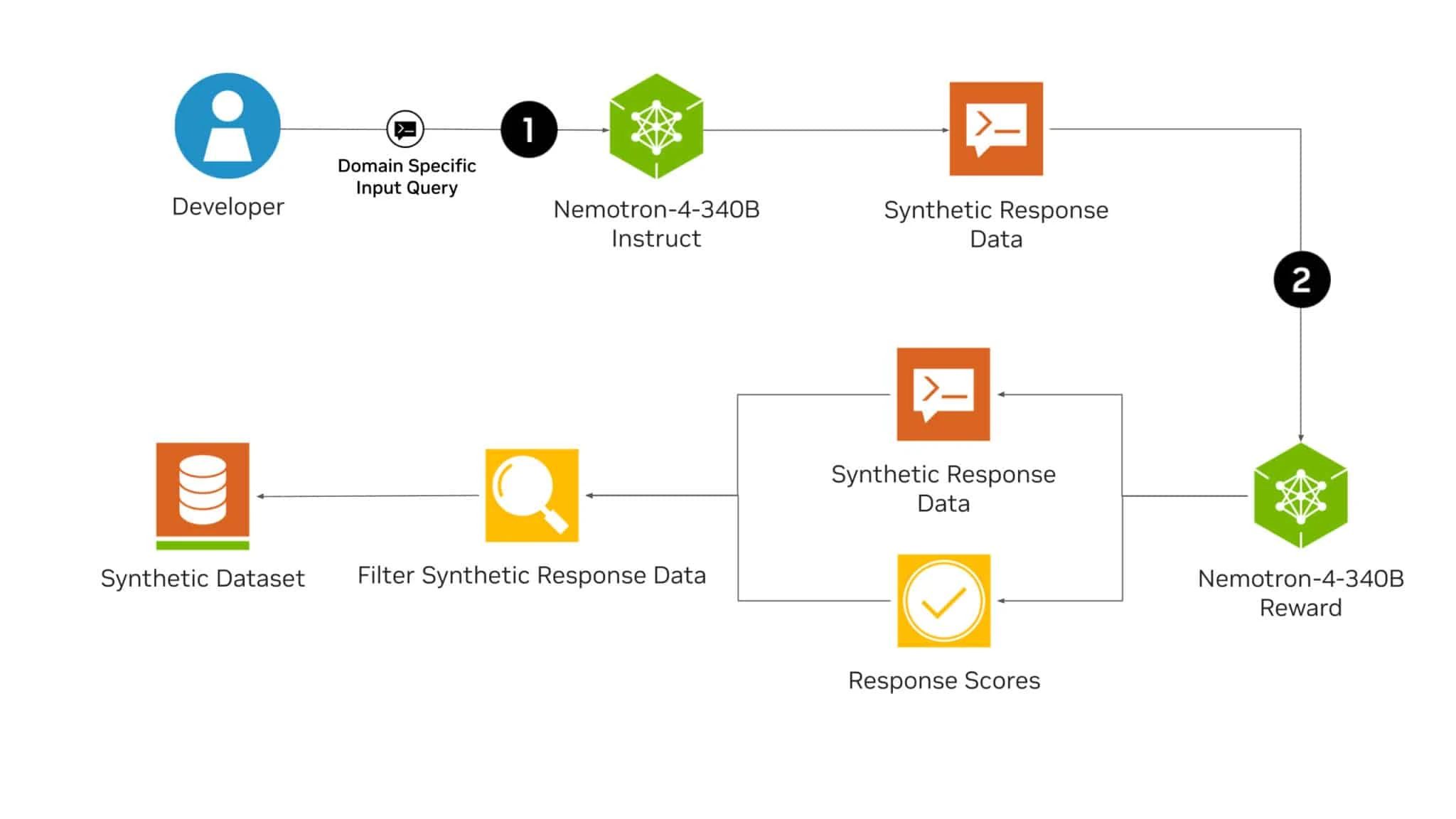

NVIDIA Nemotron-4 340B模型幫助開發者生成合成訓練數據

SFB 4 "TON"生成接通延遲

SFB 4 "TON"生成接通延遲

評論