這一篇主要講講ROMRAMFlash的一些零碎知識點,網上也能找到很多資料。

1、ROM1.1 概述只讀存儲器(Read-only memory, ROM),當然從廣義上來講,也有一些器件,例如Flash,EPROM等等,通過某種手段可以編程的,也屬于ROM的范疇的。ROM一般用在一些程序的存儲和數據的存儲,這里程序多半是比較固定的程序(Firmware,固件,一種跟硬件強相關的程序,例如驅動等等),這里的數據多半是固化的表項,查找表等等不會怎么改變的表項。1.2 基本原理HDL設計中,對于小ROM,深度和位寬都不大,一般使用組合邏輯就可以做一個ROM。如果數據比較大,比如1K*4B這種,就換一種ROM,使用標準單元Mask ROM,來做存儲,如下圖所示。百度百科對MASK ROM的定義,是制造商為了要大量生產,事先制作一顆有原始數據的ROM或EPROM當作樣本,然后再大量生產與樣本一樣的 ROM,這一種做為大量生產的ROM樣本就是MASK ROM,而燒錄在MASK ROM中的資料永遠無法做修改。

1.3 分類

一種是真的寫了就沒法改的ROM;一種是可以寫一次的ROM(one-time Programmable read-only memory),使用的高壓反熔絲技術;一種是可擦出的能、能寫多次的ROM(Erasable programmable read only memory),使用紫外線擦除;一種是電擦除的EEPROM(Electrically Erasable programmable read only memory,EEPROM),再到后來東芝搞的Flash。工業(yè)界第一種ROM和最后一種的Flash用的比較多。

二、Flash1.1 原理非遺失性的存儲,是在ROM的基礎上演進出來的。目前主流是NAND和NOR。模擬的團隊來做flash。可以任意地址訪問。對于連續(xù)地址讀訪問,NAND和NOR的帶寬差距不大。NAND是存儲塊訪問,NOR可以Byte訪問。總的來說,NOR特點就是比較細的訪問,基本啟動程序放NOR中,穩(wěn)定性和可靠性也稍微高一些;NAND訪問數據塊比較好,通常數據放NAND中,而且成本也較低。

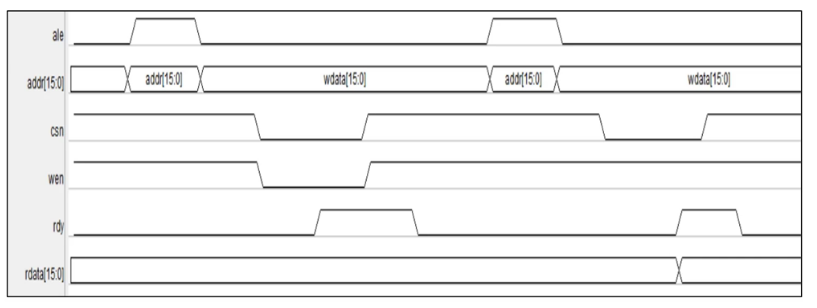

圖:NOR Flash的時序

ale: address lock enable;一般Flash不會直接集成到芯片中,如果集成在芯片外面,IO數量增加,NOR解決辦法就是數據和地址復用,當ale為高的時候,addr上走的是地址,當ale為低且csn為低的時候,addr上走的是數據。 wen:write enable;用于指示讀還是寫。 rdy:對于芯片和FLash分離,因為是異步接口,所以使用rdy信號用來握手。對于MCU來講,如果把小的NOR flash集成到芯片內部,就可以直接使用同步接口,也就是SRAM的接口。

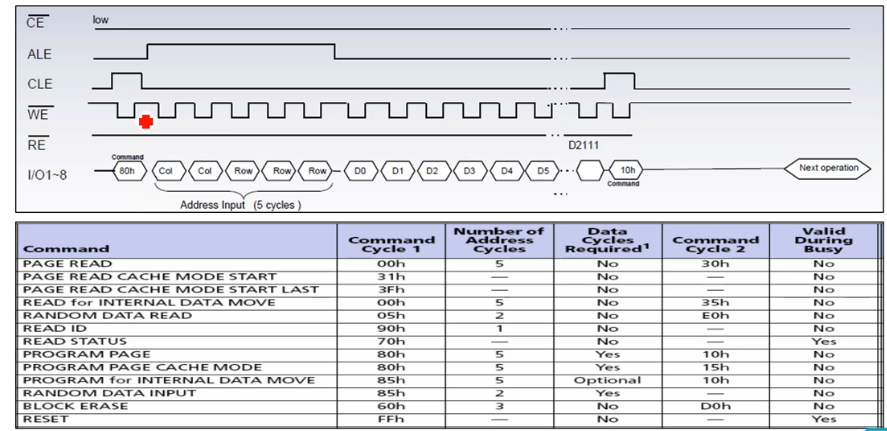

圖:NAND Flash時序

CLE:Chip Lock Enable;

可以看到NAND也是數據和地址線復用的。NAND可以大塊的數據讀寫,多了些Command。NAND Flash在MCU中的比較少。Flash跟ROM和RAM不同,不想數字的可以直接用工具生成,這個需要模擬團隊自己做。

3、RAM 1.1 基本概念Static Random Access Memory,靜態(tài)的,隨機的訪問。靜態(tài)的,不用刷新,不像DRAM需要隨時刷新,但是SRAM沒有DRAM的集成度高,面積比較大。另外,速度和功耗比DRAM好一些。

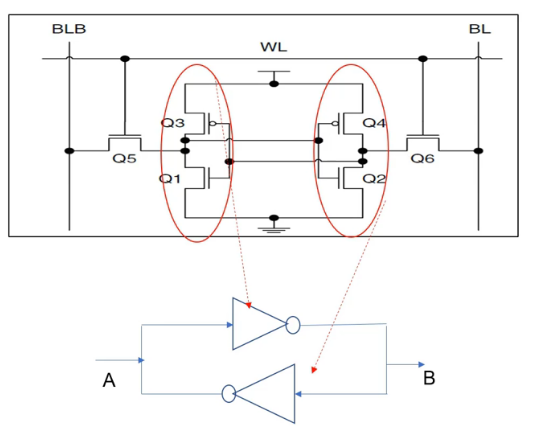

圖:存儲一個bit的SRAM的結構

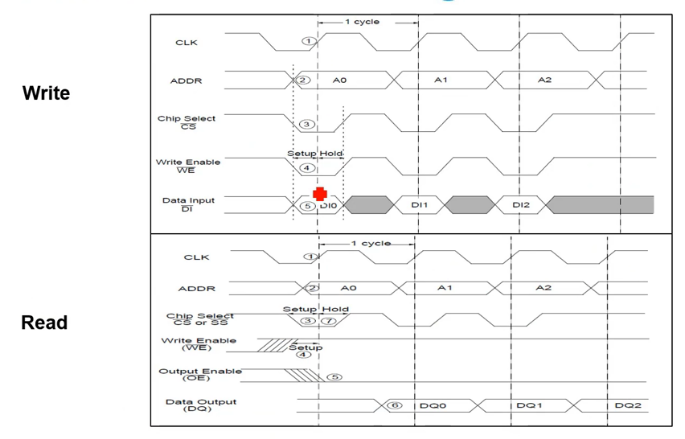

6個CMOS管子組成一個SRAM單元,Q1和Q3組成反相器,Q2和Q4組成反相器,兩個反相器組成一個環(huán)路,這樣,只要不掉電,這個邏輯環(huán)就不會變,跟觸發(fā)器原理有點類似。Q5用于控制輸入,Q6用于控制輸出,兩個管子相當于輸入和輸出的開關。1.2 分類single port SRAM:不會發(fā)生讀寫沖突,因為之后一個端口,要么讀,要么寫;盡量做到先寫后讀,或者初始化再讀,否則讀出來的數據有可能不對(原因是SRAM的軟失效)。對于軟失效,可以加一個ECC校驗,例如寸10bir,其中2bit是校驗位。 Two port SRAM:FOGA的讀寫沖突允許,但是ASIC不可以,在同一個時刻,讀地址和寫地址不要一樣。FIFO一般是TP SRAM。 Dual port SRAM:也是兩個端口A、B,可以A讀B寫,也可以A寫B(tài)讀,不在局限于只能誰讀誰寫。可靠性,面積和率都不是很好。 工程上,使用兩個SRAM,做乒乓操作,實現TP SRAM的功能,一個讀的時候,另外一個寫。兩個SRAM加起來面積可能比TP SRAM小一些。對于幾百幾K的bit位,直接用D觸發(fā)器來存儲比較好。1.3 接口SRAM有一個需要注意下,就是Redundancy接口,用于擴展SRAM的,在比較的大的memory中會用,例如cache,這個接口可選的。用法的話,舉個例子這個就是說,當SRAM中有一塊壞掉了,這個時候就在尾部在接一塊SRAM存儲,就把壞塊的地址映射到新加的存儲塊中,這個時候就要用的Redundancy了。1.4 時序對于Single port SDRAM的時序,如下圖:

讀是在一個時鐘周期完成,如果是連續(xù)寫,紅點處,write enable是可以一直拉低的;讀的話,是要在下一個時刻才能采到數據,注意下。

-

NAND

+關注

關注

16文章

1721瀏覽量

138055 -

存儲器

+關注

關注

38文章

7644瀏覽量

167129 -

ROM

+關注

關注

4文章

578瀏覽量

87263

原文標題:MCU存儲系統

文章出處:【微信號:mcugeek,微信公眾號:MCU開發(fā)加油站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

C51單片機及C語言知識點必備秘籍

電機選型計算公式與知識點匯總

電氣工程師必知必會的100個電?知識點分享

華邦電子安全閃存關鍵知識點

Docker-鏡像的分層-busybox鏡像制作

Aigtek功率放大器應用:電感線圈的知識點分享

串口設計一些關鍵注意點!千萬別踩雷!

一文詳解信號的回流路徑

后悔沒有早點看到:天線設計中的知識點!

分享一些常見的電路

ROMRAMFlash的一些零碎知識點

ROMRAMFlash的一些零碎知識點

評論