在圖像處理系統(tǒng)中常需要對圖像進(jìn)行預(yù)處理。由于圖像處理的數(shù)據(jù)量大,對于實時性要求高的系統(tǒng), 采用軟件實現(xiàn)通常難以滿足實時性的要求。Altera的QuartusⅡ作為一種可編程邏輯的設(shè)計環(huán)境,由于其強大的設(shè)計能力和直觀易用的接口,越來越受 到數(shù)字系統(tǒng)設(shè)計者的歡迎。QuartusⅡ支持Altera的IP核,包含了LPM/Megafunctions宏功能模塊庫,設(shè)計者只需要選取設(shè)置這些 功能模塊的相關(guān)參數(shù)就可以在程序中調(diào)用,從而使用戶可以充分利用成熟的模塊,大大簡化了設(shè)計的復(fù)雜性,加快了設(shè)計速度。

拉普拉斯算子是一種重要的圖像增強算子,它是一種各向同性濾波器,即濾波器的響應(yīng)與濾波器作用圖像的突變方向無關(guān),而且實現(xiàn)簡單,被廣泛用于圖像銳化和高頻增強等算法中。在此,提出一種使用QuartusⅡ開發(fā)環(huán)境的Megafunctions功能模塊實現(xiàn)拉普拉斯算子的方案,可以做到實時增強圖像的高頻細(xì)節(jié)。

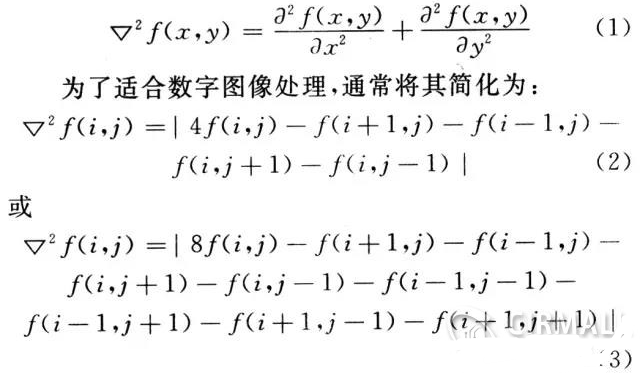

1 、Laplacian算子介紹拉普拉斯算子是各向同性線性算子,二元函數(shù)f(x,y)的拉普拉斯變換定義為:

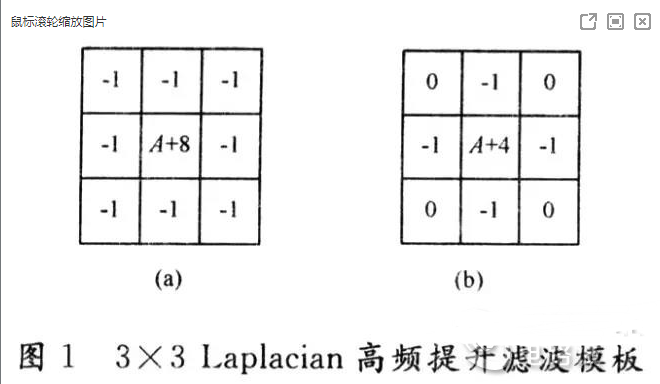

基本高通濾波模板中所有系數(shù)的和為0,如果在模板所覆蓋的區(qū)域內(nèi)像素的灰度值都相同或者灰度值的變化較為緩慢.則模板的輸出為0或輸出很小。人們常用的高通提升濾波方法,就是將原圖像乘以一個放大因子A,再減去低通濾波圖像。高通提升濾波可以表示為: 高通提升濾波圖像=A×原圖像-低通濾波圖像=(A-1)×原圖像+原圖像-低通濾波圖像=(A-1)×原圖像+高通濾波圖像

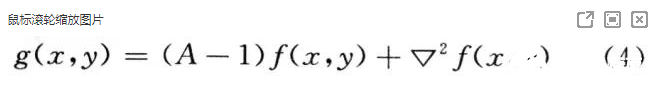

即:

式中:當(dāng)A=1時,高通提升濾波就是基本的高通濾波;當(dāng)A》1時,部分原圖像被加到高通濾波的結(jié)果上,這就恢復(fù)了部分高通濾波中丟失的低頻成分。因此,經(jīng)過高通提升濾波的圖像與原圖像更加相像,同時又對圖像的邊緣進(jìn)行了增強。進(jìn)行模板卷積的主要步驟為:

(1)將模板在圖中漫游,并將模板中心與圖中某個像素位置重合;

(2)將模板上系數(shù)與模板下對應(yīng)像素相乘;

(3)將所有乘積相加;

(4)將和(模板的輸出響應(yīng))賦給圖中對應(yīng)模板中心位置的像素。當(dāng)模板遍歷圖像中的每個像素就得到圖像濾波結(jié)果。實現(xiàn)Laplacian高通提升濾波的模板如圖1所示。

文獻(xiàn)[2]的實驗證明,使用圖1(a)所示掩模能得到更好的銳化效果,所以在硬件實現(xiàn)時使用該掩模。實驗中取A=1。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22020瀏覽量

617144 -

Laplacian

+關(guān)注

關(guān)注

0文章

3瀏覽量

6972

發(fā)布評論請先 登錄

如何使用USB中斷傳輸方法訪問FPGA?

Linux系統(tǒng)中通過預(yù)留物理內(nèi)存實現(xiàn)ARM與FPGA高效通信的方法

利用FPGA實現(xiàn)USB 2.0通信接口

基于FPGA實現(xiàn)圖像直方圖設(shè)計

FPGA驅(qū)動AD芯片之實現(xiàn)與芯片通信

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

FPGA門數(shù)的計算方法

基于 DSP5509 進(jìn)行數(shù)字圖像處理中 Sobel 算子邊緣檢測的硬件連接電路圖

如何在FPGA中實現(xiàn)按鍵消抖

摩爾線程攜手智源研究院完成基于Triton的大模型算子庫適配

分享幾個用FPGA實現(xiàn)的小型神經(jīng)網(wǎng)絡(luò)

Laplacian算子的FPGA實現(xiàn)方法

Laplacian算子的FPGA實現(xiàn)方法

評論