電子設計自動化—— Electronic Design Automation,簡稱EDA。作為芯片設計最上游,EDA軟件的工作,是要在芯片那么小的空間進行布局布線、版圖、設計規則檢查等,好比在米粒上刻出航空母艦模型。

在EDA問世之前,設計人員必須通過手工完成電路設計和布線等基礎工作。隨著芯片集成度提高和性能的多元化,令芯片設計要求也變得越來越復雜,一個指甲蓋大小的芯片上要集成數百億顆晶體管,這樣細微且宏大的工程,早已不是單純人力范圍所能覆蓋,EDA的重要性不言而喻。

根據應用場景的不同,EDA工具的使用主要分為設計、驗證和制造三大類。大規模集成電路設計復雜性的提升,使芯片驗證面臨資金與時間的巨大挑戰。早期開發者想驗證芯片的設計是否符合預設,只有等待極其漫長的模擬結果,或是等待流片成果,而一旦結果不如預期,不管是再次模擬或是二次流片,都將產生極高的成本。因此,當Xilinx推出現場可編程邏輯門陣列(FPGA)時,開發者即可通過用FPGA板拼湊出有效的流程來對設計進行驗證,FPGA原型驗證這一解決方案就此應運而生,這一比流片便宜、比仿真要快的方式,已成為開發者檢驗設計有效性的不二選擇。

01基于FPGA的物理原型驗證

就像是建筑師設計完樓房、開始建造前,需要通過模型去測試防震、防風、結構強度等各種參數,芯片和系統開發者也需要在流片前對設計進行“原型驗證”——就是模仿真實軟件應用條件下的芯片和系統表現是否滿足了實際應用場景要求。

FPGA的應用范圍廣泛,通信、計算、控制等領域等都有它的建樹,并且由于其具有內部電路可重構的特點,幾乎可以完全映射芯片的邏輯設計,也被當作一種性價比優越的芯片驗證基礎設施。FPGA原型驗證已是當前原型驗證的主流且成熟的芯片驗證方法——它通過將RTL移植到現場可編程門陣列(FPGA)來驗證ASIC的功能,并在芯片的基本功能驗證通過后就可以開始驅動的開發,一直到芯片Tape Out并回片后都可以進行驅動和應用的開發。當芯片回片后,應用程序可以直接基于FPGA版本的驅動來進行簡單的適配,即可以應用到SoC芯片上,將SoC芯片Time-to-Market的時間控制的很完美。除了可以提前進行軟件開發外,從成本上來說,FPGA原型驗證是一個性價比很高的驗證手段,在價格上可以說非常的親民。更重要的FPGA原型在運行速度上也技高一籌:它在速度上當然比EDA驗證高了好幾個數量級,即使是與Emulator相比,其性能上也有碾壓式的優勢。在這種種優勢中,“流片前的軟硬件協同開發”是FPGA物理原型驗證最不可替代之處,提早基于該技術平臺進行軟件驅動開發和應用開發,對于縮短最終芯片Time-to-Market周期意義重大。

在軟硬件深度定制化、要求芯片到應用的一站式交付的今天,FPGA原型平臺的重要性進一步提升。2000年,一家創立于瑞典的公司Hardi Electronics正式推出一款基于FPGA的原型系統HAPS,HAPS可以通過多種方式快速組裝ASIC原型系統,為客戶在關鍵驗證階段節省數月的時間。2007年,Synplicity以2400萬美元的金額收購了Hardi,而Synopsys在2008年以2.27億美元收購了Synplicity,HAPS經歷幾代人于2014年發展至HAPS-80,至今仍是業界最快的原型驗證加速平臺。

02物理原型驗證工具的

幾大挑戰及解決方案

目前ASIC的設計變得越來越大,越來越復雜,單片FPGA已不能滿足原型驗證要求,多片FPGA驗證應運而生。RTL邏輯的分割、多片FPGA之間的互聯拓撲結構、I/O分配、高速接口都對應用FPGA原型驗證的芯片開發者提出了更高的要求也帶來了前所未有的挑戰。那當選擇一款合適的物理原形驗證工具時,應該在哪些緯度做重點考量和取舍呢?

1 容量限制和性能要求 對于大型的設計(大于2千萬等效ASIC門),一塊FPGA往往容納不下,此時必須將多塊FPGA互聯才能驗證整個設計,在這種情況下,就需要對大型的設計進行Partition即分割。Partition引入了新的問題,而這些問題其實在芯片中并不存在,很多時候耗費很多人力去實現一個可用的Partition方案,僅僅是受限于FPGA的容量而不得已的處理辦法。

Partition引入的最大問題是對I/O的需求激增,雖然FPGA有超過1000個可用的I/O,但是一個完整的SoC如果被拆分成規模相當的幾個部分時,每個部分之間的互聯信號數量往往會遠超1000個,所以在I/O數量受限時,必須采用TDM(Time Division Multiplex),即FPGA內部的多個并行信號轉為高速串行信號,通過FPGA I/O傳輸到另一塊FPGA,然后再進行解復用,轉換成并行信號,實現信號從一個FPGA到另一塊FPGA的傳遞。引入了TDM雖然解決了I/O瓶頸,但是Mux和De-Mux引入了額外的延時,導致Cross-FPGA的Path成為Critical Path,進一步降低了FPGA的可運行頻率,可以說Partition是不得已而為之的方案,最終的結果只是得到一個可用的方案而非理想的方案。

另一個方面,由于在SoC原型驗證中模塊常常會增減,導致需要頻繁的改動Partition方案,如果手動去處理,則需要花費很多精力才能得到一個上文提到可用但折中的方案。此外,處理大量的Cross-FPGA信號非常容易出錯,所以對于大型的SoC FPGA原型驗證,必須采用自動化的工具去完成Partition,這對EDA工具而言亦是全新的挑戰。

新思科技HAPS原型驗證解決方案,具有獨一無二的自動可干預分割功能,同時提供了系統級跨FPGA的時序分析工具,為HSTDM IP, 纜線和I/O提供時序模型,可以方便地處理TDM路徑上的多個約束,為多FPGA的設計提供了優化且可靠的時序,保證了平臺的高速性能和穩定性。

2 迭代速度

由于SoC芯片的設計頻率很高,為了讓原型驗證平臺盡可能和SoC芯片性能接近,開發者期望讓FPGA原型平臺運行在盡可能高的頻率上,但是由于SoC的RTL代碼是為芯片實現設計,大量深層次組合邏輯的存在(這樣可以節省芯片面積),導致了SoC RTL代碼在FPGA上實現時時序收斂困難,往往只能達到幾MHz。對于大型的SoC,內部的CPU/GPU/CODEC/NPU等計算和編解碼模塊邏輯復雜,往往成為整個設計的Timing Wall,導致時序優化過程會占據FPGA Implementation過程30-40%的時間。

基于新思科技HAPS原型驗證解決方案,在對設計進行分割和時序優化的同時,也充分考慮到后續FPGA布局布線的挑戰,在綜合時,HAPS采用獨特的技術,增強和優化單FPGA的綜合結果,可以有效的減少后期Vivado布局布線的時間,并結合多核多進程綜合等技術,有效減少各個環節的時間,加快迭代速度。

3 接口方案

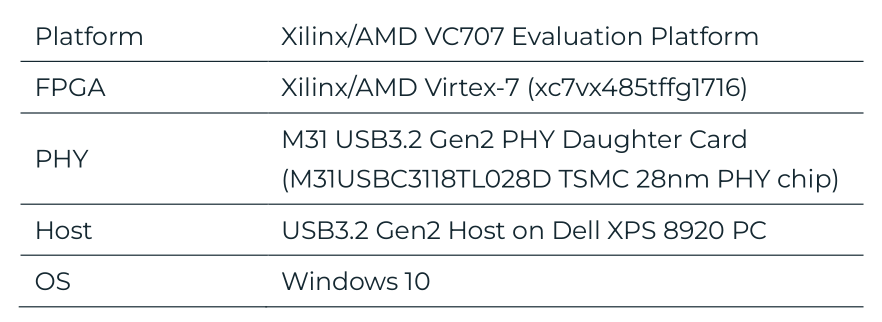

外部子板和FPGA I/O之間的高速同步接口一直以來都是FPGA的痛點和難點:一方面,相比于ASIC,FPGA在I/O時序方面可以調整的空間有限,它不能像ASIC一樣可以通過時序約束來靈活調整FPGA I/O信號之間的Skew,導致并行信號接口之間的Path Skew很難控制在一個比較理想的范圍內,最終會導致數據采樣失敗,降低頻率往往是一種有效的辦法,但是有些控制器和PHY之間的接口是需要滿足標準規范的,不能無限制的降低,對于這種情況有時只能想盡辦法嘗試修復時序,甚至需要修改代碼。

另一方面,原型驗證使用的子板數量不大,市場上往往沒有銷售,很多時候需要自行設計,進一步給調試帶來了不確定性,也延長了調試周期。高速接口的調試往往消耗了大量的人力資源,很多時候都是靠調試的經驗和靈感解決問題,這么做不僅費時費力,而且效果不佳。

新思科技HAPS原型驗證解決方案,給用戶提供了多種靈活的接口方案,包含豐富的外部子卡集合,降速橋方案;還和業界伙伴通過HAPS Connect Program,為使用者提供了更廣泛的擴展空間。

4 可觀測性 FPGA也是芯片產品,所以內部的信號無法直接觀測。通常需要借助于FPGA的Debug工具在生成Bit文件前選取要觀察的信號。當Bit文件加載運行時,必須通過配套的Debug工具觀察指定的信號波形,但是受限于Block RAM的容量以及信號優化等原因,如此調試的效率比較低。

新思科技HAPS原型驗證平臺提供了多種靈活的調試手段。DTD(深度跟蹤調試)功能,為用戶提供了多FPGA實時速度的RTL級別信號聯合波形調試,可以觀測上千信號秒級的波形,進一步結合Verdi/Siloti的關鍵信號提取功能,可顯著的擴大信號觀測的范圍。GSV是另外一個被用戶廣泛采用的調試功能,它可以提供設計內部所有寄存器的快照,在多種實際調試場景有效的幫助軟硬件團隊分析定位系統問題。

5 產品的成熟度

原型驗證是一項壁壘頗高的技術,串聯著芯片設計和最終應用,需要極強的適用性和靈活度來適應發展迅速和多樣性的芯片研發,通過和一線芯片研發人員的通力合作,打造使用生態圈,不斷進化和迭代技術才能始終幫助芯片開發者實現“Shift-Left”研發,加快產品上市時間。

新思科技自2003年起推出第一款原型驗證產品HAPS-10起,持續推出7代產品,久經市場檢驗, 并為滿足不斷演進的原型驗證需求,補充了諸多獨一無二的產品功能,如UMRBus, Hybrid原型驗證,基于UPF的低功耗系統驗證, HAPS GateWay等,是加快軟件開發和芯片設計驗證的最佳解決方案。全球200多家公司都已經部署了最新一代HAPS-80,包括前十大半導體公司中的九家,其出貨量在今年超過3000臺。

國內目前也有逾50家芯片設計企業部署了HAPS平臺,進一步驗證了HAPS原型驗證的市場領先地位。

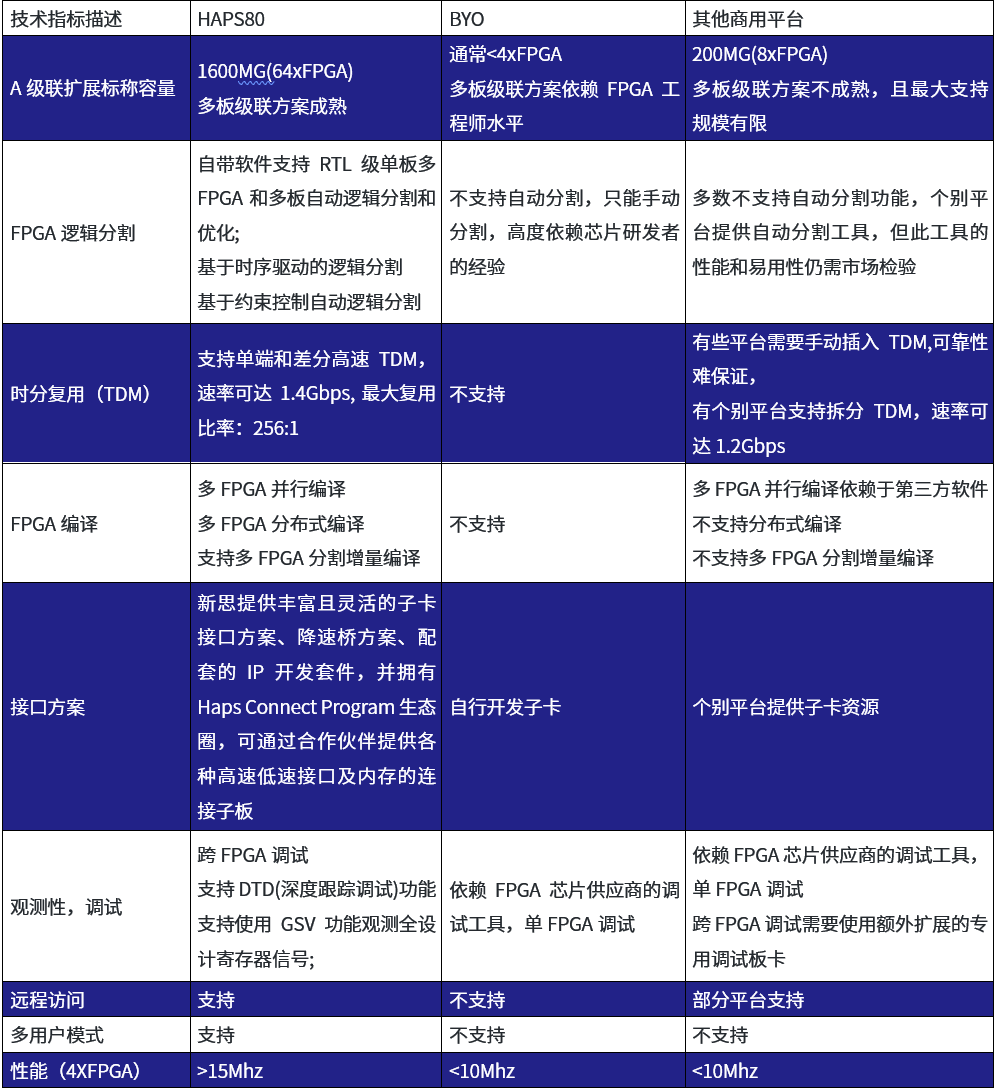

各類FPGA原型驗證平臺技術對比

目前市面上常見的FPGA原型驗證平臺可以分為兩大類別,一類是芯片設計公司自己制作的FPGA板(Build Your Own, 以下簡稱BYO); 另一類是商用FPGA平臺,比如新思科技的HAPS方案。

就上文提到的一些具體考量點,各類原型驗證平臺的對比如下:

顯而易見,新思科技的HAPS方案,在全面性,成熟度,和對大規模設計的支持上,都占有絕對明顯的優勢。

03物理原型

驗證工具的應用不止于芯片

芯片是硬件產業,也是軟件產業,同時涉及下游的應用場景還有上游的高精度設計。在科技賦能的智能化時代,芯片不僅支撐數字經濟的各個方面,在賦能各產業的作用也不容小覷,從5G,自動駕駛汽車,人工智能等,芯片的應用幾乎遍布所有可能想象的電子產品,甚至包括航空航天到軍工技術的所有方面。隨著人工智能和5G的加速發展,以及加快數字化時代的新基建的開展,未來芯片的應用場景會越來越多,定制化芯片的需求也會越來越大。而作為手握未來世界之門鑰匙的開發者們必須要和系統廠商更緊密的協作研發,才能讓芯片技術創新最終賦能科技應用。

以人工智能的人臉識別場景為例,在海量人群中搜索走失兒童需要超強的快速反應能力,才能在第一時間抓住機會識別并找到目標對象,其中軟件支持了人工智能的算法,芯片所提供的超強算力讓復雜的算法在毫秒內實現推斷。物理原型驗證讓軟件的開發和芯片的研發得以同步進行,而不用互相等待。這一技術將推動芯片和科技應用的生態結合,讓科技的進步進入極速模式,加速未來的想象變為現實。

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618415 -

原型驗證

+關注

關注

0文章

24瀏覽量

10859 -

人工智能

+關注

關注

1806文章

49018瀏覽量

249461

原文標題:一文看懂FPGA原型驗證的技術進階之路

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子桌面級原型驗證系統Veloce proFPGA介紹

AMD技術賦能西門子FPGA原型設計解決方案

新思科技推出基于AMD芯片的新一代原型驗證系統

芯華章發布FPGA驗證系統新品HuaProP3

Nordic推出最新物聯網原型驗證平臺Thingy:91 X

芯華章發布新一代FPGA原型驗證系統HuaPro P3

芯華章推出新一代高性能FPGA原型驗證系統

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

數字芯片設計驗證經驗分享文章 實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

各類FPGA原型驗證平臺技術對比 驗證工具的應用不止于芯片

各類FPGA原型驗證平臺技術對比 驗證工具的應用不止于芯片

評論