第二篇以德州儀器(TI)的高速ADC芯片——ads52j90為例,介紹完了4線SPI配置時(shí)序。本篇將以該芯片SPI結(jié)構(gòu)為例,具體介紹如何利用verilog實(shí)現(xiàn)4線SPI配置時(shí)序。

無論實(shí)現(xiàn)讀還是寫功能,都先要提供SCLK。假如FPGA系統(tǒng)工作時(shí)鐘40MHz,我們可以利用計(jì)數(shù)器產(chǎn)生一個(gè)n分頻的時(shí)鐘作為SCLK,本例中n取8,SCLK頻率5MHz。SCLK產(chǎn)生的代碼如下:

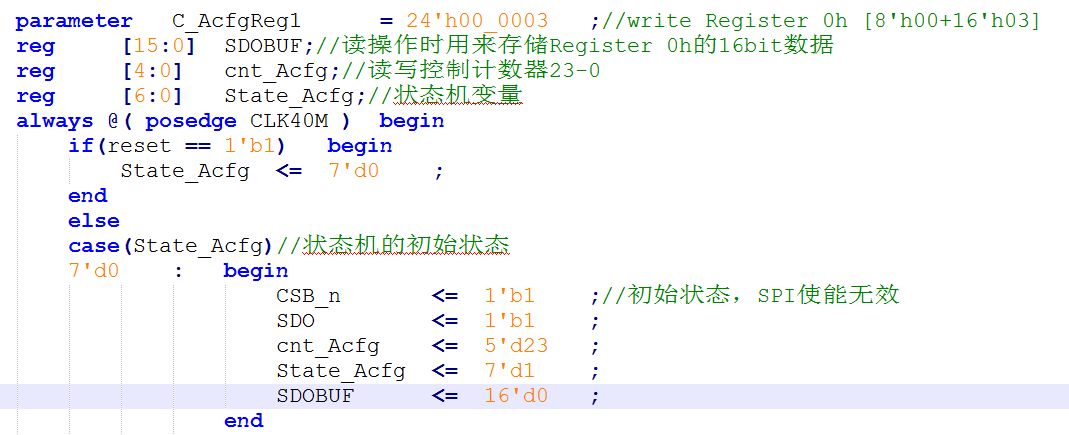

SCLK時(shí)鐘有了,接下來我們建立一個(gè)狀態(tài)機(jī)實(shí)現(xiàn)讀和寫功能:

初始化狀態(tài)的下一個(gè)狀態(tài)就是寫寄存器操作了,每次SCLK的上升沿寫入數(shù)據(jù):

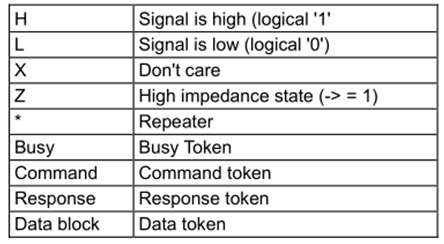

寫完一個(gè)寄存器參數(shù),CSB先拉高。接下來在進(jìn)入下一個(gè)狀態(tài),本篇例子下一個(gè)狀態(tài)的操作是讀取對(duì)應(yīng)寄存器地址的數(shù)據(jù)。我們首先需在SCLK的上升沿寫入8bit的寄存器地址,接下來在SCLK的下降沿讀取16bit的數(shù)據(jù)。

到此,讀寫操作都完成了。代碼上的注釋可以便于大家理解,大家還可以仿真看一下波形加深理解。

-

Verilog

+關(guān)注

關(guān)注

29文章

1367瀏覽量

112251 -

SPI

+關(guān)注

關(guān)注

17文章

1804瀏覽量

95886 -

ADC芯片

+關(guān)注

關(guān)注

3文章

82瀏覽量

20693

原文標(biāo)題:FPGA通過SPI對(duì)ADC配置簡(jiǎn)介(四)---Verilog實(shí)現(xiàn)4線SPI配置

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

ADS1118 spi通信時(shí)序的問題誰來解答一下

Verilog 測(cè)試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開發(fā)指南

KeyStone架構(gòu)串行外設(shè)接口(SPI)手冊(cè)

能否在純fpga上通過verilog實(shí)現(xiàn)SPI控制器去配置adc12dj3200?

ADS127L11配置ADC使用外部時(shí)鐘以及FILTER[4:0]都不成功,為什么?

ADS127L11使用4線spi不管怎么配置寄存器,示波器看到ADC的drdy脈沖周期始終是400K,怎么回事?

瀚海微SD NAND之SD 協(xié)議(42)SPI總線時(shí)序

如何利用Verilog-A開發(fā)器件模型

怎么樣提高verilog代碼編寫水平?

利用Tl的智能高端開關(guān)實(shí)現(xiàn)SPI通信

使用IO-link主幀處理程序實(shí)現(xiàn)靈活的時(shí)序配置

如何利用verilog實(shí)現(xiàn)4線SPI配置時(shí)序

如何利用verilog實(shí)現(xiàn)4線SPI配置時(shí)序

評(píng)論