1.0 序列檢測(cè)器電路設(shè)計(jì)

設(shè)計(jì)一個(gè)序列檢測(cè)器電路,功能是:檢測(cè)出串行輸入數(shù)據(jù)Sin中的4位二進(jìn)制序列0101(自左至右輸入),當(dāng)檢測(cè)到該序列時(shí),輸出Out=1;沒(méi)有檢測(cè)到該序列時(shí),輸出Out=0(注意考慮序列重疊的可能性,如010101,相當(dāng)于出現(xiàn)兩個(gè)0101序列)。

經(jīng)過(guò)分析,首先可以確定采用米利型狀態(tài)機(jī)設(shè)計(jì)該電路。因?yàn)樵撾娐吩谶B續(xù)收到信號(hào)0101時(shí),輸出為1,其他情況下輸出為0,所以采用米利型狀態(tài)機(jī)。

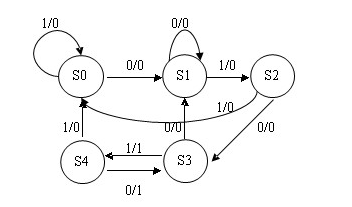

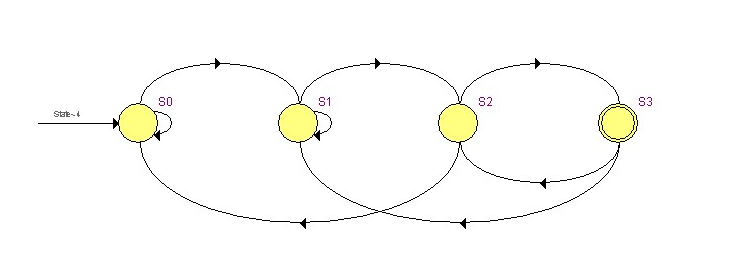

其次,確定狀態(tài)機(jī)的狀態(tài)圖,該電路必須能記憶所收到的輸入數(shù)據(jù)0、連續(xù)收到前兩個(gè)數(shù)據(jù)01.。。可見(jiàn)至少要是個(gè)狀態(tài),分別用S1,S2,S3,S4,再加上電路初始態(tài)S0。根據(jù)要求可以畫(huà)出狀態(tài)圖:

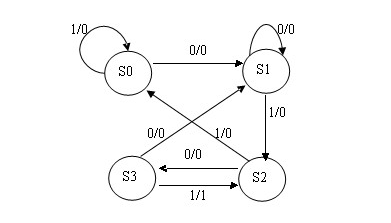

觀察該圖可以看出,當(dāng)狀態(tài)機(jī)處以S2、S4的時(shí)候,如果輸入Sin = 1,則電路會(huì)轉(zhuǎn)移到相同的次態(tài)S0,如果輸入Sin = 0,則電路會(huì)轉(zhuǎn)移到相同的次態(tài)S3,且兩種情況下輸出Out都為0。所以,S2、S4為等價(jià)狀態(tài),可用S2代替S4,于是得到簡(jiǎn)化的狀態(tài)圖:

如果用CPLD/FPGA器件實(shí)現(xiàn)狀態(tài)機(jī),則邏輯綜合器會(huì)自動(dòng)化簡(jiǎn)狀態(tài)機(jī)。

利用Verilog HDL描述狀態(tài)圖主要包括:

(1) 利用參數(shù)定義語(yǔ)句parameter描述狀態(tài)機(jī)中各個(gè)狀態(tài)的名稱(chēng),并指定狀態(tài)編碼。

(2) 用時(shí)序的always塊描述狀態(tài)觸發(fā)器實(shí)現(xiàn)的狀態(tài)存儲(chǔ)。

(3) 使用敏感表和case語(yǔ)句(也可以采用if-else語(yǔ)句)描述狀態(tài)轉(zhuǎn)換邏輯。

(4) 描述狀態(tài)機(jī)的輸出邏輯。

這個(gè)電路我試著用3種方式來(lái)描述,看看他們的差別在哪里。

(1) 單個(gè)always塊描述狀態(tài)機(jī)方法(應(yīng)該避免的寫(xiě)法)

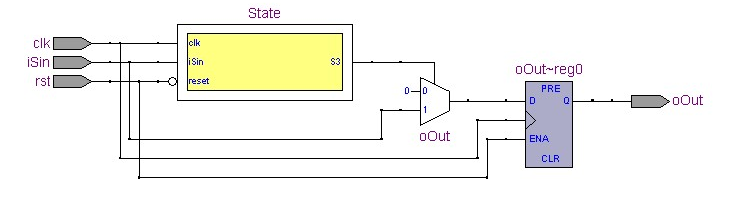

生成的RTL視圖:

State模塊里面其實(shí)就是一個(gè)狀態(tài)機(jī):

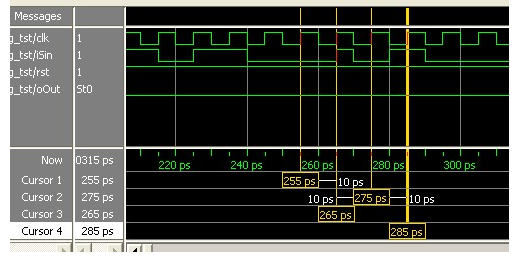

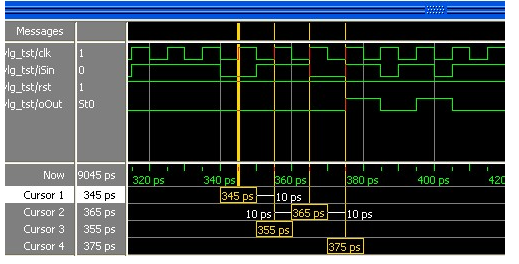

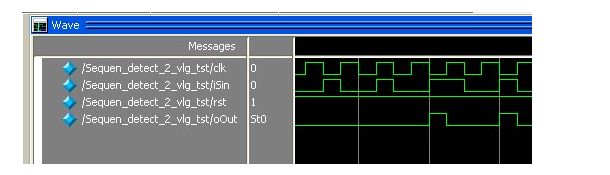

仿真結(jié)果有時(shí)會(huì)出錯(cuò):

在每個(gè)clk上升沿讀取數(shù)據(jù),可以看到是0101,在285ps時(shí)輸出oOut應(yīng)該是高電平,但不是,這是為什么了?再看下面一張圖

這張是對(duì)的,為什么有時(shí)對(duì)又是錯(cuò)了,如果是這樣那就失去了它的意義了。

對(duì)序列檢測(cè)器電路用單個(gè)always塊的描述的邏輯存在一個(gè)隱含的錯(cuò)誤,即輸出信號(hào)oOut的描述存在錯(cuò)誤。其原因是:oOut信號(hào)是由狀態(tài)機(jī)的當(dāng)前狀態(tài)和輸入信號(hào)共同決定的,它是一個(gè)純組合邏輯電路,如果當(dāng)前狀態(tài)不變,而輸入信號(hào)變了,oOut信號(hào)應(yīng)立即發(fā)生變化,而不是等到時(shí)鐘上升沿來(lái)了才變化。因此,單個(gè)always塊描述狀態(tài)機(jī)的寫(xiě)法僅僅適用于穆?tīng)栃蜖顟B(tài)機(jī)。這雖然是個(gè)問(wèn)題,但是跟我出現(xiàn)的問(wèn)題貌似沒(méi)有什么直接關(guān)系,郁悶。。。繼續(xù)思考。

在實(shí)際應(yīng)用中,為了消除組合邏輯輸出信號(hào)中的毛刺,在時(shí)序允許的情況下,通常允許米利型狀態(tài)機(jī)中輸出信號(hào)通過(guò)寄存器輸出。但是單個(gè)的always塊的描述方法將狀態(tài)轉(zhuǎn)換判斷的組合邏輯和狀態(tài)觸發(fā)器轉(zhuǎn)移的時(shí)序邏輯混合編寫(xiě)在同一個(gè)always塊中,不符合將時(shí)序和組合邏輯分開(kāi)描述的代碼風(fēng)格(Coding Style),而且在描述當(dāng)前狀態(tài)時(shí)還要考慮下一個(gè)狀態(tài)的邏輯,整個(gè)代碼的結(jié)構(gòu)不清晰,不利于修改和維護(hù),不利于時(shí)序約束條件的加入,不利于綜合器對(duì)設(shè)計(jì)的優(yōu)化。所以不推薦使用單個(gè)always塊的描述方式。

必須為自己的粗心大意買(mǎi)單,還說(shuō)輸出有時(shí)會(huì)出錯(cuò)原來(lái)狀態(tài)圖都是錯(cuò)了,不經(jīng)意的一眼,看來(lái)不能隨便啊。case語(yǔ)句后的 S1:當(dāng)條件滿足時(shí)(iSin == 1‘b1)時(shí)會(huì)跳到S2否則還會(huì)停留在S1。改過(guò)來(lái)看看正確的狀態(tài)機(jī)就不會(huì)出錯(cuò)了。太粗心了!

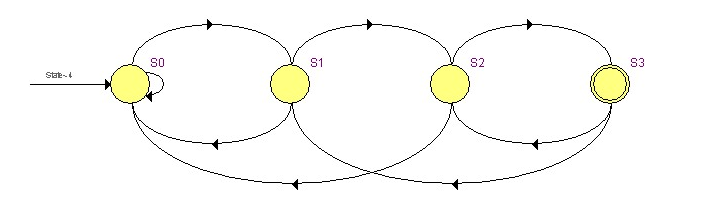

正確的狀態(tài)機(jī):

(2) 兩個(gè)always塊描述狀態(tài)機(jī)的方法(推薦寫(xiě)法)

值得注意的是Next_state = 2’bxx;對(duì)狀態(tài)的默認(rèn)賦值有3種方式:(1) 全部設(shè)置成不定狀態(tài)(x); (2) 設(shè)置成預(yù)先規(guī)定的初始狀態(tài); (3) 設(shè)置成FSM中的某一有效狀態(tài)。設(shè)置成不定狀態(tài)(x)的好處是:(1) 在仿真時(shí)可以很好地考察所設(shè)計(jì)的FSM的完備性,若設(shè)計(jì)的FSM不完備,則進(jìn)入任意狀態(tài),仿真時(shí)容易發(fā)現(xiàn);(2) 綜合器對(duì)代碼進(jìn)行綜合時(shí),會(huì)忽略沒(méi)有定義的狀態(tài)觸發(fā)器向量。

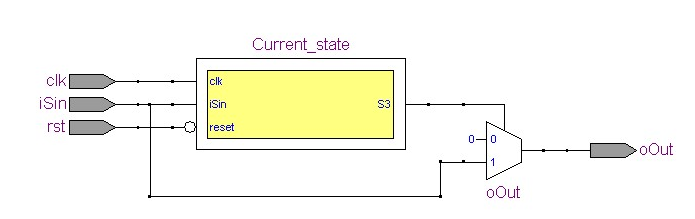

生成的RTL視圖:

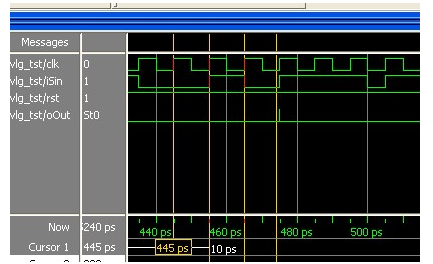

和上面的比較了一下,少了個(gè)D觸發(fā)器,這是為什么呢?并且仿真的結(jié)果也不一樣了。仿真圖:

當(dāng)然新的問(wèn)題也就隨之而來(lái):

我們可以明顯的看到這種寫(xiě)法和上面寫(xiě)法的區(qū)別,最重要的是:輸出oOut不在是在clk上升沿來(lái)的時(shí)候才能發(fā)生變化,它是一個(gè)純組合邏輯電路只要輸入條件滿足輸出就立馬發(fā)生改變。隨著毛刺的出現(xiàn),毛刺是一個(gè)很重要的問(wèn)題,很值得我們認(rèn)真思考。為什么會(huì)出現(xiàn)毛刺了,我們可以清楚的看到這時(shí)次態(tài)是完全由組合邏輯電路決定的,時(shí)序電路做的事情僅僅是在clk上升沿來(lái)的時(shí)候把,把次態(tài)賦給現(xiàn)態(tài)。在445ps時(shí)在S1狀態(tài),輸出為0、在455ps時(shí)在S2狀態(tài),輸出為0、在465ps時(shí)在S3狀態(tài),此時(shí)就算clk的posedge不來(lái),只要iSin == 1,輸出同樣會(huì)為1,正如上圖,但在這里,clk 的上升沿和iSin 的高電平是同時(shí)來(lái)的,所以,在 iSin 的高電平來(lái)的那一瞬間,輸出oOut = 1,就在同時(shí)狀態(tài)裝換到S2,輸出oOut = 0;

這就導(dǎo)致了上面毛刺的產(chǎn)生。怎么解決這個(gè)問(wèn)題呢?我們來(lái)看看第三種方法。

(3) 3個(gè)always塊描述狀態(tài)機(jī)(推薦寫(xiě)法)

分析一下代碼,我們很容易看出:第一個(gè)always塊采用同步時(shí)序邏輯方式描述狀態(tài)轉(zhuǎn)移(在電路框圖的中間框),第二個(gè)always塊采用組合邏輯方式描述狀態(tài)轉(zhuǎn)移規(guī)律(一般是第一個(gè)方框),第三個(gè)always塊描述電路的輸出信號(hào),在時(shí)序允許的情況下,通常讓輸出信號(hào)經(jīng)過(guò)一個(gè)寄存器再輸出,保證輸出信號(hào)中沒(méi)有毛刺。

綜合后的RTL視圖,就跟第一版程序是一樣的了,又有了D觸發(fā)器,仿真結(jié)果和第一版也是一樣的,但是兩版代碼的風(fēng)格(Coding Style)是不一樣的。

-

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43219 -

檢測(cè)器

+關(guān)注

關(guān)注

1文章

888瀏覽量

48484 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

165瀏覽量

48590 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

493瀏覽量

28109

發(fā)布評(píng)論請(qǐng)先 登錄

有可能在 FX3 GPIF2 中創(chuàng)建兩個(gè)獨(dú)立的狀態(tài)機(jī)嗎?

求助,關(guān)于srammaster.cydsn中狀態(tài)機(jī)的問(wèn)題求解

如何快速入門(mén)PLD電路設(shè)計(jì)

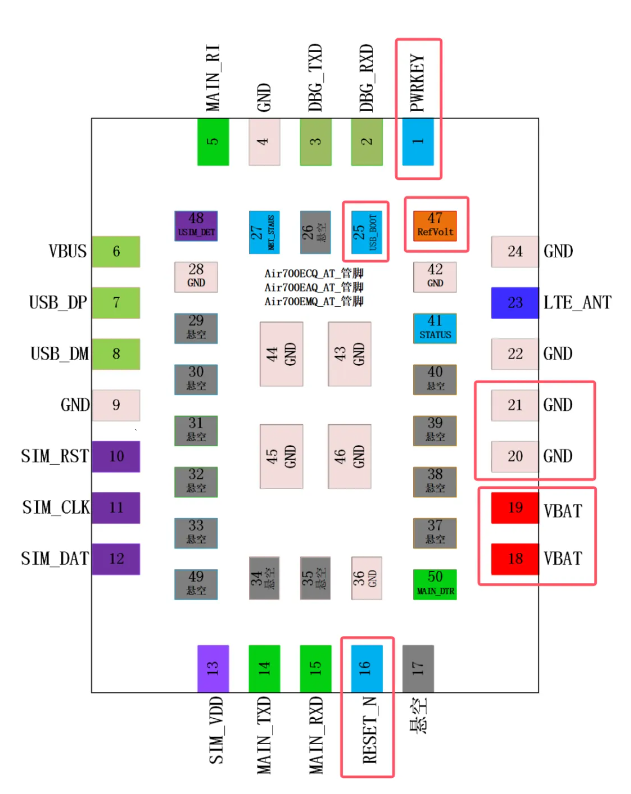

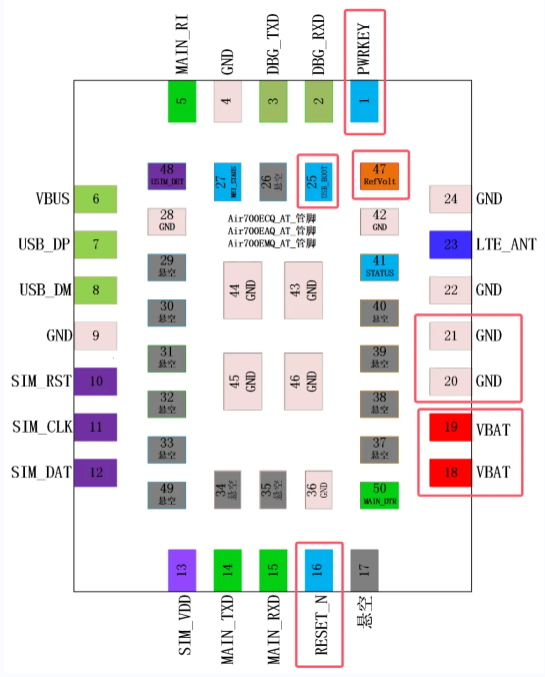

技術(shù)分享!蜂窩模組開(kāi)機(jī)電路設(shè)計(jì)

蜂窩模組開(kāi)機(jī)電路,你學(xué)廢了嗎?

Simulink中的狀態(tài)機(jī)建模方法 Simulink數(shù)據(jù)可視化與分析功能

基于PWM控制的buck電路設(shè)計(jì)

單片機(jī)電路圖用什么軟件畫(huà)

接口芯片的譯碼電路設(shè)計(jì)一般采用什么方法

電流反饋型運(yùn)放與電壓反饋型運(yùn)放

串聯(lián)型穩(wěn)壓電路中的調(diào)整管工作在什么狀態(tài)

時(shí)序邏輯電路中如何判斷有效狀態(tài)和無(wú)效狀態(tài)

觸發(fā)器和狀態(tài)機(jī)的關(guān)系是什么

如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

玩轉(zhuǎn)Spring狀態(tài)機(jī)

采用米利型的狀態(tài)機(jī)電路設(shè)計(jì)

采用米利型的狀態(tài)機(jī)電路設(shè)計(jì)

評(píng)論