描述:

在《Virtex UltraScale+ FPGA 數據手冊》(DS923) 中,XCVU27P-3E 器件和 XCVU29P-3E 器件的最低量產軟件和速度規格已從 Vivado 工具 2019.2 v1.28 更新至 Vivado 工具 2020.1.1 v1.30。

XCVU27P-3E 器件和 XCVU29P-3E 器件的速度文件參數以及速度/溫度等級在 2020.1.1 版中已更新,包括已糾正了集成塊接口建立時間和保持時間參數。

受此影響的主要集成塊包括:PCIe、Interlaken 和 100G Ethernet MAC。

速度文件更新中,部分參數要求已放寬,部分參數要求則進一步收緊。

解決方案:

對于 XCVU27P-3E 器件和 XCVU29P-3E 器件以及速度/溫度等級設計,請使用 Vivado Design Suite 2020.1.1 或更高版本。

您可通過以下方式來評估時序問題對于您使用 Vivado 工具 2019.2 - 2020.1 所構建的設計產生的影響:在 Vivado 2020.1.1 或更高版本中,對已完全實現的設計檢查點 (.dcp) 文件重新運行時序分析。

如果您的比特流是使用 Vivado 工程模式生成的,則必須找到已完全實現的 .dcp 文件。

通常,已完全實現的 .dcp 文件應位于如下某一路徑中,具體取決于布線后是否已啟用 phys_opt_design。

project_myDesign.runs/impl_1/myDesign_routed.dcp

project_myDesign.runs/impl_1/myDesign_postroute_physopt.dcp

例如,如果已完全實現的 .dcp 文件為 myDesign_routed.dcp,則上述命令應如下所示:

#Open the final dcp for the finished design open_checkpoint project_myDesign.runs/impl_1/myDesign_routed.dcp #Report timing report_timing_summary -file myDesign_timing_summary_routed.rpt

如果在受影響的主要集成塊上出現時序違例,則必須在 Vivado 2020.1.1 或更高版本中對設計進行重新編譯以達成時序收斂。

原文標題:面向 XCVU27P-3E 器件和 XCVU29P-3E 器件的 Vivado 2020.1.1 量產速度文件更新

文章出處:【微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

-

PCIe

+關注

關注

16文章

1340瀏覽量

85102 -

Vivado

+關注

關注

19文章

834瀏覽量

68698

原文標題:面向 XCVU27P-3E 器件和 XCVU29P-3E 器件的 Vivado 2020.1.1 量產速度文件更新

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

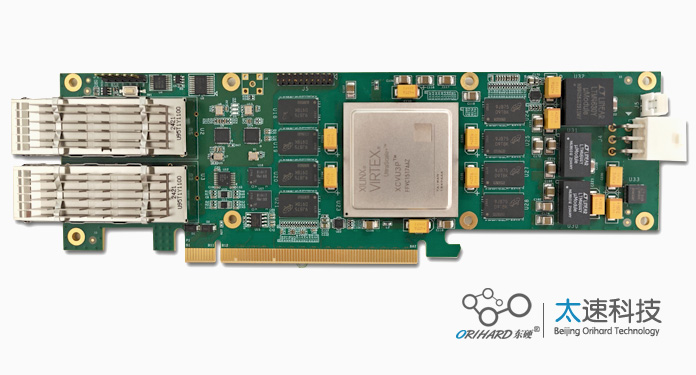

設計原理圖:U200E 基于VU9P的4路QSFP28光纖PCIeX16收發卡

集中式ZDM-E0400P3熱電阻RTD測溫模塊(1) — 基礎應用

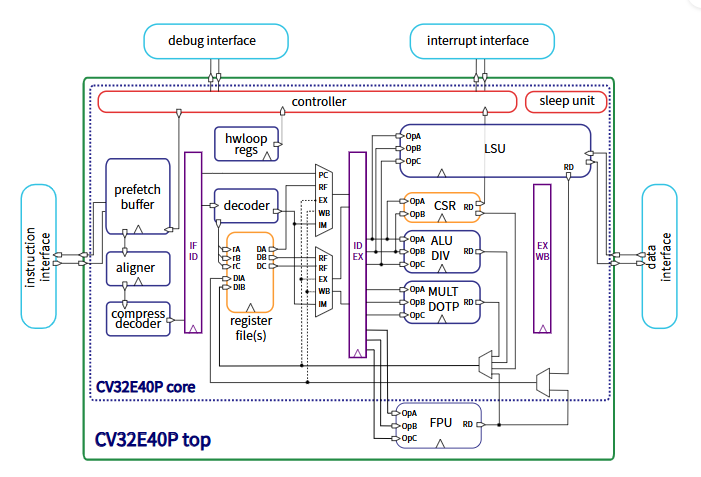

CORE-V(OpenHW Group)CV32E40P 詳細解讀

DD20-48E0524B3C3 DD20-48E0524B3C3

PDD12-18E0507A3C2 PDD12-18E0507A3C2

DD6-05S24E3C2 DD6-05S24E3C2

KW3-24D24E3R3 KW3-24D24E3R3

KW1-24D15E3R3 KW1-24D15E3R3

DA10-220S3V3P2D4 DA10-220S3V3P2D4

XCVU13P板卡設計原理圖:509-基于XCVU13P的4路QSFP28光纖PCIeX16收發卡

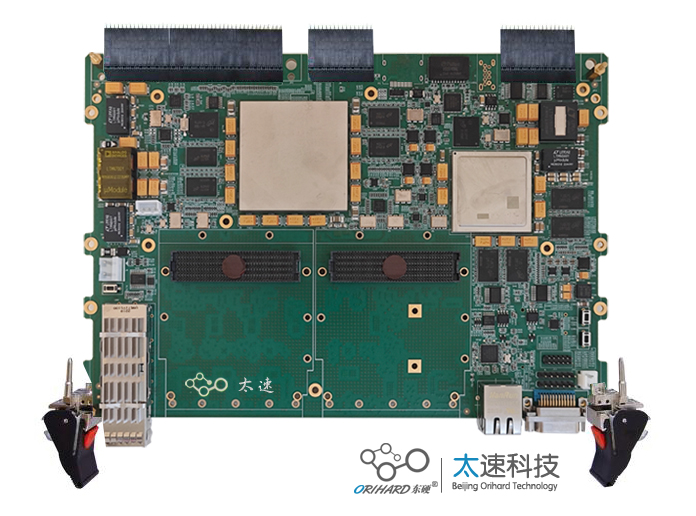

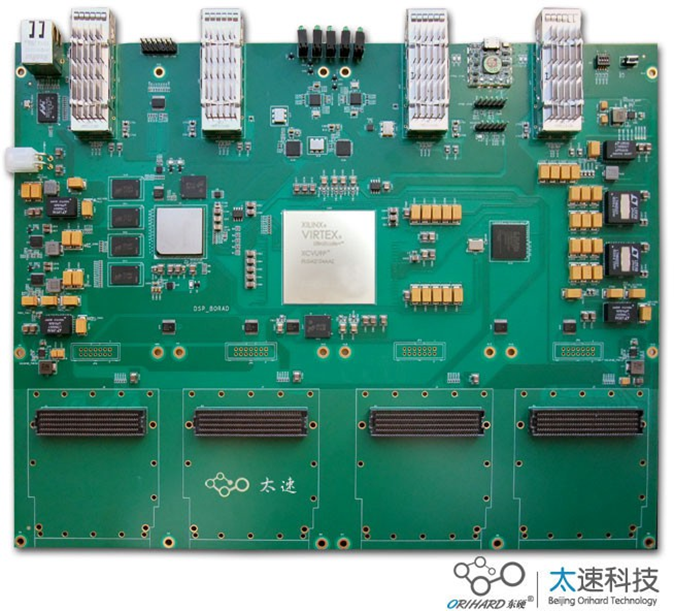

基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡

XCVU9P 板卡設計原理圖:616-基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡 高性能數字計算卡

智能加速計算卡設計原理圖:628-基于VU3P的雙路100G光纖加速計算卡 XCVU3P板卡

XCVU27P-3E和 XCVU29P-3E的速度文件參數已更新

XCVU27P-3E和 XCVU29P-3E的速度文件參數已更新

評論