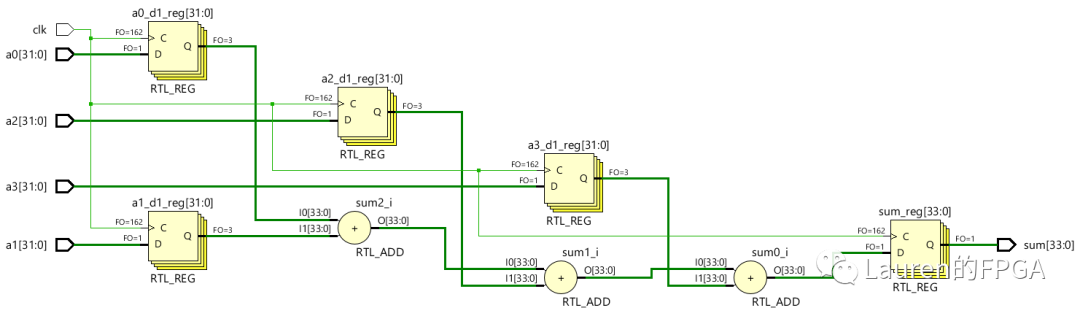

兩個數相加,三個數相加有什么不同 接下來,我們考慮4個32-bit有符號數相加該如何實現,其中目標時鐘頻率仍為400MHz。以UltraScale Plus系列芯片為目標芯片。 第一種方案:四個數直接相加此方案對應的電路圖如下圖所示。這里不難看出關鍵路徑是三個加法器所在路徑,這將是時序收斂的瓶頸。

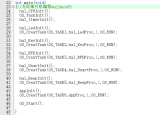

此電路對應的SystemVerilog代碼如下圖所示。

從綜合后的結果來看,邏輯級數最高為7。

第二種方案:加法樹

加法樹的結構如下圖所示,兩兩相加。與第一種方案相比,可以有效降低邏輯級數。

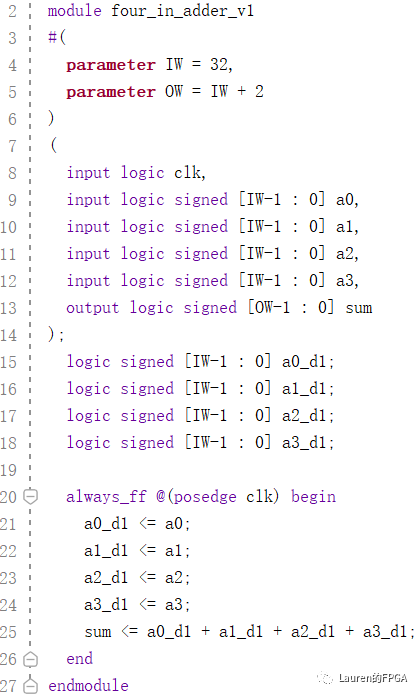

此電路對應的SystemVerilog代碼如下圖所示。

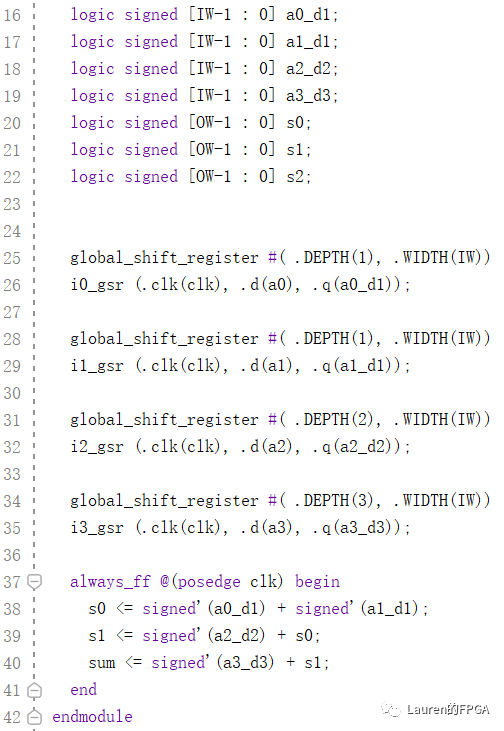

從綜合后的結果來看,邏輯級數最高為6。 第三種方案:加法鏈之所以選用加法鏈的結構是因為DSP48本身就是這種鏈式結構。對應的電路如下圖所示。其中a0和a1端口有一級寄存器,a2端口有兩級寄存器,a3端口有三級寄存器。

此電路對應的SystemVerilog代碼如下圖所示。

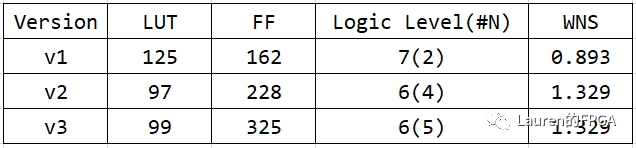

接下來,我們對這三種方案進行比較,如下圖所示。不難看出,第一種方案邏輯級數最高,消耗的LUT也最多,時序結果也是最差的(盡管達到了收斂的目的)。后兩種方案不相上下。

如果將這三種方案通過綜合屬性USE_DSP使其映射到DSP48上,結果如何呢?如下圖所示。不難看出,第一種方案只消耗了兩個DSP,資源利用率最低,但時序也是最糟糕的。后兩種方案都用了三個DSP,但第三種方案由于可以很好地匹配硬件結構,故時序最好。

對比下來不難得出這樣的結論:寫RTL代碼時,盡可能地做到代碼風格與硬件結構相匹配,可達到更好的性能。

Tcl之$$a 80%的概率...... AI Engine到底是什么?

ACAP不可不知的幾個基本概念

嵌套的for循環,到底對哪個執行pipeline更好

HLS中循環的并行性(2)

HLS中循環的并行性(1)

HLS優化方法DATAFLOW你用了嗎

HLS中如何控制流水程度

如何查看可綜合C代碼的中間結果

如何在C代碼中插入移位寄存器

HLS IP Library? HLS Math Library:csim ?C/RTL co-sim(2) HLS Math Library:csim ?C/RTL co-sim(1) 加法運算很簡單? AXI-4 Lite與AXI-4 Memory Mapped有什么區別? 深入理解AXI-4 Memory Mapped 接口協議 AXI是Interface還是Bus? 如何閱讀時序報告 時序報告要看哪些指標 如何使set_max_delay不被覆蓋 一些小巧的IP IP是用DCP還是XCI? 如果使用第三方綜合工具,Xilinx IP… IP生成文件知多少 IP的約束需要處理嗎? IP為什么被Locked? copy_ip你用過嗎? IP是XCI還是XCIX 如何降低OSERDES/CLK和CLKDIV的Clock Skew 如何獲取Device DNA 談談設計復用 過約束到底怎么做 時序收斂之Baseline 什么情況下要用OOC綜合方式 異步跨時鐘域電路該怎么約束 如何復用關鍵路徑的布局布線信息 Vivado學習資料有哪些? 異步跨時鐘域電路怎么設計 ECO都有哪些應用 FPGA中的CLOCK REGION和SLR是什么含義 FPGA中的BEL, SITE, TILE是什么含義 約束文件有哪些 如何高效復用Block的位置信息? 如何復用關鍵寄存器的位置信息 部分可重配置都生成哪些.bit文件 VIO你用對了嗎 Device視圖下能看到什么 Schematic視圖下能看到什么 都是pin,有什么區別 都是net,有什么區別 如何快速查找目標cell 學習筆記:深度學習與INT8 學習筆記:多層感知器 學習筆記:單層感知器的局限性 學習筆記:單層感知器基礎知識 學習筆記:神經網絡學習算法 學習筆記:神經網絡模型 學習筆記:ReLU的各種變形函數 學習筆記:神經元模型(2) 學習筆記:神經元模型(1) 學習筆記:深度學習之“深” 學習筆記:深度學習之“學習” 學習筆記:人工智能、機器學習和深度學習 2019文章匯總

原文標題:加法樹還是加法鏈?

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

-

電路圖

+關注

關注

10404文章

10735瀏覽量

541467 -

32-bit

+關注

關注

0文章

7瀏覽量

6462

原文標題:加法樹還是加法鏈?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

分析C語言代碼結構的設計問題

如何寫出穩定的單片機代碼

汽車異構硬件平臺開發如何進行靜態代碼分析

寫 Verilog 如何做到心中有電路?

ida反編譯出來代碼能直接用嗎

hex文件如何查看原c語言代碼

為了盡可能的消除模擬開關的影響,xtr105的電壓至少需要多少伏?

請問怎樣修改電路使帶寬盡可能加寬到200MHz以上,增益不要有太大的波動?

軟件設計哲學:新“代碼整潔之道”

請問stm32f103VCT6的spi1的兩處接口可以混用嗎?

電路的阻抗如何匹配

該如何提高代碼容錯率、降低代碼耦合度?

寫RTL代碼時,盡可能地做到代碼風格與硬件結構相匹配

寫RTL代碼時,盡可能地做到代碼風格與硬件結構相匹配

評論