在嵌入式系統里,以太網是一個基本的接口,既用于調試,也用于數據傳輸。所以在單板調試過程中,以太網是一個基本的任務。如果以太網工作正常,也可以說是一個重要的里程碑。

Xilinx MPSoC支持多個網卡,應用成熟,下面是常見的調試思路。

1. 以太網硬件

以太網的硬件,分為兩塊,第一是MAC,第二是PHY。當然,在調試以太網以前,CPU和DDR、相關總線都要工作正常。MAC和PHY之間,有兩個接口,第一是數據接口,可能是MII、GMII、RGMII、SGMII等;第二是管理接口,MDIO總線。數據接口用于傳輸數據。對RGMII而言,如果以太網工作在1000M,頻率是125MHz;如果以太網工作在100M,頻率是25MHz。MDIO是類似IIC的總線,MAC提供時鐘MDC,數據線MDIO是雙向的,既可以讀PHY的寄存器,也可以寫PHY的寄存器。

!Xilinx MPSoC RGMII信號](https://upload-images.jianshu.io/upload_images/22911878-ecedcfc816a786bd...)

2. 軟件

2.1. Standalone代碼

Xilinx在Xilinx/SDK/2018.3/data/embeddedsw/XilinxProcessorIPLib/drivers/emacps_v3_8/examples提供了測試代碼xemacps_example_intr_dma.c。2018.3是版本號,請根據自己情況更改。xemacps_example_intr_dma.c的功能是初始化MAC和PHY,設置PHY為自環,發送一個包,再接收一個包,最后檢查數據是否正確。如果代碼不能退出,可能是發送失敗,或者沒有收到包。代碼缺省配置MAC和PHY為1000M。

2.2. UBoot代碼

UBoot下,MAC的驅動代碼是drivers/net目錄下的macb.c。

PHY的驅動代碼是drivers/net/phy目錄下的phy.c,以及廠家相關代碼,比如ti.c。

2.3. Linux代碼

Linux下,MAC的驅動代碼是drivers/net/ethernet/cadence目錄下的macb_main.c、macb_ptp.c。

PHY的驅動代碼是drivers/net/phy目錄下的phy.c,以及廠家相關代碼,比如dp83867.c。

2.4. 設備樹

UBoot/Linux的驅動代碼需要設備樹提供一些參數。其中一個必須的參數是PHY的地址。下面代碼是U-Boot 2019.1里zynqmp-zcu102-revB.dts文件里關于Phy的設置。它指定了PHY的地址0xc。其它參數是Phy的參數,設置原因請參考PHY手冊。

&gem3 {

phy-handle = ;

phyc: phy@c {

reg = ;

ti,rx-internal-delay = ;

ti,tx-internal-delay = ;

ti,fifo-depth = ;

ti,dp83867-rxctrl-strap-quirk;

/* reset-gpios = ; */

};

/* Cleanup from RevA */

/delete-node/ phy@21;

};

3. 調試流程

調試時,先確保硬件工作正常。需要軟件配合時,Standalone代碼最簡單,因此最好修改Standalone代碼來配合硬件調試。

3.1. 檢查MDIO

讓軟件發起PHY寄存器的讀寫操作,檢查MDC/MDIO是否有跳變及其信號質量。

3.2. 檢查PHY

讓軟件讀PHY的ID等寄存器,對照手冊,看寄存器值是否正確。如果不對,可能是PHY的地址錯誤。也可以從0到31嘗試PHY的地址,讀取PHY的ID。讀到正確的ID,就說明PHY的地址對了。

3.3. 測試自協商

連接單板和電腦,電腦分別配置成自協商、1000M、100M、10M。讓軟件讀PHY寄存器的自協商結果寄存器,檢查單板側PHY自協商的結果。

3.4. RGMII時鐘

對RGMII而言,TX_Clk是MAC發出的,RX_Clk是PHY發出的。如果沒有時鐘,MAC自環也會有問題。需要確保TX_Clk、RX_Clk正常。

3.5. MAC自環測試

network_control寄存器的bit 1是loopback_local,用于使能本地自環。在測試數據收發之前,可以先設置loopback_local,再進行發送、接收測試。

在Standalone代碼下,調用函數EmacPsUtilEnterLocalLoopback()可以完成這個操作。

建議創建一個Standalone的工程,把xemacps_example_intr_dma.c復制到工程中。再在xemacps_example_intr_dma.c中調用EmacPsUtilEnterLocalLoopback()設置本地自環,完成MAC自環測試。

3.6. PHY自環測試

在Standalone代碼下,函數EmacPsUtilEnterLoopback()會設置PHY為自環模式。它調用XEmacPsDetectPHY()檢測PHY的地址,在讀取PHY的ID,并根據ID判斷PHY的廠家是Marvell或者Ti,再調用對應的函數設置PHY為自環模式。對于ZCU102單板,會調用EmacPsUtilTiPhyLoopback()。

建議創建一個Standalone的工程,把xemacps_example_intr_dma.c復制到工程中。如果PHY和Xilinx開發板型號一樣,xemacps_example_intr_dma.c能夠正常完成PHY自環測試。

3.7. 檢查MAC統計計數寄存器

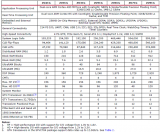

MAC提供了寄存器統計MAC的運行狀態。其中最重要的兩個寄存器是frames_txed_ok、frames_rxed_ok。frames_txed_ok的偏移是0x0108,表示成功發送的幀的數目。frames_rxed_ok的偏移是0x0158,表示成功接收的幀的數目。

在調試時,檢查者兩個寄存器,可以檢查MAC的發送和接收的狀態。

3.8. UBoot測試

在MAC自環和PHY自環測試成功后,可以在UBoot測試以太網,比如使用簡單的ping命令。可以把對端的電腦,分別設置成1000M、100M、10M的情況,檢查是否能夠成功ping對端的電腦。下面是一個ping命令的例子。

uboot> setenv ipaddr 192.168.0.111

uboot> setenv serverip 192.168.0.100

uboot> ping 192.168.0.100

host 192.168.0.100 is alive

3.9. Linux測試

在MAC自環和PHY自環測試成功后,可以在Linux測試以太網,比如可以檢查Linux啟動后,能否通過DHCP得到IP地址,能否成功ping其它主機。同UBoot一樣,也可以把對端的電腦,分別設置成1000M、100M、10M的情況,檢查是否能夠成功ping對端的電腦。

-

以太網

+關注

關注

40文章

5590瀏覽量

174959 -

嵌入式系統

+關注

關注

41文章

3668瀏覽量

130950 -

Linux

+關注

關注

87文章

11469瀏覽量

212899

發布評論請先 登錄

什么是Xilinx ZynqUltraScale+ MPSoC技術?

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

XILINX MPSOC系列FPGA視頻教程

基于Xilinx UltraScale+MPSoC的自動駕駛專用板卡

Xilinx Zynq UltraScale MPSoC可擴展電源設計

Xilinx Zynq UltraScale+ MPSoC的同步調試和跟蹤演示

在Xilinx Zynq UltraScale+ MPSoC中實現的NVMe主機加速器

Xilinx UltraScale+ FPGA和MPSoC互連寬度的使用

詳解Xilinx公司Zynq? UltraScale+?MPSoC產品

Xilinx的Xa Zynq UltraScale MPSOC數據手冊免費下載

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

AMD-Xilinx MPSoC的Watchdog在Linux中使用的簡明教程

適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計

淺談Xilinx MPSoC常見的調試思路

淺談Xilinx MPSoC常見的調試思路

評論