約束主時鐘

在這一節開講之前,我們先把wave_gen工程的wave_gen_timing.xdc中的內容都刪掉,即先看下在沒有任何時序約束的情況下會綜合出什么結果?

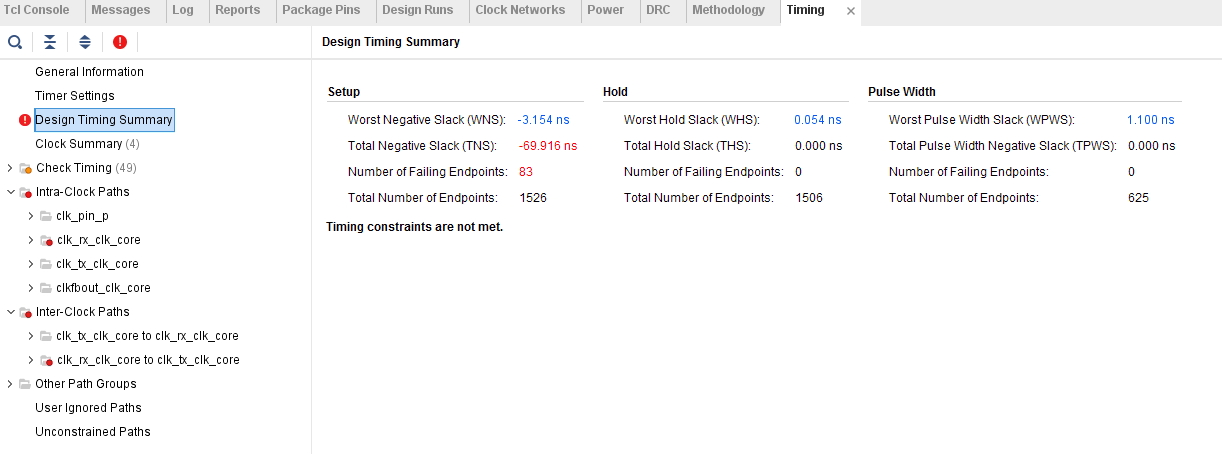

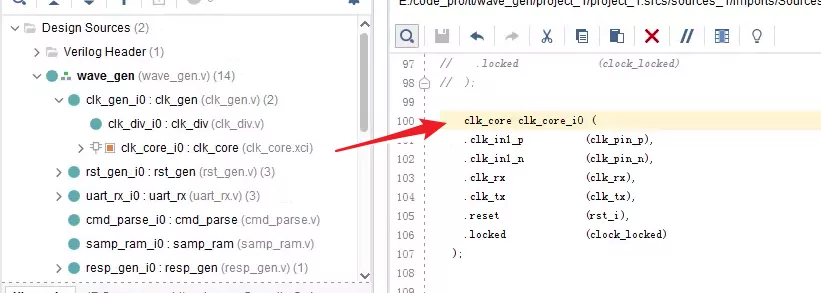

對工程綜合并Implementation后,Open Implemented Design,會看到下圖所示內容。

可以看到,時序并未收斂。可能到這里有的同學就會有疑問,我們都已經把時序約束的內容都刪了,按我們第一講中提到的“因此如果我們不加時序約束,軟件是無法得知我們的時鐘周期是多少,PAR后的結果是不會提示時序警告的”,這是因為在該工程中,用了一個MMCM,并在里面設置了輸入信號頻率,因此這個時鐘軟件會自動加上約束。

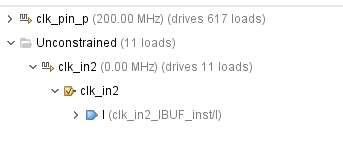

接下來,我們在tcl命令行中輸入report_clock_networks -name main,顯示如下:

可以看出,Vivado會自動設別出兩個主時鐘,其中clk_pin_p是200MHz,這個是直接輸入到了MMCM中,因此會自動約束;另一個輸入時鐘clk_in2沒有約束,需要我們手動進行約束。

或者可以使用check_timing -override_defaults no_clock指令,這個指令我們之前的內容講過,這里不再重復講了。

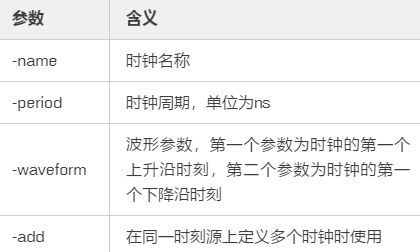

在tcl中輸入

create_clock -name clk2 -period 25 [get_ports clk_in2]

注:在Vivado中,可以直接通過tcl直接運行時序約束腳本,運行后Vivado會自動把這些約束加入到xdc文件中。

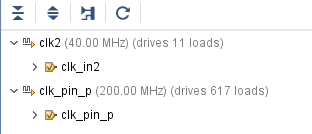

再執行report_clock_networks -name main,顯示如下:

可以看到,主時鐘都已被正確約束。

編輯:hfy

-

FPGA

+關注

關注

1642文章

21920瀏覽量

612047 -

TCL

+關注

關注

11文章

1774瀏覽量

89482 -

Vivado

+關注

關注

19文章

825瀏覽量

67918 -

時鐘約束

+關注

關注

0文章

15瀏覽量

6087

發布評論請先 登錄

相關推薦

FPGA案例解析:針對源同步的時序約束

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA時鐘約束問題

FPGA時序約束之設置時鐘組

FPGA之主時鐘約束解析

FPGA之主時鐘約束解析

評論