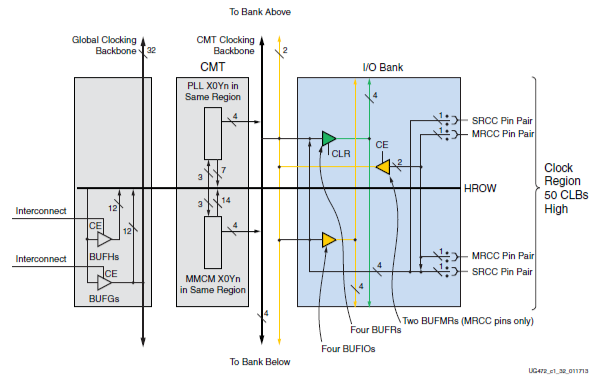

slice與全局時(shí)鐘在一起就可以實(shí)現(xiàn)任意的組合邏輯和時(shí)序邏輯功能,但很多時(shí)候咱們還需要將FPGA內(nèi)部的數(shù)據(jù)暫時(shí)存儲(chǔ),用作它用。Slice作為FPGA最基本的單元,也是能夠完成數(shù)據(jù)存儲(chǔ)的功能,但顯然有些大材小用,因此xilinx公司在其FPGA內(nèi)部專門集成了很多存儲(chǔ)器模塊,稱作Block RAM,其猶如slice海洋當(dāng)中的一顆顆明珠,專門實(shí)現(xiàn)數(shù)據(jù)暫存功能,且每個(gè)時(shí)鐘區(qū)域都布置了若干個(gè)Block RAM。

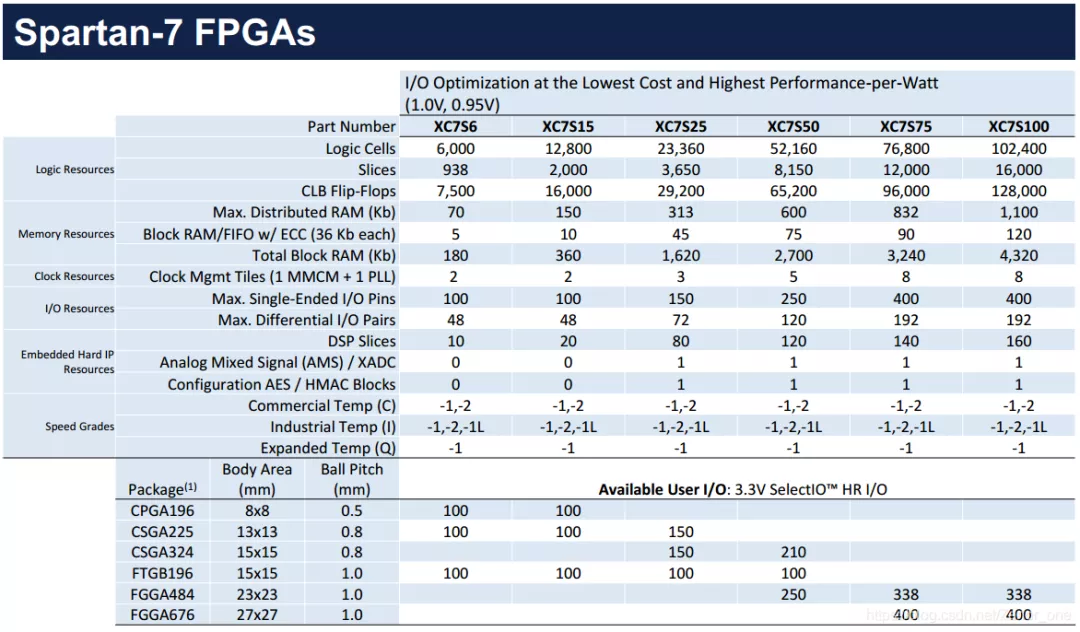

今天咱們就聊一聊7系列FPGA里面的Block RAM。

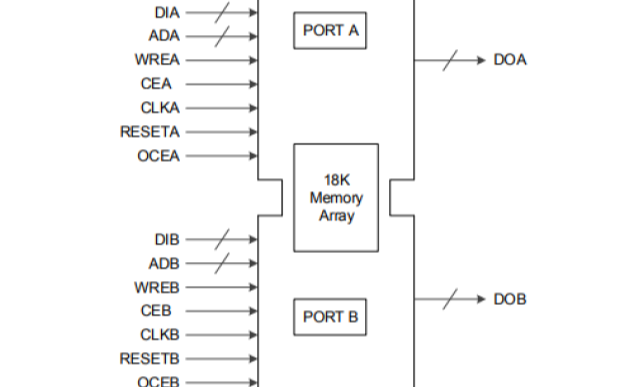

在7系列FPGA里面,每個(gè)Block RAM最多可存儲(chǔ)36Kb的數(shù)據(jù),2個(gè)Block RAM可級(jí)聯(lián)實(shí)現(xiàn)64kb數(shù)據(jù)存儲(chǔ),而每個(gè)Block RAM又可分成2個(gè)18kb的Block RAM,僅此而已,不可再分,亦不可無限級(jí)聯(lián)。

Block RAM在使用的時(shí)候都是使用Xilinx CORE Generator來無腦配置,可以配置成RAM、ROM以及運(yùn)用最廣泛的FIFO。RAM可以配置成各種不同的接口模式以及讀出模式,F(xiàn)IFO則可配置成同步FIFO和異步FIFO等。所有配置信息咱們都是在FPGA的開發(fā)工具Xilinx CORE Generator里面實(shí)現(xiàn)。

Block RAM的各種不同配置以及如何在全局時(shí)鐘下讀/寫數(shù)據(jù)RAM和FIFO內(nèi)容太多,不太好描述,但其實(shí)用起來很easy,基本上只用得到以下a幾個(gè)信號(hào):時(shí)鐘、復(fù)位、時(shí)鐘使能、讀數(shù)據(jù)、讀地址、讀使能、寫數(shù)據(jù)、寫地址、寫使能、數(shù)據(jù)空信號(hào)、數(shù)據(jù)滿信號(hào),以后咱們單獨(dú)拿出來,用具體例子操作一波!

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1643文章

21982瀏覽量

614567 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166529 -

Xilinx

+關(guān)注

關(guān)注

73文章

2183瀏覽量

124464

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx 7系列FPGA的時(shí)鐘結(jié)構(gòu)解析

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx 7系列FPGA管腳是如何定義的?

xilinx公司的7系列FPGA應(yīng)用指南

FPGA從Xilinx 的7系列學(xué)起(8)

Xilinx 7系列FPGA使用之CLB探索(一)

FPGA的RAM存儲(chǔ)資源詳細(xì)資料說明

Xilinx 7系列FPGA時(shí)鐘資源

Xilinx 7 系列FPGA中的Serdes總結(jié)

Xilinx 7系列FPGA簡(jiǎn)介--選型參考

Xilinx 7系列FPGA管腳是如何定義的?

Xilinx 7系列與Ultrascale系列FPGA的區(qū)別

簡(jiǎn)述Xilinx 7系列FPGA芯片相關(guān)知識(shí)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

xilinx 7系列FPGA里面的Block RAM

xilinx 7系列FPGA里面的Block RAM

評(píng)論