做FPGA樣機和做芯片的思路其實是有差異的。為了追求好的性能,節(jié)省成本,降低功耗(PPA),芯片設(shè)計者往往把事情做到極致,去做驗證時把各種覆蓋率盡可能做到100%,把每個模塊電路結(jié)構(gòu)優(yōu)化到面積最小,通過Power Gating和Clock Gating等技術(shù)把功耗降到最低,爭取把每次流片(燒錢)的風險降到最低;相比芯片設(shè)計流程,F(xiàn)PGA樣機的開發(fā)人員往往不太注重上述要求,雖然有著與做芯片相同的目標和追求,但往往因為FPGA的可編程性,即便后續(xù)發(fā)現(xiàn)問題,也可以通過修改代碼再次燒寫bit文件的方式來彌補,出錯成本相對低了很多。但如果按照做芯片的方式來做FPGA樣機,肯定會帶來更好的結(jié)果,甚至可以大幅度的降低FPGA開發(fā)時間。在這個過程中,就需要把常規(guī)的做FPGA的方式進行修正,比如經(jīng)常采用的跟FPGA編譯工具聯(lián)合仿真的辦法就不太適合做芯片的驗證了。本文就探討如何把Vivado與ModelSim聯(lián)合仿真修改為單獨采用ModelSim進行仿真。

在本公眾號上一篇文章(【干貨】推薦一款FPGA仿真調(diào)試鳥槍換炮的工具!)中就曾提到,隔行如隔山,做芯片的人永遠無法理解只做FPGA樣機的人在某些情況下不做仿真就直接上板的做法,非芯片設(shè)計出身只做FPGA樣機的人也不知道這個世界上還存在更為高效的Verilog或VHDL語言的仿真工具和仿真方法,也不理解為了把一個芯片做到極致,必須嚴格要求代碼規(guī)范的做法。為了能夠使用上一篇文章中高效的Verdi或者SimVision仿真調(diào)試工具,脫離Vivado等仿真工具單獨搭建仿真環(huán)境的就成為比較急迫的需求了。

本公眾號之前也曾經(jīng)發(fā)布過一篇相關(guān)的文章,用Modelsim獨立仿真帶Vivado IP核的仿真工程,也是實現(xiàn)采用ModelSim單獨搭建仿真環(huán)境的一種方法,但文中所述方法仍未徹底擺脫Vivado的環(huán)境,適用的場景也受到限制,某些工程中還會出錯。因此,本文從最原始文件搭建仿真環(huán)境的思路出發(fā),嘗試著研究脫離Vivado單獨建仿真環(huán)境的過程中都會遇到什么問題,采用什么樣的方法比較容易解決,筆者試了好幾個工程,總結(jié)出一套相對完善的解決思路,來分享給大家。

FPGA開發(fā)最不理解的芯片設(shè)計中的操作

1、做芯片的仿真最后都不用圖形界面

與剛開始做FPGA開發(fā)時都在圖形界面下操作的仿真方法不同,做大規(guī)模芯片設(shè)計時的仿真常常不調(diào)用圖形界面,都是采用命令行的形式做的仿真。

上圖就是采用簡單的windows下的批處理調(diào)用modelsim進行的一個仿真過程,這個簡單的批處理,就是腳本。也是本文最終要實現(xiàn)的目標。

set PROJECT_PATH=%cd% ::vsim -do sim.do vsim -c -do sim.do

腳本,是芯片設(shè)計人員必須要掌握的基本技能。在芯片設(shè)計的各個階段,腳本的作用是非常巨大的。代碼仿真,可以使用腳本來進行仿真環(huán)境的搭建,綜合的約束文件,必須采用腳本來提前對綜合過程中的各種要求進行說明,后端就更不用說了。因為整個芯片的設(shè)計流程,每個流程的所有中間信息都是靠文本來儲存的,RTL代碼,netlist,后端的顏色文件,流片用的GDSII等等,對文本進行隨意的操作處理就是一名IC設(shè)計人員的基本技能。

如下圖就是一個簡單的采用NCVerilog進行仿真的腳本。

#!/bin/sh echo "/`include /"../testcase166/$1.v/"" > testcase.v sed "s///wave.shm///wave$1.shm/g" ../testbench/testbench.v > testbench.tmp cp ../testbench/testbench.v ../testbench/testbench.bak cp testbench.tmp ../testbench/testbench.v rm -f testbench.tmp ncverilog -f ../filelist/filelist.v +access+rwc -l ../log/log/$1.log mv ../testbench/testbench.bak ../testbench/testbench.v rm -f testcase ~

而下圖則是一個采用TCL語言描述的Design Complier綜合腳本的開頭部分。

sh date

remove_design -designs

##########################

#set library #

##########################

set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys /

/tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]

set target_library { smic25_tt.db }

set link_library { smic25_tt.db }

set symbol_library { smic25.sdb }

##########################

#Paths variables #

##########################

set main_dir ../..

set RTL_ROOT_PATH $main_dir/hdl

set NETLIST_PATH $main_dir/sim/syn/netlist

set RPT_PATH $main_dir/sim/syn/log

set DB_PATH $main_dir/sim/syn/db

set SDF_PATH $main_dir/sim/syn/sdf

##########################

#void warning Info #

##########################

suppress_message VER-130

suppress_message VER-129

suppress_message VER-318

suppress_message ELAB-311

suppress_message VER-936

################################

#read&link&Check design#

################################

2、做芯片的仿真最后都不看波形

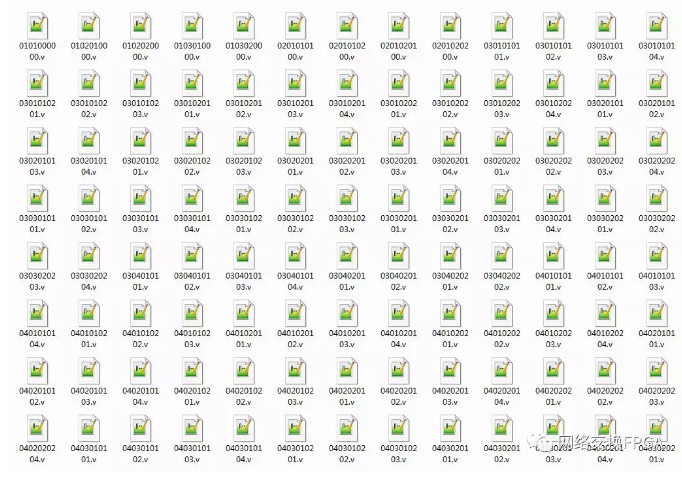

在做芯片仿真時,無論是采用自己搭建的簡單仿真環(huán)境還是UVM的仿真環(huán)境,最后的形式常常是把所有的testcase都集中到仿真環(huán)境中,只需敲一個命令,回車,所有的testcase就能夠全部運行下去。而仿真過程的錯誤,也都被記錄到log文件中,無論是運行的對與錯,都可以在log文件中看到。如下圖就是所有的testcase截圖,每個case運行的結(jié)果也會保存到另外一個log目錄下。

而FPGA開發(fā)人員,則不會去建立如此完善的仿真環(huán)境,往往是簡單的搭建一個某種功能模式下的仿真環(huán)境仿一下過了,就上板了。

采用ModelSim單獨仿真

1、整理RTL代碼及仿真代碼

如果要用ModelSim單獨仿真,并且需要搭建類似于上面描述的采用腳本形式來仿真的仿真環(huán)境,那么第一步就需要從Vivado工程中把相應(yīng)的Verilog代碼整理出來。

Vivado跟Quartus在仿真時采用的思路是不一樣的,對于Quartus而言,你可以很容易就能脫離開Quartus單獨搭建一個ModelSim或者VCS的仿真環(huán)境,因為Quartus所有的IP核或者原語庫之類的內(nèi)容全部都是以verilog或者VHDL文件存儲的,建仿真環(huán)境時,只需要到Quartus的安裝路徑下找一個叫EDA的目錄下找sim_lib的子目錄下找相應(yīng)的.v文件添加到仿真工程里就可以了,常見的庫文件主要有三個,220model.v,altera_mf.v和cyclone_atoms.v(或者是別的FPGA型號)。見本公眾號之前的文章有詳細描述:用Quartus II和ModelSim做后仿真(時序仿真)。

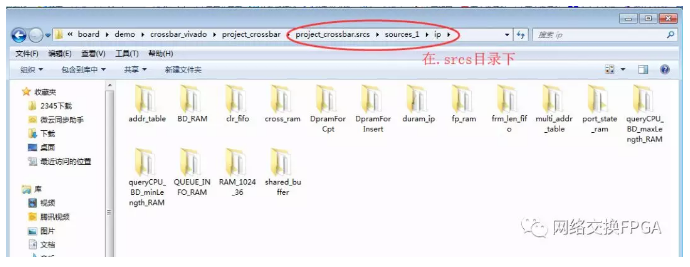

在Vivado中也有類似于Quartus中的庫文件,在Vivado工程目錄下,如下圖所示。

然后,整體拷貝ip文件夾到自己想搭建的modesim仿真環(huán)境目錄下:

上圖中rtl文件夾就是自己原來的設(shè)計文件,tb則是一些仿真用的.v文件。

2、編寫腳本sim.do文件

一個比較簡單的modelsim腳本文件如下。

vlib work vlog -f ./rtl.f vsim -novopt work.tb_crossbar_top do wave.do run 10us

上面的腳本的具體含義,大家都可以百度搜索找到。需要說明的是所有工程中的文件的路徑是需要寫到一個rtl.f的文件夾下的,具體源代碼可以參考本公眾號之前的文章:如何快速生成Verilog代碼文件列表?(內(nèi)附開源C代碼),需要注意的是,生成的文件路徑地址中的斜杠與modelsim腳本中要求的斜杠剛好相反,可以直接采用文本編輯器替換掉,也可以添加以下子函數(shù)到C代碼中簡單修改一下。

void xiegang(char* s)

{

int i,j,k;

char buf[800]=" ";

char buf1[800]=" ";

memset(buf,0,800);

memset(buf1,0,800);

strcpy(buf,s);

strcpy(buf1,s);

for(i=0;i

if(buf[i]=='//')

{

buf1[i]='/';

}

}

strcpy(s,buf1);

}

上面的C代碼實現(xiàn)文件列表的程序,其實也是腳本。

3、注意事項

在實現(xiàn)的過程中,發(fā)現(xiàn)Vivado并沒有把所有用到的庫文件都寫成.v的形式,而是以編譯庫的形式存在。這樣就需要在仿真時把對應(yīng)的庫文件包含進去。上面的腳本需要修改為:

vlib work vlog -f ./rtl.f #vsim -novopt work.tb_crossbar_top vsim -gui work.tb_crossbar_top -voptargs="+acc" -L C:/modeltech64_10.5/vivado_17_2/simprims_ver -L C:/modeltech64_10.5/vivado_17_2/unisims_ver do wave.do run 10us

C:/modeltech64_10.5/vivado_17_2/simprims_ver

C:/modeltech64_10.5/vivado_17_2/unisims_ver

兩個庫都是Vivado與ModelSim聯(lián)合仿真時ModelSim預(yù)先編譯好的仿真庫,這里面很多都是FPGA上用到的BUFG、PLL等內(nèi)容。但添加完這些庫文件后,還是有錯誤,具體如下:

經(jīng)過上網(wǎng)查找原因,發(fā)現(xiàn)這是xilinx全局復(fù)位的模塊。該模塊在C:/Xilinx/Vivado/2015.1/data/verilog/src路徑其實在上面Error提示的一部分。

于是,自己copy一份glbl.v到當前工程,進行編譯。

但還是彈出相同的錯誤提示。

最后,在tb.v中添加該模塊的調(diào)用才最終解決問題。

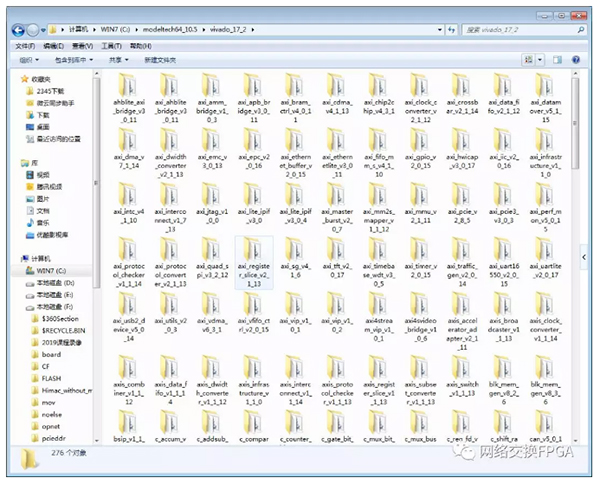

在筆者嘗試多個工程之后,發(fā)現(xiàn)找Vivado 對應(yīng)的庫實在是太麻煩了,那么多的編譯出來的庫,每個庫也找不到具體解釋含義的說明文檔。無奈之下,想到了徹底擺脫Vivado的終極解決方案。

出現(xiàn)了找不到某個模塊定義的錯誤之后,就需要嘗試著去添加上圖中不知道含義的庫看能不能解決問題,一個一個的試,一個一個的試,試到懷疑人生。

終極方案

這個終極解決方案就是采用ASIC的思路來替換掉所有的IP。如果考慮最后要做ASIC,那么就需要把設(shè)計代碼中所有的FGPA IP核或者原語之類的內(nèi)容全部替換掉,比如FIFO都要修改成控制邏輯加RAM的形式,一些BUFG之類的改善時序或驅(qū)動的原語也全部刪掉。如果只考慮做仿真,則只需要自己手寫一個RAM的行為邏輯,定義一個數(shù)組類型,根據(jù)輸出的時候是否打拍隨意的調(diào)整。一些FIFO也可以很容易的在網(wǎng)上找到源代碼,同步的,異步的,首字置出的FIFO都有。替換干凈之后,就跟Vivado沒有任何關(guān)系了!甚至也跟ModelSim也沒有任何關(guān)系了,可以隨意的更換仿真工具,比如VCS和NC等,徹底的解決問題。

寫到此處,想起了一個有趣的事情。據(jù)說有一種永遠不讓代碼中出現(xiàn)BUG的終極解決方案。猜猜看是什么。

答案是:不要寫一行代碼!

這個跟擺脫Vivado單獨建仿真環(huán)境的終極解決思路竟然高度一致!徹底擺脫Vivado建仿真環(huán)境的方法也是,仿真代碼中不要用到Vivado中的任何一個IP核!!!

4、覆蓋率分析

有了腳本的支持,也脫離掉了Vivado的束縛,就可以做很多自己想做的事情,把仿真環(huán)境做成可回歸的形式之后就可以做覆蓋率分析。這時的腳本就修改成如下的樣子。

vlib work vlog -f ../filelist/filelist_sim.v vlog -f ../filelist/filelist_hdl.v -cover bcesxf vsim -novopt -coverage work.TESTBENCH -L C:/modeltech64_10.5/vivado_17_2/simprims_ver -L C:/modeltech64_10.5/vivado_17_2/unisims_ver run -all

大家可能注意到,上面腳本中把filelist分成了兩種,一種是仿真的,不用看覆蓋率,另外一種則是可綜合代碼部分,需要看覆蓋率,單獨寫到了filelist_hdl.v的文件里面。

運行結(jié)束后,就可以在圖形界面上看到覆蓋率分析的結(jié)果。

隨著測試例的運行,上面設(shè)計代碼的覆蓋率也會逐漸提高,最后可以通過選擇達不到覆蓋率要求的模塊進行詳細的分析,查看測試例沒有運行到的語句。有了充分的仿真驗證后,再上板就順利的多了。至少99%的邏輯BUG都被解決掉了,剩余的就是一些時序方面的問題,這樣就可以大大節(jié)約FPGA調(diào)試的時間。

用做芯片的思路去做FPGA,不是殺雞用牛刀,而是一種正確的思路。搭建一個完善的仿真驗證環(huán)境固然麻煩,但一旦做好之后,事半功倍,效率會大幅度的提升。本文中提到的仿真環(huán)境僅僅是一種最簡單的只有Verilog代碼的仿真環(huán)境,在驗證復(fù)雜度和便捷性等方面都差的很遠遠。公司里面目前采用的辦法,往往是大牛們用SV搭建好一個UVM框架后,下面做具體實現(xiàn)的人只需要往對應(yīng)框里面填數(shù)字就可以了。

工欲善其事,必先利其器!做FPGA,仿真驗證就是器!

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618728 -

Vivado

+關(guān)注

關(guān)注

19文章

835瀏覽量

68813

發(fā)布評論請先 登錄

Vivado無法選中開發(fā)板的常見原因及解決方法

北京建工六建集團與軟通動力達成戰(zhàn)略合作

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

《聊一聊ZXDoc》之CAN總線仿真、面板仿真

一文詳解Vivado時序約束

Vivado Design Suite用戶指南:邏輯仿真

每次Vivado編譯的結(jié)果都一樣嗎

如何利用TPA2012D2的輸出端和阻抗值4OHM的喇叭建一個cadence仿真模型?

使用Vivado通過AXI Quad SPI實現(xiàn)XIP功能

Vivado使用小技巧

基于PFGA的脫離Vivado單獨建仿真環(huán)境工程

基于PFGA的脫離Vivado單獨建仿真環(huán)境工程

評論