基于FPGA vivado 17.2 的數字鐘設計

2018-06-08 09:41:47 10211

10211

01. Vivado的兩種工作模式 Vivado設計有工程和非工程兩種模式: 1. 工程模式: 工程模式是使用Vivado Design Suite自動管理設計源文件、設計配置和結果,使用圖形化

2020-11-09 17:15:47 3916

3916

作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3176

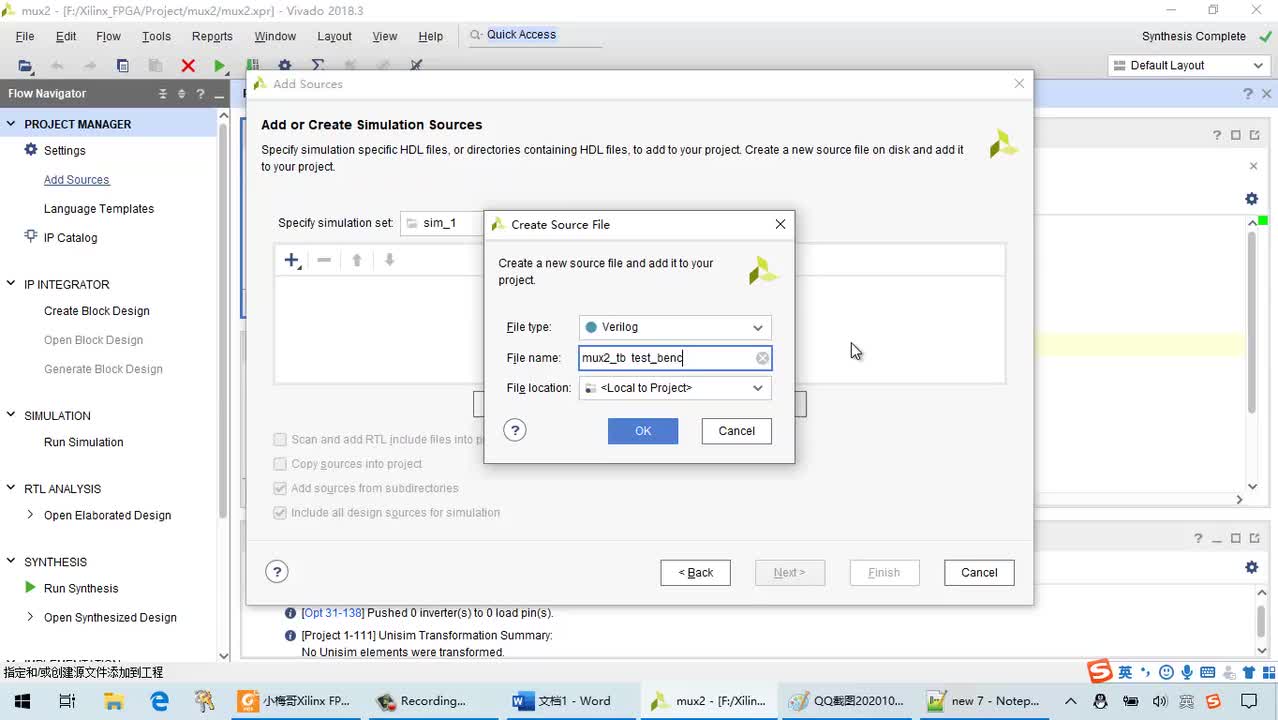

3176 仿真功能概述 仿真FPGA開發中常用的功能,通過給設計注入激勵和觀察輸出結果,驗證設計的功能性。Vivado設計套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 4739

4739

FPGA 的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟 IC 設計流程類似,可以分為前端設計和后端設計。

2023-04-23 09:08:49 1643

1643

。Axcelerator和Vivado是常用的綜合工具,其中Vivado是由Xilinx公司開發的EDA工具。

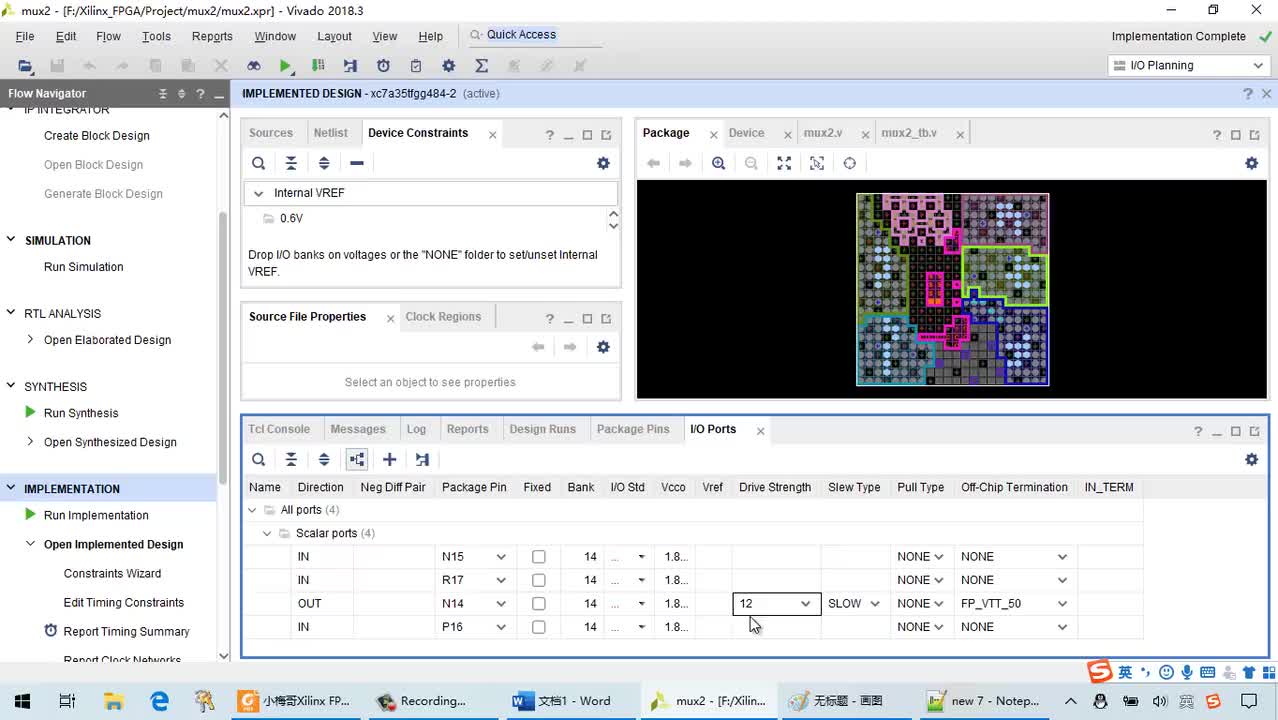

在布局布線方面,FPGA工程師需要使用工具將邏輯網表傳輸到物理布局中。在這個過程中

2023-11-09 11:03:52

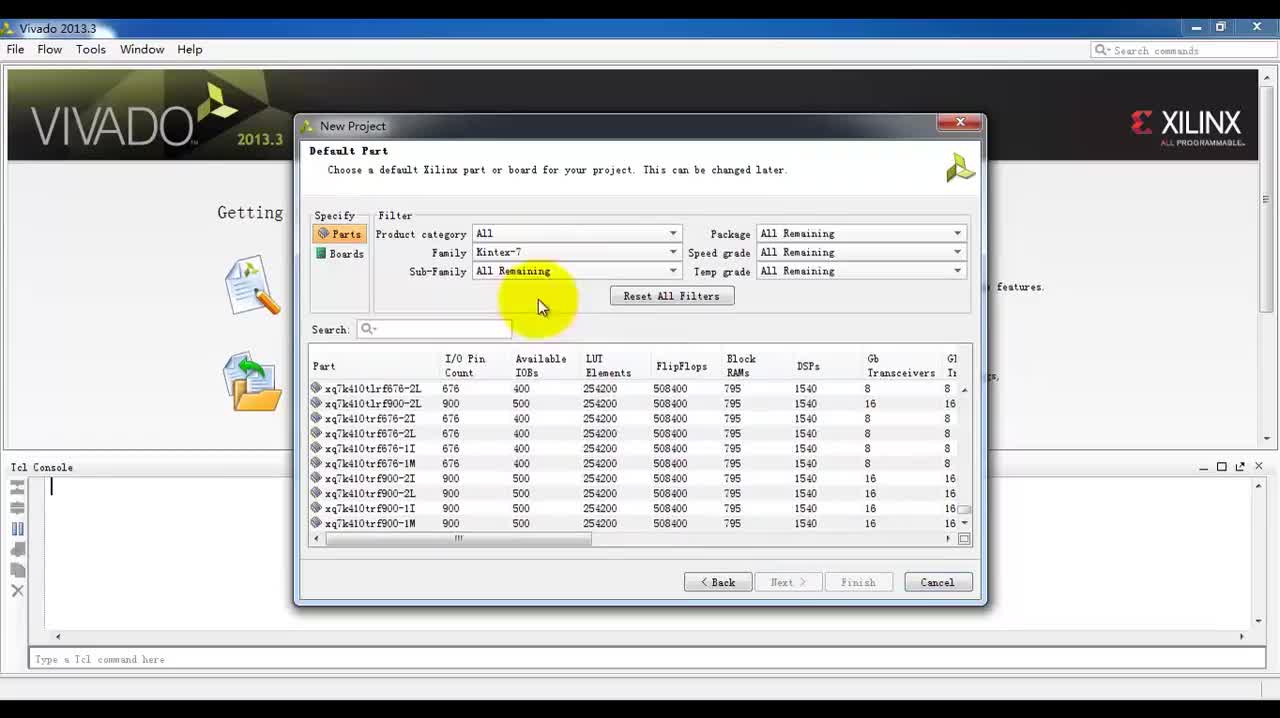

一、總體流程開發工具:Vivado2020VerilogARTIX-7 FPGA AX7035這是我做的完整流程,涉及到初級開發的功能;新建工程:(RTL Project)芯片選型;編寫程序:源文件

2021-07-22 07:35:26

驗證無誤,則可以生產下載配置文件燒錄的實際器件中進行板級的調試工作。圖5.15 FPGA/CPLD開發流程當然了,對于沒有實際工程經驗的初學者而言,這個流程圖可能不是那么容易理解。不過沒有關系,我們會

2019-01-28 02:29:05

、板級仿真以及芯片編程與調試等主要步驟。圖1-10 FPGA開發的一般流程1.電路功能設計在系統設計之前,首先要進行的是方案論證、系統設計和FPGA芯片選擇等準備工作。系統工程師根據任務要求,如系...

2021-07-23 09:12:07

,這也就要求設計者從設計一開始就要非常認真細致,來不得半點的馬虎,否則后續的很多工作量可能就是不斷的返工。(特權同學版權所有)1.6 FPGA開發流程當然了,對于沒有實際工程經驗的初學者而言,這個流程

2015-03-31 09:27:38

,這也就要求設計者從設計一開始就要非常認真細致,來不得半點的馬虎,否則后續的很多工作量可能就是不斷的返工。(特權同學版權所有)圖1.6 FPGA開發流程當然了,對于沒有實際工程經驗的初學者而言,這個

2019-01-28 04:24:37

II、Vivado等)、仿真軟件(ModelSim等)的使用5、熟悉FPGA設計流程(仿真,綜合,布局布線,時序分析)。6、熟練掌握資源估算(特別是slice,lut,ram等資源的估算)。7、同步

2020-10-22 17:08:15

Vivado概述 / 251.3.1 Vivado下的FPGA設計流程 / 251.3.2 Vivado的兩種工作模式 / 261.3.3 Vivado的5個特征 / 30參考文獻 / 31第2章

2020-10-21 18:24:48

`Vivado 開發環境簡介及設計流程`

2017-12-12 10:15:48

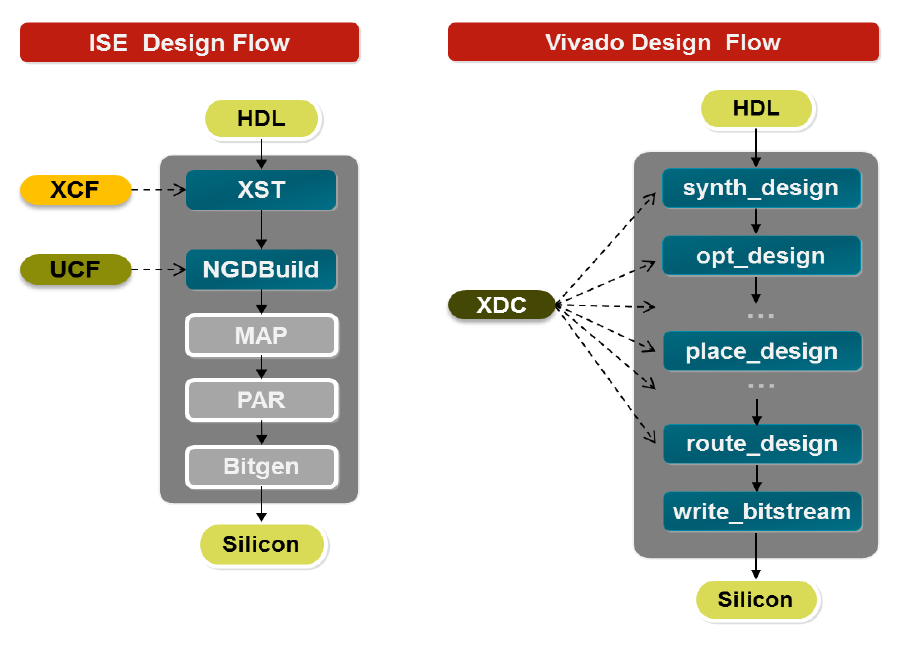

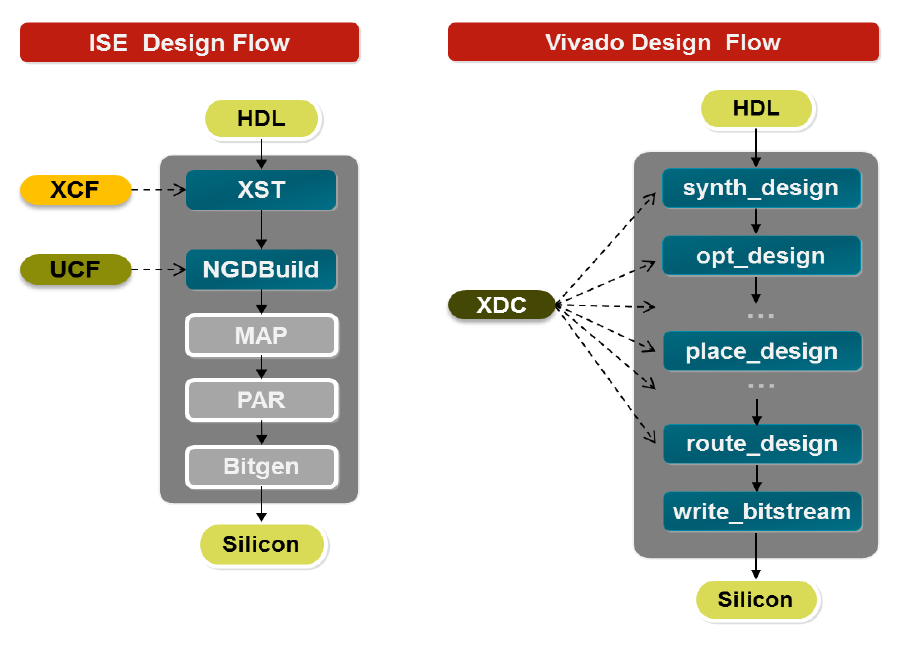

不支持更老的設備(Spartan, Virtex-6 以及之前的 FPGA) 。同樣 ,ISE 也不再支持 7 系列之后的設備ISE 和 Vivado 之間另一個重要的區別就是約束文件的類型。在 ISE

2021-01-08 17:07:20

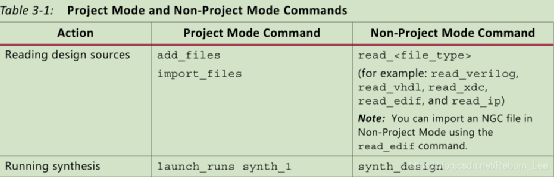

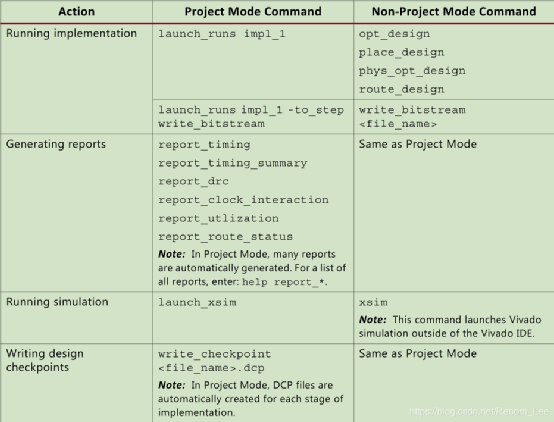

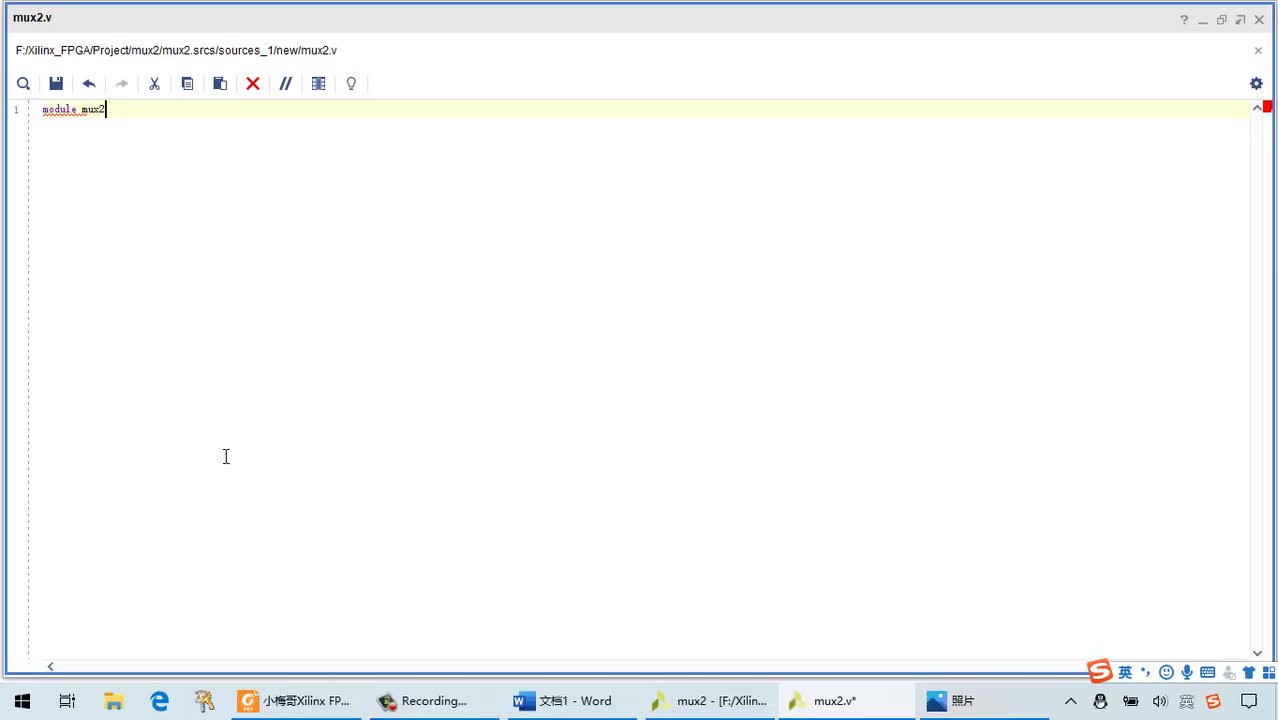

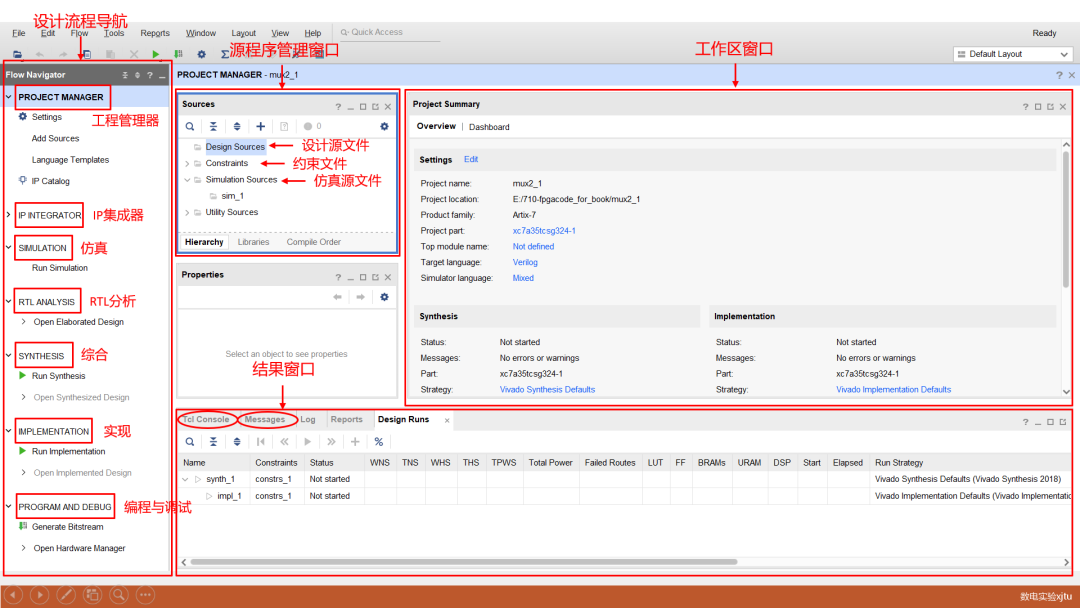

Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程。

2023-09-20 07:37:39

下面b) 采用manage IP的設計流程11.把自己的代碼封裝成一個IP,初學xilinx的fpga設計,好多東西都沒有概念,真是一頭霧水,比起Altera的開發環境,這個vivado真的是困難太多

2016-11-09 16:08:16

本書收集整理了作者在FPGA學習和實踐中的經驗點滴。書中既有日常的學習筆記,對一些常用設計技巧和方法進行深入探討;也有很多生動的實例分析,這些實例大都是以特定的工程項目為依托,具有一定的借鑒價值

2014-12-29 16:57:26

分析,這些實例大都是以特定的工程項目為依托,具有一定的借鑒價值;還有一些適合于初學者入門和進階學習的實驗例程;另外還給出了兩個比較完整的DIY工程,讓讀者從系統角度理解FPGA的開發流程。第一部

2012-02-27 10:45:37

LabVIEW 深入探索

2015-07-01 10:54:43

LabVIEW_深入探索

2012-08-31 13:53:31

`LabVIEW_深入探索`

2012-08-19 13:38:42

Labview 深入探索

2013-04-11 18:09:31

Labview深入探索的很好資料哦

2012-04-27 21:29:59

在撥號界面輸入“*#*#3646633#*#*”會出現一個界面,這個界面就是工程模式設置界面。下面對聽筒音量進行調整。選擇Hardware Testing --> AUDIO,先修改

2016-09-18 21:06:00

我剛剛在 STMCubeIDE 中為 STM32MP157A-DK1 創建了一個項目,并嘗試在工程模式和生產模式下運行 MCU 調試。我使用 ST-LINK 線和 Ethernet Over USB

2022-12-12 08:25:41

本帖最后由 夏良濤FPGA 于 2020-4-9 12:33 編輯

XILLINX VIVADO快速上手-HDL流程-內含視頻、工程和中文版ppt200多M大小 只能網盤了。鏈接:https://pan.baidu.com/s/1wNkSIJeO7G86YGjy0CtJ6g 提取碼:zjev

2020-04-09 11:30:45

開發設計流程。話不多說,上貨。Xilinx FPGA Vivado 開發流程在做任何設計之前,我們都少不了一個工作,那就是新建工程,我們設計的一些操作,必須在工程下完成,那么接下來就向大家介紹一下新建工程的步驟

2023-04-13 15:18:52

開發過程中的一個重要特點,這就要求設計者從一開始就要非常認真細致,否則后續的很多工作量可能就是不斷的返工。圖1.32 FPGA開發流程 基于Xilinx的Vivado開發工具,我們對以上開發流程所涉

2019-04-01 17:50:52

技術學習。現正在進行fpga技術學習心得的整理和歸納,《小梅哥和你一起深入學習Fpga》目前正在各大論壇持續更新。現擔任至芯科技工程師,負責至芯科技大學計劃校內實訓項目工程,在至芯科技擔任FPGA

2014-11-21 14:47:53

。界面如下圖所示,與Xilinx Vivado軟件類似,主界面也是由工具欄、工程目錄、代碼編輯、調試信息組成。Keil軟件的主要作用是將C語言/匯編語言寫的程序編譯成機器碼,在進入調試模式時,通過調試器

2022-04-01 17:48:02

善用Vivado工程配置文件xpr快速工程創建對于第一次新建工程,沒啥捷徑,建議大家規規矩矩的使用Vivado的GUI創建工程。完成工程創建后,我們找到這個新建工程下的.xpr文件,它是工程配置文件

2016-10-19 18:05:13

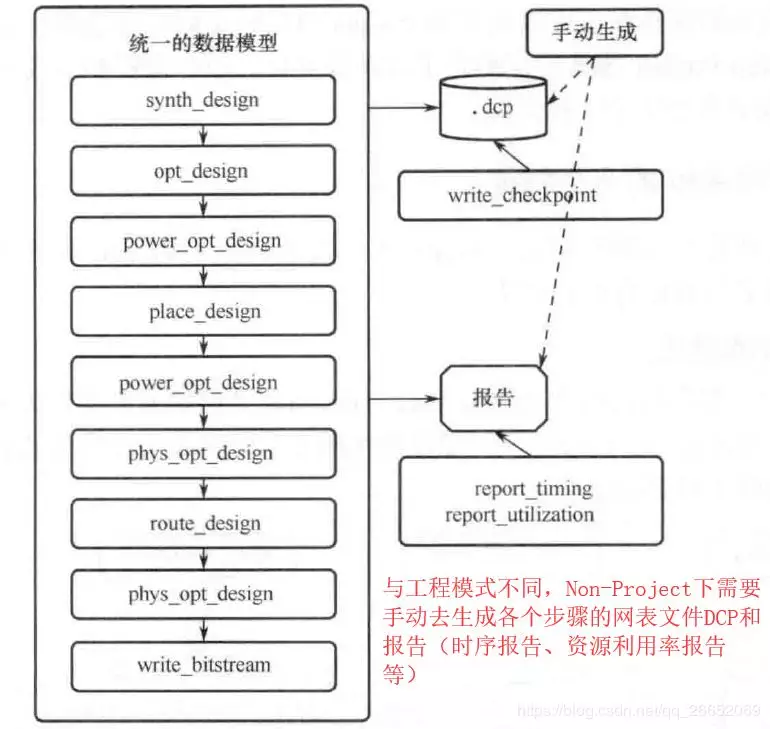

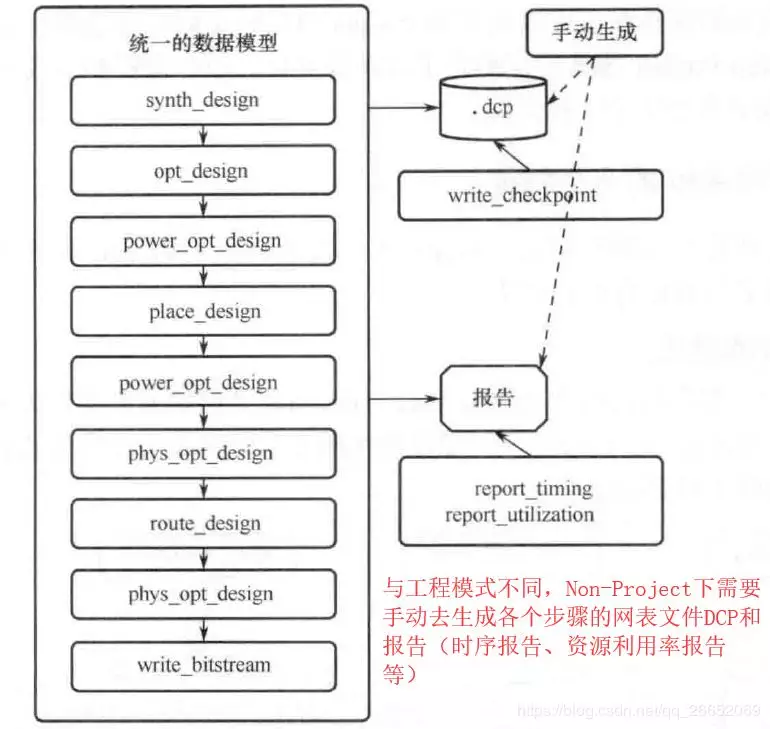

,Vivado工具可自動管理設計流程和設計數據,各種數據都比較直觀。非工程模式是一直內存編譯流程,所有步驟都需要開發者手動編輯腳本,命令和參數,這樣的模式開發者對設計流程有完全的掌控力。目前,更多的人

2022-06-17 14:52:14

、書籍、源碼、技術文檔…(2023.07.09更新)

本篇掌握基于 FPGA Vivado 信號發生器設計(附源工程),掌握基于添加文件和IP的Vivado工程設計流程,掌握基于Tcl

2023-08-15 19:57:56

今天給大俠帶來基于 FPGA Vivado 的數字鐘設計,開發板實現使用的是Digilent basys 3。話不多說,上貨。

需要源工程可以在以下資料獲取里獲取。

資料匯總|FPGA軟件安裝包

2023-08-18 21:18:47

今天給大俠帶來基于 FPGA Vivado 示波器設計,開發板實現使用的是Digilent basys 3,話不多說,上貨。

需要源工程可以在以下資料獲取里獲取。

資料匯總|FPGA軟件安裝包

2023-08-17 19:31:54

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2022-02-07 08:02:04

基于FPGA vivado 17.2 的數字鐘設計目的:熟悉vivado 的開發流程以及設計方法附件:

2017-12-13 10:16:06

、SW撥碼開關以下是官網提供的資料鏈接:arty a7開發板資料Pmod DA4資料vivado安裝說明board files添加基于microblaze的vivado開發流程以下是在vivado2017.4_MicroBlaze_ArtyA735t上的開發流程新建工程注:路徑不要有中文名,電

2022-01-18 08:09:43

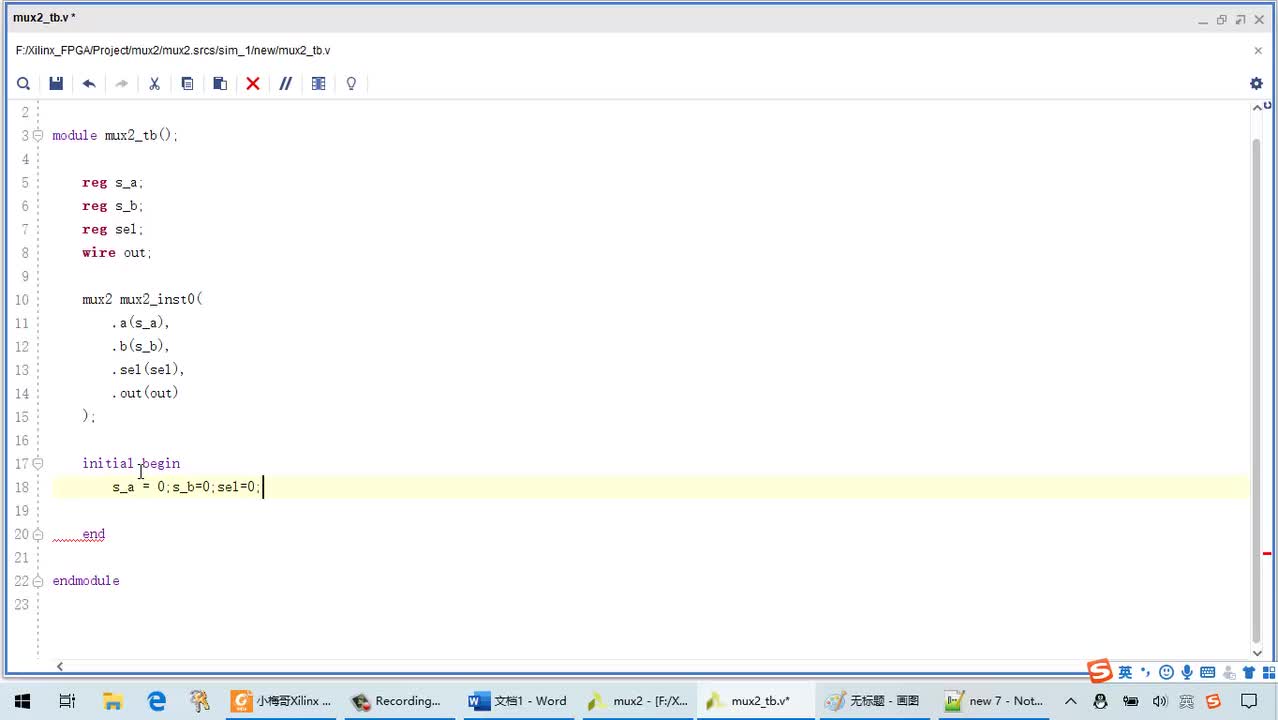

程序來選擇工具。 3. 創建Vivado工程 3.1 首先建立按鍵的測試工程,添加verilog測試代碼,完成編譯分配管腳等流程。 `timescale1ns/1ps module

2021-01-06 17:48:21

看了《小梅哥和你一起深入學習FPGA之FPGA設計流程》受益匪淺,所以做個pdf方便大家。

2015-02-04 09:39:22

、USB、Micro SD、CAN、UART等接口,支持LCD顯示拓展及Qt圖形界面開發,方便快速進行產品方案評估與技術預研。HLS基本開發流程如下:HLS工程新建/工程導入編譯與仿真綜合IP核封裝IP核

2021-11-11 09:38:32

非工程模式下對應的Tcl 命令。右圖所示是 Vivado 中設計實現的基本流程,藍色部分表示實現的基本 步驟(盡管opt_design 這一步理論上不是必選項,但仍強烈建議用戶執行),對應

2023-06-28 19:34:58

轉帖:采用高級語言開發FPGA的探索近年來,由于人工智能和金融數據分析等計算密集型領域的日益興起,異構計算越來越受到大家的重視。異構計算是指使用不同類型指令集和體系架構的計算單元組成系統的計算方式

2017-09-25 10:06:29

MTK平臺手機進入工程測試模式指令大全

目前MTK平臺的開發手機型號越來越多,對應的進工程模式的指令也隨之五

2009-12-28 08:13:29 6648

6648 東芝液晶電視工程模式的常用功能(4:3電視不適用): 開機狀態下,按一次遙控器的Mute鍵(靜音鍵),然后按住遙控器的Mute鍵的同時按電視機的Menu鍵,即可進入工程菜單

2012-05-14 17:07:04 19505

19505 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。 基本的FPGA設計實現流程 FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。

2017-11-18 01:48:01 3325

3325

資源、速度和功耗是FPGA設計中的三大關鍵因素。隨著工藝水平的發展和系統性能的提升,低功耗成為一些產品的目標之一。功耗也隨之受到越來越多的系統工程師和FPGA工程師的關注。Xilinx新一代開發工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優化。

2017-11-18 03:11:50 4916

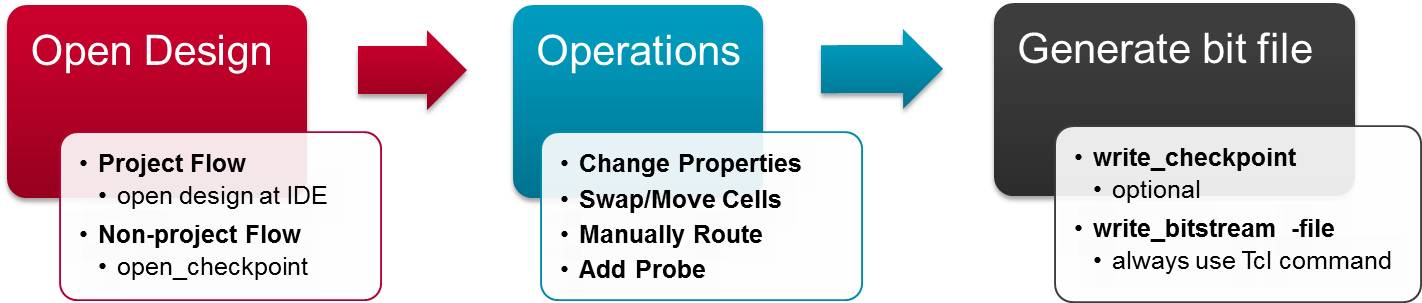

4916 關于Tcl在Vivado中的應用文章從Tcl的基本語法和在Vivado中的應用展開,介紹了如何擴展甚至是定制FPGA設計實現流程后,引出了一個更細節的應用場景:如何利用Tcl在已完成布局布線

2017-11-18 18:26:46 5003

5003

不斷 從賽靈思FPGA設計流程看懂FPGA設計 1.XILINX ISE傳統FPGA設計流程 利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 15845

15845

本文首先介紹了FPGA發展由來,其次介紹了FPGA的硬件設計技巧及FPGA設計者的5項基本功,最后介紹了FPGA設計流程及工程師FPGA設計心得體會。

2018-05-31 09:35:06 11261

11261 Vivado不僅是xlinx公司的FPGA設計工具,用它還可以學習Verilog描述,你造嗎?

2018-09-20 09:29:22 9458

9458 我們以8-bit 的LFSR(線性反饋移位寄存器)做一個流水燈為例,介紹Vivado的基本使用。

2018-09-25 16:16:36 14495

14495

單片機是基于FLASH結構的,所以單片機上電直接從本地FLASH中運行。但SRAM 架構的FPGA是基于SRAM結構的,掉電數據就沒了,所以需要借助外部電路來配置運行的數據,其實我們可以借助Vivado來學習FPGA的各種配置模式。

2018-11-05 15:12:57 7323

7323 這兩個選項可幫助降低控制集。但這兩個選項不能與-directive同時使用,所以如果是工程模式下,可將其放置在Hook文件中(Tcl.pre或Tcl.post)。非工程模式下,可在執行完-directive之后,再次執行這兩個選項;

2018-11-07 11:11:32 5093

5093

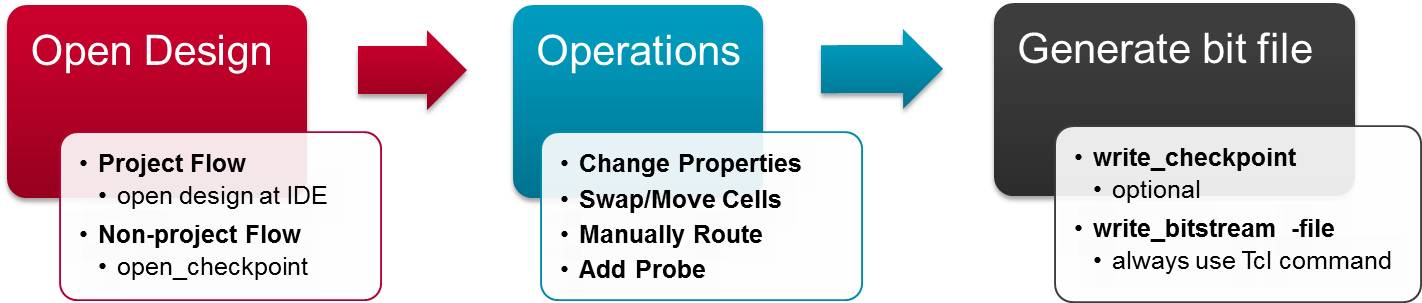

了解如何在Vivado中執行工程變更單(ECO)。

本視頻將向您介紹ECO的常見用例,我們推薦的完成ECO的流程,優勢和局限性,并將演示功能設計的ECO。

2018-11-21 06:40:00 4670

4670

中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-06 06:12:00 3471

3471

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:06:00 2182

2182

中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-04 07:05:00 1317

1317

本文檔的主要內容詳細介紹的是Vivado的安裝生成bit文件及燒錄FPGA的簡要流程教程免費下載。

2019-06-18 08:00:00 25

25 第一步所指的Design通常是完全布局布線后的設計,如果是在工程模式下,可以直接在IDE中打開實現后的設計,若是僅有DCP文件,不論是工程模式或是非工程模式產生的DCP,都可以用open_checkpoint命令打開。

2019-07-25 09:27:05 2479

2479

工程模式的關鍵優勢在于可以通過在Vivado 中創建工程的方式管理整個設計流程,包括工程文件的位置、階段性關鍵報告的生成、重要數據的輸出和存儲等。

2019-07-24 17:30:38 4234

4234

從 Vivado 2019.1 版本開始,Vivado 綜合引擎就已經可以支持增量流程了。這使用戶能夠在設計變化較小時減少總的綜合運行時間。

2019-07-21 11:02:08 1376

1376 Tcl介紹 Vivado是Xilinx最新的FPGA設計工具,支持7系列以后的FPGA及Zynq 7000的開發。與之前的ISE設計套件相比,Vivado可以說是全新設計的。無論從界面、設置、算法

2020-11-17 17:32:26 2142

2142 ? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9615

9615 FPGA的開發流程是遵循著ASIC的開發流程發展的,發展到目前為止,FPGA的開發流程總體按照下圖進行,有些步驟可能由于其在當前項目中的條件的寬度的允許,可以免去,比如靜態仿真過程,這樣來達到項目

2020-10-25 10:05:37 3610

3610

帶大家一起體驗一下Vivado 的ECO流程,以vivado自帶的Example Design為例, 直接用TCL命令修改網表,在正常的寄存器路徑之間加一級LUT。 1. 打開Vivado 界面 2. 打開

2020-10-26 09:45:23 3401

3401

這里帶大家一起體驗一下Vivado 的ECO流程,以vivado自帶的Example Design為例, 直接用TCL命令修改網表,在正常的寄存器路徑之間加一級LUT。

2020-11-29 11:04:53 3896

3896

本文主要介紹如何使用Vivado 開發套件創建硬件工程。

2021-02-02 07:13:32 18

18 Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程。

2021-03-22 11:39:53 49

49 Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程

2021-03-25 14:39:13 28

28 參考:UG892 UG835 Vivado集成開發工具為設計者提供了非工程模式下的FPGA設計流程。在Vivado非工程模式下,FPGA開發人員可以更加靈活地對設計過程的每個階段進行控制,從而進一步

2021-06-19 10:52:47 2248

2248

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 26

26 傳統的FPGA開發都是通過GUI界面進行相關的“按鈕”式操作,Vivado則在引入Tcl解釋器后,可以通過非工程模式進行操作,一個Tcl腳本即可自動化建立工程,對工程進行分析。

2022-04-07 15:02:29 5448

5448 在 Windows 下,我喜歡在批處理模式下運行 Vivado 仿真器。 我創建了仿真批文件 (.bat) ,包含以下命令。當我運行批文件,執行第一條命令后腳本中止。如何正確在批模式下運行 Vivado 仿真器?

2022-08-01 09:43:01 745

745 Vivado可以導出腳本,保存創建工程的相關命令和配置,并可以在需要的時候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠遠小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級到Vivado 2020.2為例,討論如何升級Vivado工程腳本。

2022-08-02 10:10:17 1569

1569 一個完整的vivado工程往往需要占用較多的磁盤資源,少說幾百M,多的甚至可能達到上G,為節省硬盤資源,可以使用Tcl命令對vivado工程進行備份,然后刪除不必要的工程文件,需要時再恢復即可。

2022-08-02 15:01:06 3749

3749 盡管FPGA的配置模式各不相同,但整個配置過程中FPGA的工作流程是一致的,分為三個部分:設置、加載、啟動。

2022-10-10 14:37:57 1290

1290 vivado有project模式和non-project模式,project模式就是我們常用的方式,在vivado里面新建工程,通過GUI界面去操作;non-project模式就是純粹通過tcl來指定vivado的流程、參數。

2022-10-17 10:09:29 2037

2037 系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,Vivado開發軟件開發設計流程。話不多說,上貨。

2023-02-21 09:16:44 2884

2884 今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 706

706

關于 Tcl 在 Vivado中的應用文章從 Tcl 的基本語法和在 Vivado 中的 應用展開,繼上篇《用 Tcl 定制 Vivado 設計實現流程》介紹了如何擴展甚 至是定制 FPGA

2023-05-05 15:34:52 1682

1682

FPGA開發過程中,vivado和quartus等開發軟件都會提供時序報告,以方便開發者判斷自己的工程時序是否滿足時序要求。

2023-06-26 15:29:05 543

543

vivado的工程創建流程對于大部分初學者而言比較復雜,下面將通過這篇博客來講解詳細的vivado工程創建流程。幫助自己進行學習回顧,同時希望可以對有需要的初學者產生幫助。

2023-07-12 09:26:57 1205

1205

vivado開發軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學者進行仿真實驗。

2023-07-18 09:06:59 2275

2275

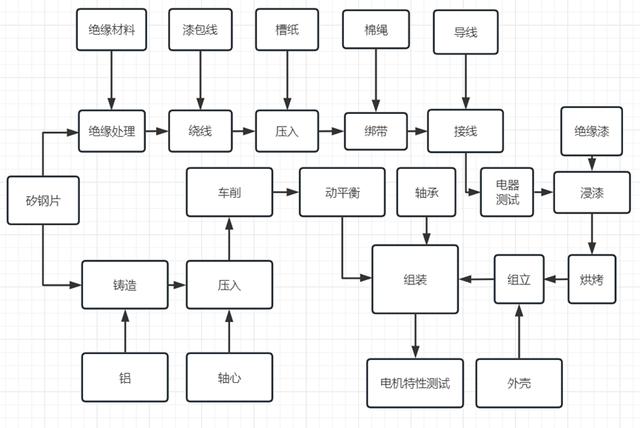

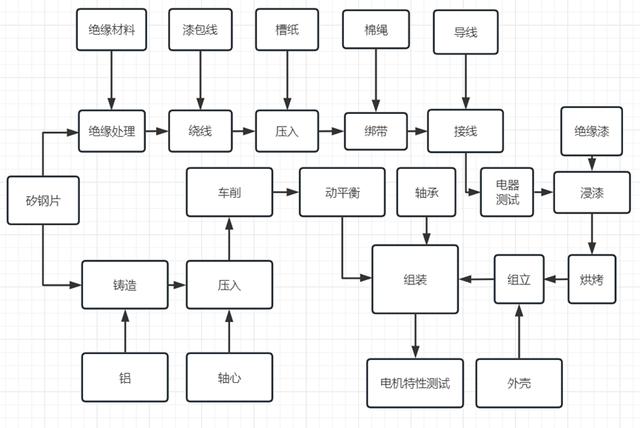

本文將深入探索感應馬達的生產過程。盡管各廠商的馬達細節設計有所異同,我們還是將以最基礎的生產模式為主要脈絡來進行闡述。

2023-08-16 16:23:30 829

829

電子發燒友網站提供《Vivado設計套件用戶指南(設計流程概述).pdf》資料免費下載

2023-09-15 09:55:07 1

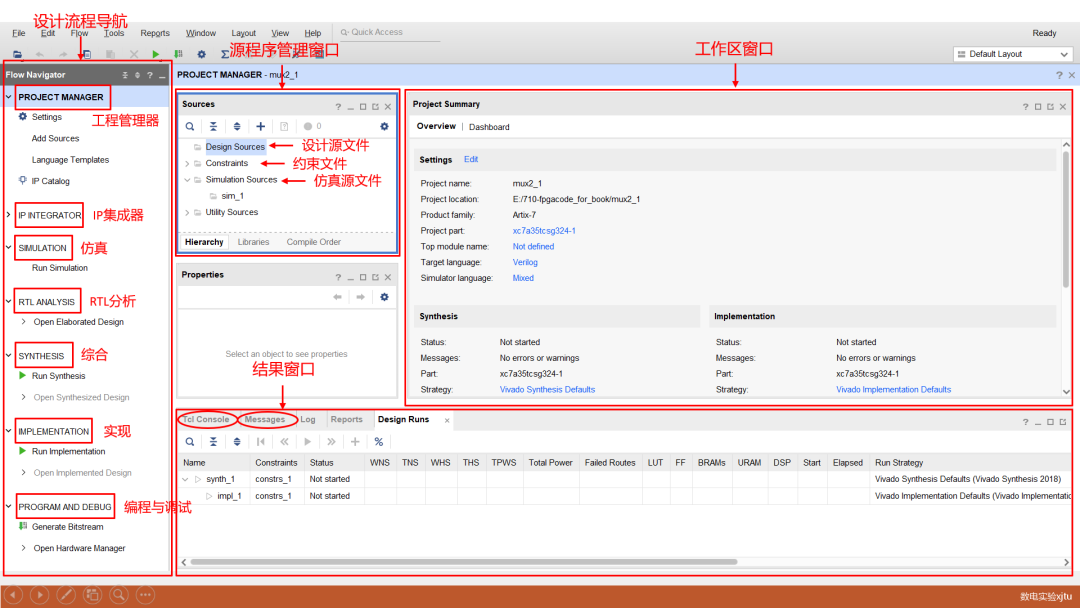

1 Vivado設計主界面,它的左邊是設計流程導航窗口,是按照FPGA的設計流程設置的,只要按照導航窗口一項一項往下進行,就會完成從設計輸入到最后下載到開發板上的整個設計流程。

2023-09-17 15:40:17 1548

1548

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 384

384 將設置設計的輸出路徑,設置設計輸出路徑的步驟如下所示。 第一步:如圖4.3所示,在“Vivado%”提示符后輸入命令“set outputDir ./gate_Created_Data/top_output”。

2024-04-03 09:34:05 34

34

電子發燒友App

電子發燒友App

評論