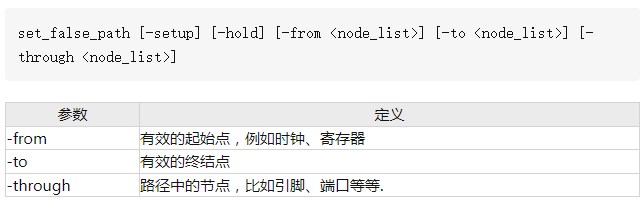

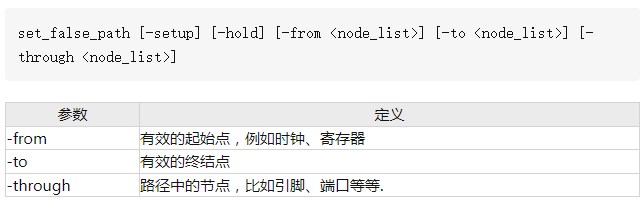

時序約束的目的就是告訴工具當(dāng)前的時序狀態(tài),以讓工具盡量優(yōu)化時序并給出詳細(xì)的分析報告。一般在行為仿真后、綜合前即創(chuàng)建基本的時序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進(jìn)行最基本時序約束相關(guān)腳本。

2022-03-11 14:39:10 8731

8731 FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設(shè)定的時鐘周期內(nèi)完成,更詳細(xì)一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 860

860

32位ARM嵌入式處理器的調(diào)試技術(shù)摘要:針對32位ARM處理器開發(fā)過程中調(diào)試技術(shù)的研究,分析了目前比較流行的基于JTAG的實時調(diào)試技術(shù),介紹了正在發(fā)展的嵌入式調(diào)試標(biāo)準(zhǔn),并展望期趨勢。關(guān)鍵詞:嵌入式

2021-12-14 09:08:18

本文以Altera公司的FPGA為目標(biāo)器件,通過開發(fā)實例介紹FPGA開發(fā)的完整的流程及開發(fā)過程中使用到的開發(fā)工具,包括QuartusII、FPGA CompilerII、Modelsim,并重點解說如何使用這三個工具進(jìn)行協(xié)同設(shè)計。

2021-04-29 06:04:13

的方法一般有四個步驟:時序分析→時序約束→時序報告→時序收斂。

為什么要進(jìn)行時序分析?

信號在系統(tǒng)中傳輸時由于經(jīng)過一些邏輯器件和PCB上的走線會造成一定的邏輯延時和路徑延時,如果系統(tǒng)要求信號

2011-09-23 10:26:01

FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設(shè)定的時鐘周期內(nèi)完成,更詳細(xì)一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

造成困難。 2. 時序修正 嚴(yán)格遵守Vivado開發(fā)流程,在第一次跑綜合時最好是在沒有任何物理約束的情況下,Vivado在越少物理約束的情況下綜合出來的效果越好。查看每個階段的時序報告,將每一階

2020-12-23 17:42:10

的,在有問題的時候能有人能夠解答,也是我感觸很深的一點,大家在帖子下方發(fā)出學(xué)習(xí)過程中遇到的問題,我會力所能及的回答大家的問題。希望大家在FPGA開發(fā)的道路上越來越順利。提問的范圍舉例:1、FPGA硬件

2019-10-14 10:08:35

CMOS攝像頭接口時序設(shè)計5時序報告(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-08-19 21:58:55

。 在FPGA的最初布局和布線完成后,時序報告提供數(shù)據(jù)總線中每個時序的詳細(xì)延時信息。如果有必要,可為FPGA開發(fā)系統(tǒng)的關(guān)鍵信號設(shè)定延時路徑,TimingDesigner軟件可以提取相關(guān)信息和利用圖表更新

2017-09-01 10:28:10

學(xué)習(xí)。個人學(xué)習(xí)的時候可以根據(jù)實際情況選擇最高至Vivado2019.1。(從Vivado2019.2開始,PS開發(fā)使用Vitis,沒有SDK了)第1章 FPGA技術(shù)分析 / 11.1 FPGA內(nèi)部結(jié)構(gòu)

2020-10-21 18:24:48

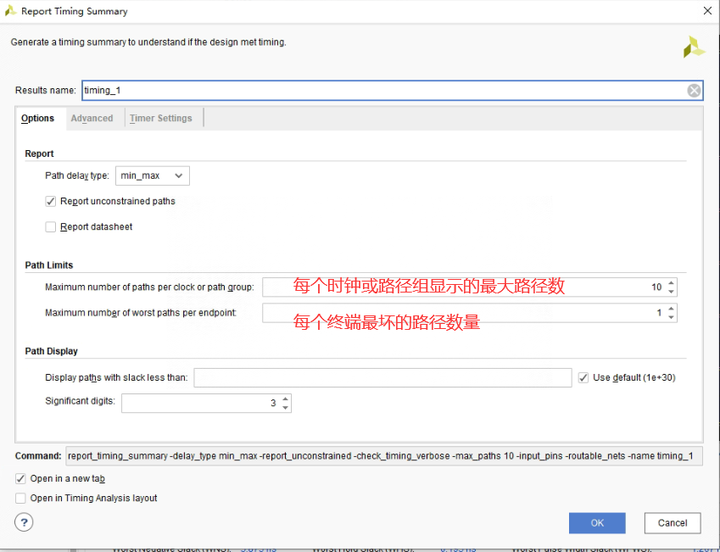

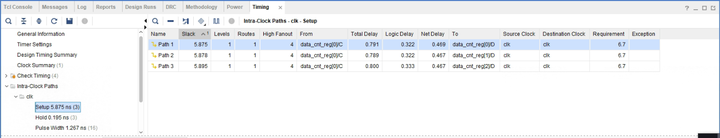

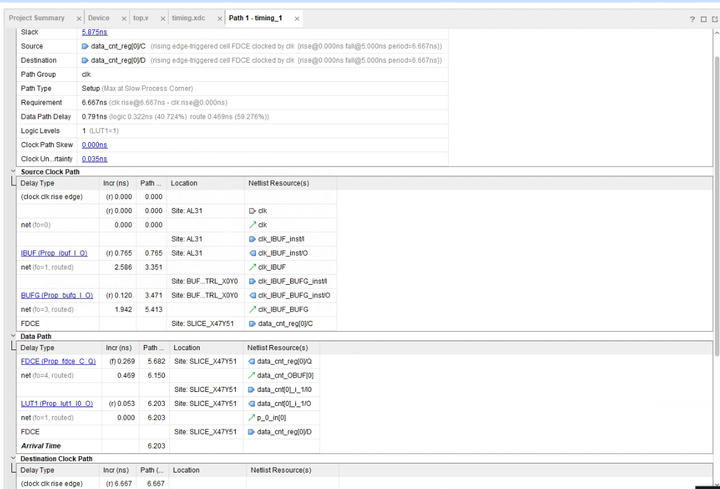

Vivado運行Report Timing Summary時,只顯示各個子項目最差的十條路徑,很可能并不包含你最關(guān)心的路近,這個時候顯示指定路徑的時序報告就顯得很重要了,下面就簡單介紹一下

2021-01-15 16:57:55

在學(xué)習(xí)fpga的過程中的疑問:1、在功能仿真和板級驗真后沒問題,還需要進(jìn)行時序分析嗎2、怎么知道自己寫的代碼有時序問題?

2017-01-08 17:50:35

最近用華大 HC32L176KATA開發(fā)過程中發(fā)現(xiàn)一個問題,引腳PC11控制LED指示燈,調(diào)用函數(shù)Gpio_WriteOutputIO(GpioPortC, GpioPin11, x&

2021-12-06 06:50:14

LabVIEW開發(fā)FPGA?開發(fā)過程是什么?有相關(guān)書籍資料嗎?

2015-08-10 21:08:55

JTAG設(shè)備STM32 匯編匯編中含C語言注釋數(shù)字信號處理濾波IIR濾波器本人STM32開發(fā)過程中的一些心得及總結(jié)。比較好的文章加密STM32MCU加密原理與方法 (很詳細(xì))驅(qū)動開發(fā)啟動使用CCMRAM內(nèi)...

2021-08-17 08:50:02

STM32開發(fā)過程中遇到的一些問題,記錄如下。Q1:下載后程序不運行,反復(fù)排查代碼沒問題。A1:棧空間太小,打開startup_stm32f10x_hd.s,把 Stack_Size EQU

2021-08-20 06:48:00

開發(fā)過程中的一個重要特點,這就要求設(shè)計者從一開始就要非常認(rèn)真細(xì)致,否則后續(xù)的很多工作量可能就是不斷的返工。圖1.32 FPGA開發(fā)流程 基于Xilinx的Vivado開發(fā)工具,我們對以上開發(fā)流程所涉

2019-04-01 17:50:52

進(jìn)行openharmony組件開發(fā)過程中,hi3516打開燒錄進(jìn)去的hap包顯示藍(lán)屏運行的hap包是官方的jsholleworld,上圖是打開app時后臺顯示的信息與設(shè)備的顯示畫面

2022-04-13 11:28:07

設(shè)計意圖以及性能的目標(biāo)和綜合工具之間的通信。設(shè)計一旦綜合完畢,這些約束和關(guān)鍵路徑信息將被自動注釋到Vivado設(shè)計套件的擺放和路由(P&R)工具中,進(jìn)一步確保滿足時序。 第二步:RTL代碼風(fēng)格

2019-08-11 08:30:00

為什么開發(fā)過程中有些不帶光耦隔離的繼電器需要引腳開漏輸出控制

2023-11-03 06:41:40

產(chǎn)品研發(fā)過程中EMC傳導(dǎo)發(fā)射預(yù)測試方法

2015-08-05 15:51:37

分享兩個開發(fā)過程中我最常用的文件

2016-10-25 14:23:12

**.**單片機(jī)開發(fā)過程中按鍵處理函數(shù)的實現(xiàn)?**.**方法一? 這種方法在單片機(jī)處理中反應(yīng)不夠好,當(dāng)按鍵交替按時,會表現(xiàn)的不夠好?voidKey_Scan(void){uint8_t

2021-11-22 06:03:41

Flash在我們生活中無處不在,比如:U盤、固態(tài)硬盤、SD卡、內(nèi)存卡等。同時,在單片機(jī)開發(fā)過程中也會遇到各種各樣的Flash,...

2021-12-09 08:00:20

單片機(jī)在組裝與開發(fā)過程中總是會出現(xiàn)一些問題,導(dǎo)致過程不是那么順利的完成。今日分享一些單片機(jī)常見問題的解決辦法1.單片機(jī)EN8F609兼容PIC12F629,僅有一個中斷入口,要避免多個中斷引發(fā)的沖突

2018-09-11 16:33:29

在FPGA開發(fā)過程中,編程與配置這兩個操作有什么區(qū)別?

2023-04-06 14:44:05

設(shè)計意圖以及性能的目標(biāo)和綜合工具之間的通信。設(shè)計一旦綜合完畢,這些約束和關(guān)鍵路徑信息將被自動注釋到Vivado設(shè)計套件的擺放和路由(P&R)工具中,進(jìn)一步確保滿足時序。第二步:RTL代碼風(fēng)格和關(guān)鍵

2021-05-18 15:55:00

今天在RT-Thread完整版開發(fā)過程中引入watchdog,踩到一個坑,系統(tǒng)一直重啟,喂狗一直失敗,搞了一天才解決,總結(jié)一下。我的RT-Thread完整版系統(tǒng)是最新版4.0.3(截止2020年12

2022-02-17 06:05:39

在單片機(jī)開發(fā)過程中怎樣使用定時器進(jìn)行定時及超時處理呢?

2022-01-21 07:33:27

在嵌入式開發(fā)過程中常用的庫函數(shù)有哪些?有何優(yōu)勢?

2022-02-25 07:07:18

目標(biāo)? 博文旨在總結(jié)自己在嵌入式linux開發(fā)過程中遇到的坑?、一些小知識點的匯總。?等哪天發(fā)展到遠(yuǎn)離代碼了,還能回一下當(dāng)年的英姿。

2021-11-05 09:06:58

OSEK/VDX標(biāo)準(zhǔn)包括哪幾個部分?OSEK/VDX任務(wù)管理的三種狀態(tài)分析基于OSEK規(guī)范的應(yīng)用開發(fā)過程是怎樣的?

2021-05-13 06:55:08

本文主要是記錄基于STM32WB55的核心板設(shè)計開發(fā)過程中遇到的關(guān)鍵問題及解決方案。1、硬件設(shè)計目前PCB已打板回來焊接完成。后續(xù)需要優(yōu)化的地方有如下所示:1、LSM6DSLTR傳感器的封裝

2021-08-11 08:27:57

大家好,我想知道如何實現(xiàn)硬件(FPGA)中的時序報告給出的時序。我的意思是,如何測量FPGA和FPGA中輸入信號的建立或保持時間與靜態(tài)時間報告給出的值進(jìn)行比較。FPGA怪胎以上來自于谷歌翻譯以下

2019-01-15 11:07:15

FPGA的最初布局和布線完成后,時序報告提供數(shù)據(jù)總線中每個時序的詳細(xì)延時信息。如果有必要,可為FPGA開發(fā)系統(tǒng)的關(guān)鍵信號設(shè)定延時路徑,TimingDesigner可以提取相關(guān)信息和利用圖表更新。在這

2009-04-14 17:03:52

本文針對FPGA實際開發(fā)過程中,出現(xiàn)故障后定位困難、上板后故障解決無法確認(rèn)的問題,提出了一種采用仿真的方法來定位、解決故障并驗證故障解決方案。

2021-05-06 07:18:15

嵌入式開發(fā)過程中,遇到scp Permission denied,將目標(biāo)文件chmod 777也不起作用,其實需要修改ssh的配置。如下:sudo vim /etc/ssh/ssh_config將其中的PasswordAuthentication 的值給為yes即可。...

2021-11-08 09:17:58

前言本篇主要是對嵌入式開發(fā)過程中遇到的一些很小的知識點進(jìn)行記錄,就像閱讀一篇英語文章,碰見一些不認(rèn)識的,不熟悉的單詞,語法,查閱資料搞懂記錄下來,這些零碎的東西聚少成多,也是一筆客觀的知識財富。以后

2021-12-14 07:37:13

嵌入式linux開發(fā)過程中逗比的硬件問題

2021-12-21 06:47:52

嵌入式產(chǎn)品與普通電子產(chǎn)品一樣,在開發(fā)過程中需要遵循一些基本過程,即從需求分析到總體設(shè)計,詳細(xì)設(shè)計到最終產(chǎn)品完成的過程它包括兩個部分:嵌入式軟件和嵌入式硬件。針對嵌入式硬件和軟件的開發(fā),不需要參與普通

2021-12-17 08:18:13

對很多人來,嵌入式軟件開發(fā)過程中模塊化(Modularization)是一個海市蜃樓、是一個書面詞匯、是一個過氣的時尚——模塊化似乎從未真正的實現(xiàn)過。吹牛時人們常不屑的說:沒吃...

2021-12-20 07:22:06

職位概述:1、從事視頻圖像處理的研究與開發(fā)2、設(shè)計各種驅(qū)動芯片的時序邏輯職位要求:1、負(fù)責(zé)FPGA軟件代碼編寫、模塊設(shè)計及仿真2、負(fù)責(zé)FPGA調(diào)試,資源優(yōu)化與時序優(yōu)化3、負(fù)責(zé)編寫開發(fā)過程中的各種技術(shù)

2016-05-11 15:15:41

求大神詳細(xì)介紹一下FPGA嵌入式系統(tǒng)開發(fā)過程中的XBD文件設(shè)計

2021-05-06 08:19:58

設(shè)計源文件和設(shè)計過程。源文件只能從當(dāng)前位置訪問,在設(shè)計實現(xiàn)過程中的每一步,數(shù)據(jù)和運行結(jié)果都存在于 Vivado 分配到的機(jī)器內(nèi)存中,在用戶不主動輸 出的情況下,不會存儲到硬盤中。

簡單來講,非工程

2023-06-28 19:34:58

ATtiny13指令執(zhí)行過程中的訪問時序?

2020-11-10 07:09:28

ATtiny2313指令執(zhí)行過程中如何訪問時序

2020-11-11 07:31:09

請問atmel32單片機(jī)開發(fā)過程中常見的問題有哪些?

2021-09-18 06:43:13

ATmega168指令執(zhí)行過程中的訪問時序

2020-11-09 06:36:55

程序開發(fā)過程中如何確認(rèn)寄存器的值是否正確?

2020-11-24 06:53:17

單片機(jī)開發(fā)過程中,有一個好的調(diào)試系統(tǒng)可以極大地提高開發(fā)效率。舉個例子,做平衡系統(tǒng)時調(diào)節(jié)PID參數(shù),你會選擇 修改參數(shù)–>編譯–>燒錄–>運行–>修改…,還是做一個功能可以一邊

2022-01-14 08:25:36

軟件,完成設(shè)計規(guī)定的性能要求。在布局布線過程中,可同時提取時序信息形成報靠。(4)時序提取:產(chǎn)生一反標(biāo)文件,供給后續(xù)的時序仿真使用。(5)配置:產(chǎn)生FPGA配置時的需要的位流文件。在實現(xiàn)過程中可以進(jìn)行

2021-06-24 08:00:01

針對客戶在STM32L011D4P6應(yīng)用開發(fā)過程中,碰到的啟動模式問題進(jìn)行了分析。并且根據(jù)問題,介紹開發(fā)工具、燒錄工具中如何配置以避免影響。一 問題描述發(fā)現(xiàn)盡管已經(jīng)為Boot0引腳提供了低電平,在

2016-08-30 16:22:14

在項目的開發(fā)過程中,項目鴻蒙中的項目名稱顯示給我們的項目計劃類,用英文表示,然后開始我們的虛擬機(jī)會發(fā)現(xiàn)界面頂部顯示為英文,如下圖:

2022-04-28 11:48:53

提出考慮資源約束的產(chǎn)品開發(fā)過程仿真模型。該模型考慮產(chǎn)品開發(fā)過程中的返工迭代以及資源約束,根據(jù)任務(wù)信息控制能力確定任務(wù)資源分配的優(yōu)先級,相對于Cooper 提出的資源分

2009-04-16 11:36:30 16

16 就目前中小型客車生產(chǎn)企業(yè)在產(chǎn)品設(shè)計、開發(fā)過程中存在的問題, 提出抓產(chǎn)品質(zhì)量應(yīng)從產(chǎn)品的設(shè)計與開發(fā)這個源頭抓起; 產(chǎn)品設(shè)計過程的基礎(chǔ)是質(zhì)量控制。關(guān)鍵詞: 客車產(chǎn)品 設(shè)計

2009-07-25 16:34:39 27

27 本文通過對目標(biāo)機(jī)硬件環(huán)境初始化過程和硬件驅(qū)動開發(fā)過程的描述,詳細(xì)介紹了基于PPC8270的BSP開發(fā)過程。在該開發(fā)實例中,該BSP軟件能夠在目標(biāo)機(jī)模塊上穩(wěn)定運行,并為上層操作系統(tǒng)及

2011-07-23 10:32:39 2574

2574

本內(nèi)容詳細(xì)介紹了基于DSPs的系統(tǒng)開發(fā)過程

2011-09-29 17:28:18 136

136 本文結(jié)合作者在單片機(jī)開發(fā)過程中體會,討論硬件調(diào)試的技巧。當(dāng)硬件設(shè)計從布線到焊接安裝完成之后,就開始進(jìn)入硬件調(diào)試階段

2012-06-01 16:09:55 13601

13601 我這個題目想說明的是,FPGA的內(nèi)部的有其相應(yīng)的Fabric,如何在開發(fā)過程中最好最大限度的使用它。

2017-02-11 12:53:11 1158

1158 嵌入式軟件開發(fā)過程中基于功能點的缺陷度量_李冰

2017-03-14 08:00:00 0

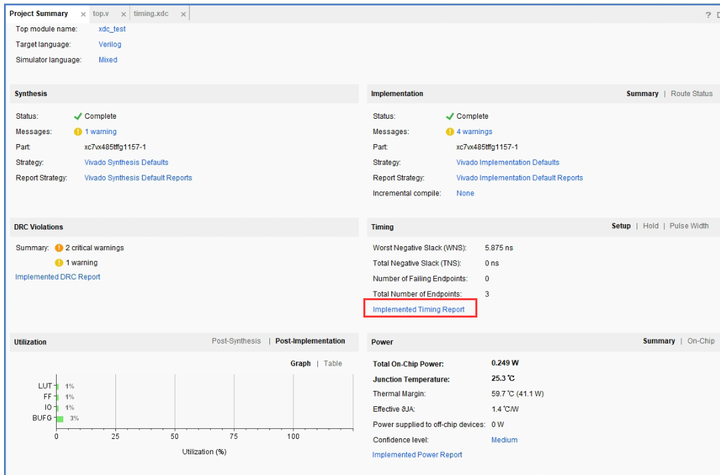

0 過程必須以滿足XDC中的約束為目標(biāo)來進(jìn)行。那么: 如何驗證實現(xiàn)后的設(shè)計有沒有滿足時序要求? 如何在開始布局布線前判斷某些約束有沒有成功設(shè)置? 如何驗證約束的優(yōu)先級? 這些都需要用到Vivado中的靜態(tài)時序分析工具。

2017-11-17 18:03:55 34003

34003

Unity開發(fā)了一個多平臺API和實用程序,幫助解決你在AR開發(fā)過程中遇到的眾多難題,他們將其稱之為 AR Foundation。

2018-09-11 09:51:00 5198

5198 在軟件項目開發(fā)過程中,應(yīng)該按軟件開發(fā)要求撰寫十三類文檔,文檔編制要求具有針對性、精確性、清晰性、完整性、靈活性、可追溯性!

2018-09-15 09:03:00 5801

5801 時序分析在FPGA設(shè)計中是分析工程很重要的手段,時序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習(xí)Vivado軟件時序分析的筆記,小編這里使用的是18.1版本的Vivado。 這次

2019-09-15 16:38:00 5787

5787

了解report_design_analysis,這是一個新的Vivado報告命令,可以獨特地了解時序和復(fù)雜性特征,這些特性對于分析時序收斂問題很有價值。

2018-11-26 07:01:00 3314

3314 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:08:00 2539

2539

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:06:00 2166

2166

小技巧進(jìn)行歸納。 清理/壓縮工程 實際使用vivado的過程中,由于vivado會自動產(chǎn)生一系列文件,有些是不

2020-12-25 14:53:36 8000

8000

VIVADO中時序報告中WNS,WHS,TNS,THS含義運行“report_timing”或“report_timing_summary”命令后,會注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

嵌入式開發(fā)過程中的一點調(diào)試經(jīng)驗嵌入式開發(fā)最麻煩的在現(xiàn)場調(diào)試過程中或?qū)嶋H運營過程中出現(xiàn)問題很難定位。我在實際開發(fā)過程中一點經(jīng)驗分享給大家嵌入式開發(fā)調(diào)試分為開發(fā)階段調(diào)試,現(xiàn)場調(diào)試,運行調(diào)試以STM32

2021-11-02 18:06:03 15

15 **.**單片機(jī)開發(fā)過程中按鍵處理函數(shù)的實現(xiàn)? **.**方法一? 這種方法在單片機(jī)處理中反應(yīng)不夠好,當(dāng)按鍵交替按時,會表現(xiàn)的不夠好?void Key_Scan(void

2021-11-13 12:36:02 16

16 基于Energia的MPS430單片機(jī)開發(fā)過程中的問題

2021-11-19 17:21:02 9

9 對 FPGA 設(shè)計的實現(xiàn)過程必須以滿足 XDC 中的約束為目標(biāo)進(jìn)行。那我們?nèi)绾悟炞C實現(xiàn)后的設(shè)計有沒有滿足時序要求?又如何在開始布局布線前判斷某些約束有沒有成功設(shè)置?或是驗證約束的優(yōu)先級?這些都要用到 Vivado 中的靜態(tài)時序分析工具。

2023-05-04 11:20:31 2368

2368

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會提供時序報告,以方便開發(fā)者判斷自己的工程時序是否滿足時序要求。

2023-06-23 17:44:00 531

531

STA(Static Timing Analysis,即靜態(tài)時序分析)在實際FPGA設(shè)計過程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設(shè)定的時鐘周期內(nèi)完成,更詳細(xì)一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 344

344

FPGA開發(fā)過程中軟件的綜合布線耗時很長,這塊對FPGA產(chǎn)品開發(fā)的進(jìn)度影響很大。

2023-06-26 14:58:09 367

367

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向?qū)В–onstraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

在單片機(jī)項目開發(fā)過程中,經(jīng)常會出現(xiàn)一個有趣的問題,即弄清楚如何延遲代碼執(zhí)行。有時,[單片機(jī)開發(fā)]人員可能只是希望有10微秒的延遲,以使I/O線在讀取之前穩(wěn)定下來,或者可能希望在兩次讀取之間指定的時間間隔使它反跳。在本文中,我們將探討五種延遲代碼執(zhí)行的技術(shù)。

2023-07-10 10:43:17 989

989 電子發(fā)燒友網(wǎng)站提供《Android校園應(yīng)用開發(fā)過程.pdf》資料免費下載

2023-10-19 11:36:21 0

0 電子發(fā)燒友網(wǎng)站提供《ASIC芯片開發(fā)過程.ppt》資料免費下載

2023-12-25 10:04:49 1

1 有些時候在寫完代碼之后呢,Vivado時序報紅,Timing一欄有很多時序問題。

2024-01-05 10:18:36 291

291

電子發(fā)燒友App

電子發(fā)燒友App

評論