FPGA開發過程中,vivado和quartus等開發軟件都會提供時序報告,以方便開發者判斷自己的工程時序是否滿足時序要求。

本文將詳細介紹如何讀懂Vivado時序報告,包括報告的基本結構和如何分析報告。

一、新建工程

使用vivado創建一個新的工程,添加verilog代碼文件,內容如下:

module xdc_test

(

input wire clk,

input wire reset,

output reg [3:0] data_cnt

);

always @(posedge clk or posedge reset)begin

if(reset)

data_cnt <= 'b0;

else

data_cnt <= data_cnt + 1'b1;

end

endmodule

創建xdc文件,并添加時序約束:

create_clock -period 6.6667 -name clk -waveform {0.000 5.000} [get_ports clk]

如果需要了解時序約束如何添加,可以看下上一篇文章《FPGA時序約束--實戰篇(Vivado添加時序約束)》

點擊“generate bitestream”,開始綜合、布線和生成bit文件。

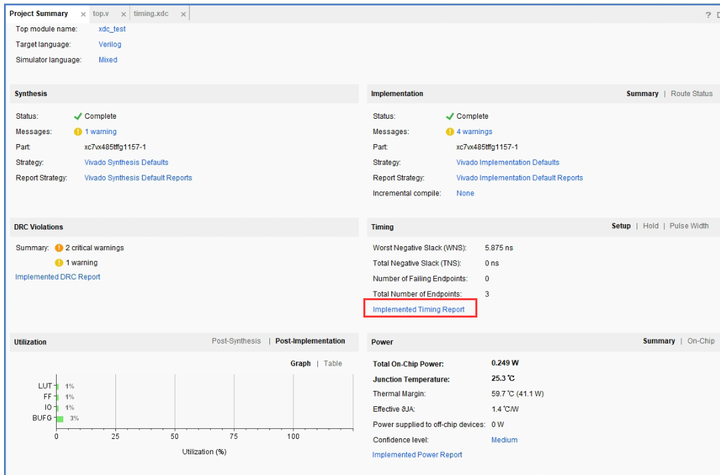

綜合完成后,可以在“Design run”界面,看到整個工程時序滿足情況,主要資源消耗、編譯時間等等信息,如下圖。

二、時序報告分析

1、打開時序報告界面

(1)方法1

點擊“實現implementation”下的“report timing summary”選項。

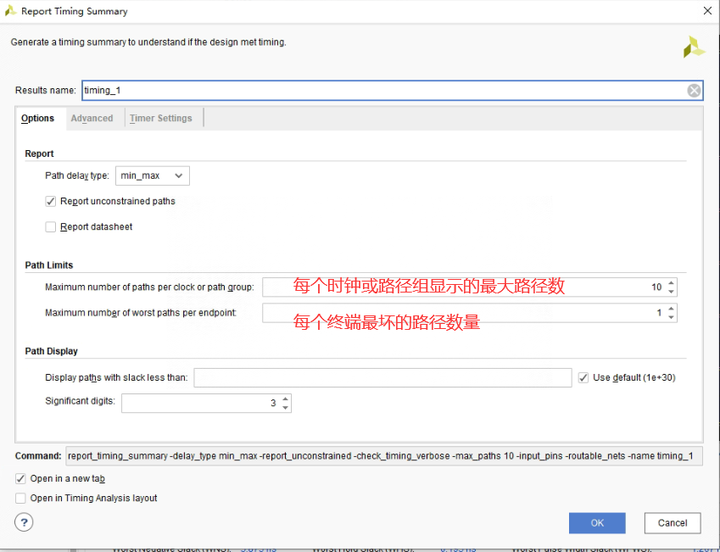

彈出時序顯示設置界面,如下圖所示,點擊OK。

(2)方法2

點擊功能欄“∑”,在“Timing”界面下,點擊“Implementation Timing Report”。

2、時序報告界面介紹

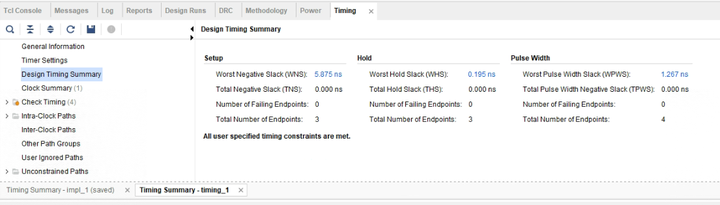

Timing界面左側是時序信息總覽、時鐘和時序路徑分類,右側是時序信息總覽詳細信息,包括Setup、Hold以及Pulse Width檢查最差的各10條路徑。

這里有幾個重要的參數信息名稱:

WNS (Worst Negative Slack) :最差負時序裕量

TNS(Total Negative Slack) :總的負時序裕量 ,也就是負時序裕量路徑之和。WHS (Worst Hold Slack) :最差保持時序裕量

THS (Total Hold Slack) :總的保持時序裕量,也就是負保持時序裕量路徑之和。

這些參數如果為負或者顏色變為紅色,則表示出現了時序違例,否則表示時序正常。

3、時序路徑分析

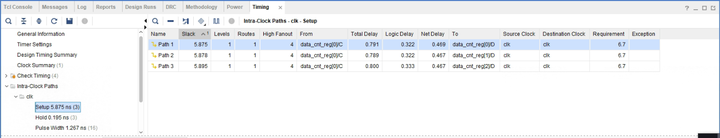

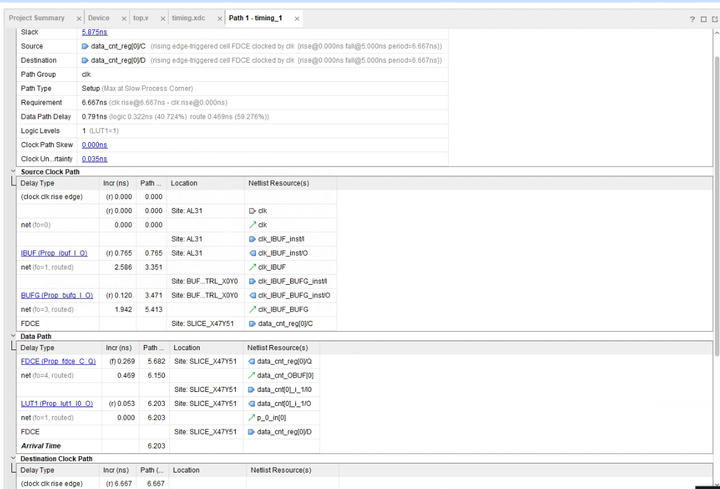

點擊時序報告界面中WNS的數值,如上面報告中的“5.875ns”,則會直接跳轉到時序最差路徑的界面。

主要參數信息含義如下:

slack:時間裕量

level:邏輯級數,表示兩個寄存器之間存在的組合邏輯層數

fanout:扇出數,表示一個信號驅動的所有接收端的數量

from:路徑起始位置,包含HDL代碼中的起始寄存器

to:路徑結束位置,包含HDL代碼中的起始寄存器的下一級寄存器

Total Delay:整個路徑的總體延時

Logic Delay:整個路徑的邏輯延時

Source Clock:路徑起始寄存器的時鐘

Destination Clock:路徑終點寄存器的時鐘

Requirement:時鐘周期,即路徑延時最大值

如果slack出現紅色值,且為負值,則表示出現了時序違例。

另外通過看level和fanout,可以看到路徑時序違例的原因,level值過大,則表示邏輯層數太多,需要考慮將這條路徑對應HDL代碼分成幾拍完成;如果fanout值過大,則表示該寄存器的扇出過大。

雙擊任意一條時序路徑,以“path1”為例,即可進入該路徑的時序具體信息,主要包括summary(總覽)、Source Clock Path(源時鐘路徑)、Data Path(數據路徑)、Destination Clock Path(目的時鐘路徑)。

這里可以查看到具體的時序布線情況,以及時序違例的原因。

三、總結

時序報告是Vivado中必不可少的工具,它可以幫助我們了解電路的時序性能,并找出潛在的時序問題。通過分析時序報告,我們可以確定關鍵路徑延遲、slack和每個信號路徑的延遲等信息,并找到需要優化和調整的地方。如果存在時序問題,我們可以通過修改代碼、時序約束或重新布局/重分配電路來進行優化。

-

FPGA

+關注

關注

1644文章

21989瀏覽量

615222 -

寄存器

+關注

關注

31文章

5426瀏覽量

123682 -

時序

+關注

關注

5文章

397瀏覽量

37826 -

Vivado

+關注

關注

19文章

833瀏覽量

68363

發布評論請先 登錄

VIVADO時序約束及STA基礎

一文詳解Vivado時序約束

vivado:時序分析與約束優化

Vivado下顯示指定路徑時序報告的流程

關于Vivado時序分析介紹以及應用

新Vivado報告命令的了解

Vivado時序案例分析之解脈沖寬度違例

VIVADO中時序報告中WNS、WHS、TNS、THS有什么含義

Vivado使用進階:讀懂用好Timing Report

如何讀懂FPGA開發過程中的Vivado時序報告?

Vivado使用小技巧

如何讀懂Vivado時序報告

如何讀懂Vivado時序報告

評論