每當您需要在PCB布局中放置參考電壓時,它都必須對溫度波動和外部噪聲具有超穩定性。基準電壓源的漂移會產生較小的電壓誤差,這在某些精密測量系統以及精密穩壓器和高分辨率轉換器中是無法接受的。參考電壓電路有一個特定的量,該量定義了溫度循環如何影響參考電壓,這就是所謂的熱滯。

對于半導體部件,僅由于半導體器件的平面結構,不可避免地存在熱滯后現象。盡管不能完全防止熱滯現象,但是可以通過在將產品部署到最終環境之前進行適當的PCB安裝和電氣測試來抑制它。這是導致熱滯現象的原因,以及在準備部署新解決方案時如何消除熱滯現象。

什么是熱滯回?

從技術上講,由于某些變量或系統參數(包括溫度和隨溫度變化的量)的變化,任何可物理測量的量在測量過程中都會顯示出滯后現象。通常用含防凍蛋白/糖蛋白的溶液中冰晶的凝固點和熔點的分離來討論熱滯,其中隨著溶液溫度在極限值之間循環,凝固溫度和熔化溫度將略有變化。從概念上講,可以將熱磁滯與磁滯進行比較,其中循環的磁場會留下一些剩余磁化強度。

電路中的熱滯回

在電子產品中,熱滯現象用于描述參考電壓的精度。這些是精密電路和設備,用于為某些其他電路中的電壓測量提供穩定的比較。需要穩定參考電壓的一些電路和組件是:

模數轉換器(ADC)和數模轉換器(DAC):這兩個電路使用參考電壓來設置量化值。

低壓差(LDO)調節器:基準電壓用作誤差放大器的一個輸入,以檢測調節器的輸出電壓何時下降得太低。然后,誤差放大器對MOSFET進行調制,以將輸出電壓校正為所需值。

比較器:基準電壓源為比較器的高和低閾值及其自身的開關滯后提供了基礎。這可以由電池,齊納二極管或硅帶隙基準源提供。

正式定義

熱滯現象的形式正式定義為在整個工作溫度范圍內器件循環之前和之后,環境溫度(+25°C)下輸出電壓的變化。電壓基準電路中的熱滯通常以ppm /°C為單位進行測量。這是輸出參考電壓由于在間隔ΔT內的溫度循環而變化的量。實際上,當溫度在整個ΔT內循環時,這是參考電壓電路輸出電壓的永久變化。

如果器件在其低溫額定值和高溫額定值之間循環(例如,許多組件的溫度范圍為-40°C至125°C),則對于典型的帶隙基準電壓電路,輸出的總變化可達到?1 mV。正確安裝在PCB上的高精度電路在整個工作溫度范圍內的遲滯值可低至?105 ppm。注意,即使電路的溫度保持恒定,在這些電路中也會發生長期漂移。

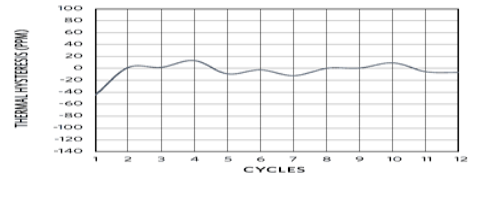

LDO穩壓器中使用的參考電壓中的熱滯示例測量。

什么引起熱滯后?

熱滯是由溫度循環過程中累積在半導體管芯上的機械應力產生的。應力分布以及如何從器件釋放應力取決于芯片先前是否處于較高或較低的溫度,以及器件中過去的應力歷史。由于熱膨脹和收縮,應力在模具上的不同位置累積并凝固。

一旦帶有參考電壓電路的設備脫離生產線,通常會在標準環境條件下進行簡短測試。接下來發生的事情可能會在半導體管芯上施加壓力,并導致參考電壓電路的輸出以下列方式發生變化:

包裝過程中的加熱和冷卻:將模具放置在包裝中時,將其裝入高溫的環氧包裝中。然后包裝冷卻并返回到環境溫度。在此過程中,應力將積聚在模具上。

組裝過程中的焊接:波峰焊需要將設備加熱到高溫并保持一段時間。冷卻后,模具中會積累一些應力。手工焊接不會將整個設備加熱到導致大量應力累積的程度。

工作期間發熱:當設備在PCB上工作時,溫度不可避免發生變化。熱量可能從板上的其他組件或外部環境流向參考電壓電路。

在容易產生熱滯的部件周圍放置切口槽是增加部件下方的基板的剛度的一種方法。另外,將設備放置在遠離PCB中心的位置。兩種方法均已通過實驗證明可減少應力積累和產生的熱滯后現象。

板邊緣提供了一個較硬的安裝表面,可防止由于熱滯而導致輸出電壓變化。

最后,為了減輕管芯中的應力并迫使參考電壓電路穩定到其長期輸出,可以在組裝的PCB運行時重復循環該電路。這可能需要多個周期,但是一些組件制造商對參考電壓的測量顯示,在重復循環之后,磁滯窗口會隨著時間的流逝而減小。

編輯:hfy

-

pcb

+關注

關注

4359文章

23448瀏覽量

407846

發布評論請先 登錄

如何通過最小化熱回路PCB ESR和ESL來優化開關電源布局

一種卡類終端的PCB熱設計方法

測量PCB或環境溫度,請問如何對PCB進行布局?

解決PCB設計消除串擾的辦法

PCB設計中熱設計的規劃

PCB熱設計概述

PCB布局如何設計檢視要素(布局DFM/熱設計/信號完整性/EMC/電源模塊的要求)

使用集成的原理圖、布局和仿真工具消除DDR設計中的猜測

PCB布局中如何消除熱滯現象

PCB布局中如何消除熱滯現象

評論