1、AC耦合電容的作用

source和sink端DC level不同,用來(lái)隔直流;

信號(hào)傳輸時(shí)可能會(huì)串?dāng)_進(jìn)去直流分量,所以隔直流使信號(hào)眼圖更好。

2、AC耦合電容的位置及大小

一般AC耦合電容的位置和容值大小都是由信號(hào)的協(xié)議或者芯片供應(yīng)商去提供,對(duì)于不同信號(hào)和不同芯片,其位置和容值大小都是不一樣的。比如PCIE信號(hào)要求AC耦合電容靠近通道的發(fā)送端,SATA信號(hào)要求AC耦合電容靠近連接器處,對(duì)于10GBASE-KR信號(hào)要求AC耦合電容靠近信號(hào)通道的接收端。

一般放在接收端,其原因如下:

電容看成一個(gè)阻抗不連續(xù)點(diǎn)(所以要求盡量跟傳輸線匹配),如果靠近接收端放,相同的反射系數(shù)下,信號(hào)經(jīng)過(guò)通道衰減之后再反射會(huì)比一開(kāi)始就反射的能量小。所以大多數(shù)的串行鏈路都要求靠接收端放。

在信號(hào)傳輸過(guò)程中,也可能串?dāng)_進(jìn)去一些直流分量,導(dǎo)致接收出問(wèn)題,所以靠近接收端。

在設(shè)計(jì)過(guò)程中,最好的處理方式如下:

優(yōu)先按照design guideline要求放置;

如果沒(méi)有g(shù)uideline,如果是IC到IC,靠近接收端放置;

如果是IC到連接器,靠近連接器放置;

盡可能選擇小的封裝尺寸,減小阻抗不連續(xù);耦合電容的大小,一般0.1uF可以滿足到10G的應(yīng)用,具體的接口要求不一樣。

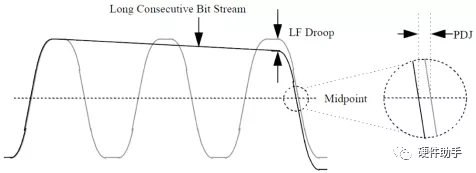

在串行信號(hào)中串入AC耦合電容,這個(gè)電容可以提供直流偏壓和過(guò)電流保護(hù),但也會(huì)給鏈路帶來(lái)另一個(gè)問(wèn)題PDJ(pattern-dependent jitter)。這和碼型有關(guān),鏈路可以等效成高通RC電路,當(dāng)出現(xiàn)連續(xù)的“1”或“0”時(shí),會(huì)出現(xiàn)下圖的直流壓降,這不僅會(huì)影響眼高,還會(huì)造成PDJ。

怎樣才能減小這個(gè)直流壓降呢?這和RC時(shí)間常數(shù)有關(guān),RC值越大,能通過(guò)的直流分量就越多,直流壓降越小。由于鏈路中等效R是相對(duì)固定的,只能調(diào)節(jié)耦合電容值了。一般情況耦合電容值越大,壓降越小。

因?yàn)椋瑢?shí)際安裝后的電容不是理想電容,除了ESR、ESL,還有安裝電感,所以就存在一個(gè)串聯(lián)諧振頻率。電容在此頻率之前呈容性,之后呈感性。電容值越大,諧振頻率越小,電容在較低頻率就會(huì)呈現(xiàn)感性,這樣會(huì)造成信號(hào)高頻分量衰減增大,同樣會(huì)使眼高減小,上升沿變緩,jitter增加。

所以選值時(shí)要綜合以上兩點(diǎn)考量,一般業(yè)界都推薦0.01uF~0.2uF,最常見(jiàn)的就是0.1uF的電容。封裝的選擇不建議使用大于0603的封裝,最好是0402的。

交流耦合電容的計(jì)算公式為:

C=7.8*NCID*Tb/R

其中:

Tb = the bit period(時(shí)鐘周期)

NCID = the maximum tolerated consecutive identical digits(連續(xù)同一電平的長(zhǎng)度)

R = the total resistance asseen from the capacitor(RC電路中的R)

例如在光通信系統(tǒng)中,典型的貸款為0.6~1倍數(shù)據(jù)速率。比如2.488Gbps的接收器Tb=402ps。如果NCID=72bits,R=100,計(jì)算出來(lái)的C=2.25nF。如果Tr=120ps,并且C=2.25nF,那么計(jì)算粗來(lái)的PDJ=12ps。如果將C增大到100nF,則PDJ會(huì)減小到<1ps。

一般而言,電容容量越大,ESL也會(huì)比較大,所以選擇電容時(shí)需要綜合考慮。詳細(xì)的選擇可以參考MAXIM Application Note HFAN-1.1:Choosing AC-Coupling Capacitors。

3、AC耦合電容的應(yīng)用

SATA信號(hào)傳輸?shù)倪^(guò)程中會(huì)有衰減,傳的距離越長(zhǎng)衰減會(huì)越厲害,所以會(huì)給他一個(gè)載波(也就是直流分量),在進(jìn)入IC或SATA device后再用串電容的方法把直流分量濾掉,這樣做會(huì)有比較好的信號(hào)質(zhì)量。也就是隔直作用。

PCIe板卡放在發(fā)送端是協(xié)議規(guī)定的(可參看后續(xù)PCIe相關(guān)文章,會(huì)詳細(xì)講解針對(duì)PCIe總線的耦合電容的位置、大小、數(shù)量等等)。

USB3.0上TX、RX要加,D+、D-不加,因?yàn)橐嫒?.0/1.1/1.0,跟2.0和1.1的檢測(cè)有關(guān)。

4、AC耦合電容的PCB設(shè)計(jì)

每個(gè)電容本身,電容的扇出引線和電容換層過(guò)孔都是一個(gè)阻抗不連續(xù)點(diǎn)。高速串行信號(hào)對(duì)于阻抗一致性提出非常高的要求,如果阻抗匹配不好將會(huì)帶來(lái)反射,最后影響整個(gè)通道的IL、RL、Jitter以及BER等,最終影響整個(gè)通道性能。

4.1、布局

差分信號(hào)在設(shè)計(jì)時(shí)候需要盡量做到對(duì)稱,任何不對(duì)稱的因素都會(huì)使得部分差分信號(hào)轉(zhuǎn)換為共模信號(hào)。對(duì)于共模信號(hào)而言,信號(hào)和參考面的耦合和回流路徑一旦處理不好,都會(huì)成為EMI的潛在威脅。

不對(duì)稱的電容擺放會(huì)帶來(lái)更多的共模信號(hào),將對(duì)EMI帶來(lái)潛在的威脅,而不對(duì)稱擺放對(duì)插損回?fù)p影響不大。

4.2、布線

對(duì)于0.1uF的0402封裝(焊盤尺寸為20mil*20mil)的耦合電容,以一個(gè)六層板為例(疊層順序?yàn)門OP-GND1-SIG1-SIG2-GND2-BOT),電容布局在TOP層,如以GND1層為參考,則焊盤處的阻抗為92Ω左右(實(shí)際差分阻抗要求是100Ω)。由于電容pad處的寬度為20mil,大于走線寬度,而阻抗和線寬成反比,因此pad處阻抗會(huì)變小。為了增大pad處的阻抗,可以使pad和參考面的距離增大。可以把pad正下方的GND1層掏空,電容pad就參考了SIG1層的電源/地平面(在對(duì)應(yīng)位置鋪銅,并通過(guò)sitching vias連接),這樣阻抗就會(huì)變大。

為了得到更精確的設(shè)計(jì)參數(shù),可以利用3D電磁場(chǎng)仿真軟件進(jìn)行仿真,不同挖空形狀對(duì)阻抗的影響還是比較大的,一般粗略的設(shè)計(jì),挖空的形狀為和電容長(zhǎng)度相等,和兩個(gè)電容并排的寬度稍微寬一點(diǎn)的矩形即可。這樣的設(shè)計(jì)會(huì)讓通道的阻抗一致性最好。阻抗通道的一致性越好,其反射會(huì)越小,從而帶來(lái)了插損和回?fù)p曲線的改善,最終會(huì)使整個(gè)系統(tǒng)工作更穩(wěn)定。

以上就是針對(duì)交流耦合電容的粗略理解,后續(xù)會(huì)以PCIe總線為例,針對(duì)PCIe總線的AC耦合電容進(jìn)行進(jìn)一步的介紹。

編輯:hfy

-

AC

+關(guān)注

關(guān)注

1文章

590瀏覽量

85068 -

邏輯電平

+關(guān)注

關(guān)注

0文章

184瀏覽量

14712 -

耦合電容

+關(guān)注

關(guān)注

2文章

155瀏覽量

20230

發(fā)布評(píng)論請(qǐng)先 登錄

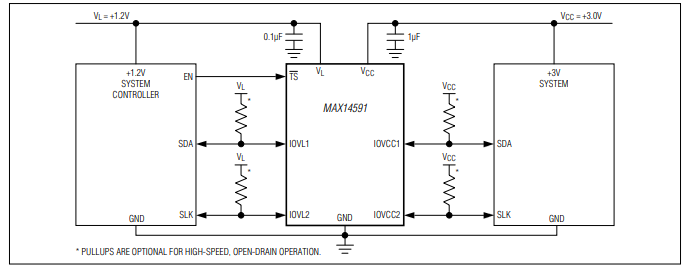

MAX14591高速、漏極開(kāi)路邏輯電平轉(zhuǎn)換器技術(shù)手冊(cè)

邏輯電平之AC耦合電容的應(yīng)用

邏輯電平之AC耦合電容的應(yīng)用

評(píng)論