本文設計思想采用明德揚至簡設計法。上一篇博文中定制了自定義MAC IP的結構,在用戶側需要位寬轉換及數據緩存。本文以TX方向為例,設計并驗證發送緩存模塊。這里定義該模塊可緩存4個最大長度數據包,用戶根據需求改動即可。

該模塊核心是利用異步FIFO進行跨時鐘域處理,位寬轉換由VerilogHDL實現。需要注意的是用戶數據包位寬32bit,因此包尾可能有無效字節,而轉換為8bit位寬數據幀后是要丟棄無效字節的。內部邏輯非常簡單,直接上代碼:

`timescale 1ns / 1ps

// Description: MAC IP TX方向用戶數據緩存及位寬轉換模塊

// 整體功能:將TX方向用戶32bit位寬的數據包轉換成8bit位寬數據包

//用戶側時鐘100MHZ,MAC側125MHZ

//緩存深度:保證能緩存4個最長數據包,TX方向用戶數據包包括

//目的MAC地址 源MAC地址 類型/長度 數據 最長1514byte

module tx_buffer#(parameter DATA_W = 32)//位寬不能改動

(

//全局信號

input rst_n,//保證拉低三個時鐘周期,否則FIF可能不會正確復位

//用戶側信號

input user_clk,

input [DATA_W-1:0] din,

input din_vld,

input din_sop,

input din_eop,

input [2-1:0] din_mod,

output rdy,

//MAC側信號

input eth_tx_clk,

output reg [8-1:0] dout,

output reg dout_sop,

output reg dout_eop,

output reg dout_vld

);

reg wr_en = 0;

reg [DATA_W+4-1:0] fifo_din = 0;

reg [ (2-1):0] rd_cnt = 0 ;

wire add_rd_cnt ;

wire end_rd_cnt ;

wire rd_en;

wire [DATA_W+4-1:0] fifo_dout;

wire rst;

reg [ (2-1):0] rst_cnt =0 ;

wire add_rst_cnt ;

wire end_rst_cnt ;

reg rst_flag = 0;

wire [11 : 0] wr_data_count;

wire empty;

wire full;

/****************************************寫側*************************************************/

always @(posedge user_clk or negedge rst_n)begin

if(rst_n==1'b0)begin

wr_en end

else if(rdy)

wr_en end

always @(posedge user_clk or negedge rst_n)begin

if(rst_n==1'b0)begin

fifo_din end

else begin//[35] din_sop [34] din_eop [33:32] din_mod [31:0] din

fifo_din end

end

assign rdy = wr_data_count

/****************************************讀側*************************************************/

always @(posedge eth_tx_clk or negedge rst_n) begin

if (rst_n==0) begin

rd_cnt end

else if(add_rd_cnt) begin

if(end_rd_cnt)

rd_cnt else

rd_cnt end

end

assign add_rd_cnt = (!empty);

assign end_rd_cnt = add_rd_cnt && rd_cnt == (4)-1 ;

assign rd_en = end_rd_cnt;

always @(posedge eth_tx_clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout end

else if(add_rd_cnt)begin

dout end

end

always @(posedge eth_tx_clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout_vld end

else if(add_rd_cnt && ((rd_cnt dout_vld end

else

dout_vld end

always @(posedge eth_tx_clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout_sop end

else if(add_rd_cnt && rd_cnt == 0 && fifo_dout[35])begin

dout_sop end

else

dout_sop end

always @(posedge eth_tx_clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout_eop end

else if(add_rd_cnt && rd_cnt == 3 - fifo_dout[33:32] && fifo_dout[34])begin

dout_eop end

else

dout_eop end

/******************************FIFO復位邏輯****************************************/

assign rst = !rst_n || rst_flag;

always @(posedge user_clk or negedge rst_n)begin

if(!rst_n)begin

rst_flag end

else if(end_rst_cnt)

rst_flag end

always @(posedge user_clk or negedge rst_n) begin

if (rst_n==0) begin

rst_cnt end

else if(add_rst_cnt) begin

if(end_rst_cnt)

rst_cnt else

rst_cnt end

end

assign add_rst_cnt = (rst_flag);

assign end_rst_cnt = add_rst_cnt && rst_cnt == (3)-1 ;

//FIFO位寬32bit 一幀數據最長1514byte,即379個16bit數據

//FIFO深度:379*4 = 1516 需要2048

//異步FIFO例化

fifo_generator_0 fifo (

.rst(rst), // input wire rst

.wr_clk(user_clk), // input wire wr_clk 100MHZ

.rd_clk(eth_tx_clk), // input wire rd_clk 125MHZ

.din(fifo_din), // input wire [33 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(fifo_dout), // output wire [33 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.wr_data_count(wr_data_count) // output wire [11 : 0] wr_data_count

);

endmodule

tx_buffer

接下來是驗證部分,也就是本文的重點。以下的testbench包含了最基本的測試思想:發送測試激勵給UUT,將UUT輸出與黃金參考值進行比較,通過記分牌輸出比較結果。

`timescale 1ns / 1ps

module tx_buffer_tb( );

parameter USER_CLK_CYC = 10,

ETH_CLK_CYC = 8,

RST_TIM = 3;

parameter SIM_TIM = 10_000;

reg user_clk;

reg rst_n;

reg [32-1:0] din;

reg din_vld,din_sop,din_eop;

reg [2-1:0] din_mod;

wire rdy;

reg eth_tx_clk;

wire [8-1:0] dout;

wire dout_sop,dout_eop,dout_vld;

reg [8-1:0] dout_buf [0:1024-1];

reg [16-1:0] len [0:100-1];

reg [2-1:0] mod [0:100-1];

reg err_flag = 0;

tx_buffer#(.DATA_W(32))//位寬不能改動

dut

(

//全局信號

.rst_n (rst_n) ,//保證拉低三個時鐘周期,否則FIF可能不會正確復位

.user_clk (user_clk) ,

.din (din) ,

.din_vld (din_vld) ,

.din_sop (din_sop) ,

.din_eop (din_eop) ,

.din_mod (din_mod) ,

.rdy (rdy) ,

.eth_tx_clk (eth_tx_clk) ,

.dout (dout) ,

.dout_sop (dout_sop) ,

.dout_eop (dout_eop) ,

.dout_vld (dout_vld)

);

/***********************************時鐘******************************************/

initial begin

user_clk = 1;

forever #(USER_CLK_CYC/2) user_clk = ~user_clk;

end

initial begin

eth_tx_clk = 1;

forever #(ETH_CLK_CYC/2) eth_tx_clk = ~eth_tx_clk;

end

/***********************************復位邏輯******************************************/

initial begin

rst_n = 1;

#1;

rst_n = 0;

#(RST_TIM*USER_CLK_CYC);

rst_n = 1;

end

/***********************************輸入激勵******************************************/

integer gen_time = 0;

initial begin

#1;

packet_initial;

#(RST_TIM*USER_CLK_CYC);

packet_gen(20,2);

#(USER_CLK_CYC*10);

packet_gen(30,1);

end

/***********************************輸出緩存與檢測******************************************/

integer j = 0;

integer chk_time = 0;

initial begin

forever begin

@(posedge eth_tx_clk)

if(dout_vld)begin

if(dout_sop)begin

dout_buf[0] = dout;

j = 1;

end

else if(dout_eop)begin

dout_buf[j] = dout;

j = j+1;

packet_check;

end

else begin

dout_buf[j] = dout;

j = j+1;

end

end

end

end

/***********************************score board******************************************/

integer fid;

initial begin

fid = $fopen("test.txt");

$fdisplay(fid," Start testing /n");

#SIM_TIM;

if(err_flag)

$fdisplay(fid,"Check is failed/n");

else

$fdisplay(fid,"Check is successful/n");

$fdisplay(fid," Testing is finished /n");

$fclose(fid);

$stop;

end

/***********************************子任務******************************************/

//包生成子任務

task packet_gen;

input [16-1:0] length;

input [2-1:0] invalid_byte;

integer i;

begin

len[gen_time] = length;

mod[gen_time] = invalid_byte;

for(i = 1;i if(rdy == 1)begin

din_vld = 1;

if(i==1)

din_sop = 1;

else if(i == length)begin

din_eop = 1;

din_mod = invalid_byte;

end

else begin

din_sop = 0;

din_eop = 0;

din_mod = 0;

end

din = i ;

end

else begin

din_sop = din_sop;

din_eop = din_eop;

din_vld = 0;

din_mod = din_mod;

din = din;

i = i - 1;

end

#(USER_CLK_CYC*1);

end

packet_initial;

gen_time = gen_time + 1;

end

endtask

task packet_initial;

begin

din_sop = 0;

din_eop = 0;

din_vld = 0;

din = 0;

din_mod = 0;

end

endtask

//包檢測子任務

task packet_check;

integer k;

integer num,packet_len;

begin

num = 1;

$fdisplay(fid,"%dth:Packet checking.../n",chk_time);

packet_len = 4*len[chk_time]-mod[chk_time];

if(j != packet_len)begin

$fdisplay(fid,"Length of the packet is wrong./n");

err_flag = 1;

disable packet_check;

end

for(k=0;k

if(k%4 == 3)begin

if(dout_buf[k] != num)begin

$fdisplay(fid,"Data of the packet is wrong!/n");

err_flag = 1;

end

num = num+1;

end

else if(dout_buf[k] != 0)begin

$fdisplay(fid,"Data of the packet is wrong,it should be zero!/n");

err_flag = 1;

end

end

chk_time = chk_time + 1;

end

endtask

endmodule

tx_buffer_tb

可見主要是task編寫及文件讀寫操作幫了大忙,如果都用眼睛看波形來驗證設計正確性,真的是要搞到眼瞎。為保證測試完備性,測試包生成task可通過輸入接口產生不同長度和無效字節數的遞增數據包。testbench中每檢測到輸出包尾指示信號eop即調用packet_check task對數值進行檢測。本文的testbench結構較具通用性,可以用來驗證任意對數據包進行處理的邏輯單元。

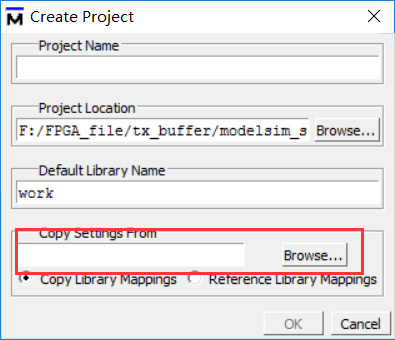

之前Modelsim獨立仿真帶有IP核的Vivado工程時經常報錯,只好使用Vivado自帶的仿真工具。一直很頭痛這個問題,這次終于有了進展!首先按照常規流程使用Vivado調用Modelsim進行行為仿真,啟動后會在工程目錄下產生些有用的文件,幫助我們脫離Vivado進行獨立仿真。

在新建Modelsim工程時,在紅框內選擇Vivado工程中

.sim -> sim_1 -> behav下的modelsim.ini文件。之后添加文件包括:待測試設計文件、testbench以及IP核可綜合文件。第三個文件在

.srcs -> sources_1 -> ip -> -> synth下。

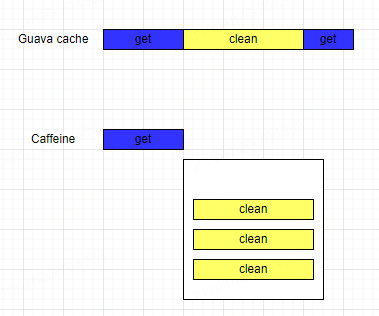

現在可以順利啟動仿真了。我們來看下仿真結果:

文件中信息打印情況:

從波形和打印信息的結果來看,基本可以證明數據緩存及位寬轉換模塊邏輯功能無誤。為充分驗證要進一步給出覆蓋率較高的測試數據集,后期通過編寫do文件批量仿真實現。在FPGA或IC設計中,驗證占據大半開發周期,可見VerilogHDL的非綜合子集也是至關重要的,今后會多總結高效的驗證方法!

編輯:hfy

-

FPGA

+關注

關注

1644文章

22000瀏覽量

615782 -

數據緩存

+關注

關注

0文章

24瀏覽量

7328 -

VerilogHDL

+關注

關注

2文章

39瀏覽量

19384

發布評論請先 登錄

MCU緩存設計

紫光同創FPGA教程:呼吸燈——盤古系列PGX-Nano開發板實驗例程

捕捉光的量子態:單光子信號驗證實驗揭秘

FPGA圖像處理基礎----實現緩存卷積窗口

亞太區首座功率半導體動態可靠度驗證實驗室即將建立

蔚華科技與恩艾共建亞太首座功率半導體驗證實驗室

基于Agilex 5 FPGA的模塊系統介紹

緩存對大數據處理的影響分析

HTTP緩存頭的使用 本地緩存與遠程緩存的區別

緩存技術在軟件開發中的應用

探討移動設備中的緩存文件管理

緩存之美——如何選擇合適的本地緩存?

FPGA設計案例:數據緩存模塊設計與驗證實驗

FPGA設計案例:數據緩存模塊設計與驗證實驗

評論