在依賴于當前集成電路的系統中,連續的硅結構已經使電磁波成為一個越來越重要的設計因素。功率面噪聲是信號完整性問題的主要來源。

芯片、封裝、PCB和VRM都會產生電源噪聲。電源噪聲也會由于核心和輸入輸出開關而產生。晶體管供電軌上的電壓波動導致抖動增加和電壓裕度降低。這些波動對工作頻率有直接影響。

芯片外集成電路之間的信號速度穩步提高,例如,在2.5D和3D集成中,集成電路被分割。它們之間的通信是通過插入器進行的,或者集成電路利用硅通孔相互堆疊。

集成電路之間的通信速度決定了系統的速度。因此,互連和封裝在決定整個系統性能方面起著至關重要的作用。

高速信號是什么意思?

許多設計師認為50MHz及以上的信號是高速的。它取決于信號的邊緣速度-上升和下降時間。我們可以用TDR發生器的1kHz重復率產生10GHz噪聲。這是關于邊緣速度。換言之,PCB可顯著降低電路性能的信號頻率稱為高速。考慮到信號速度的PCB設計過程被定義為高速或復雜電路板。例如,主板、路由器和智能手機。

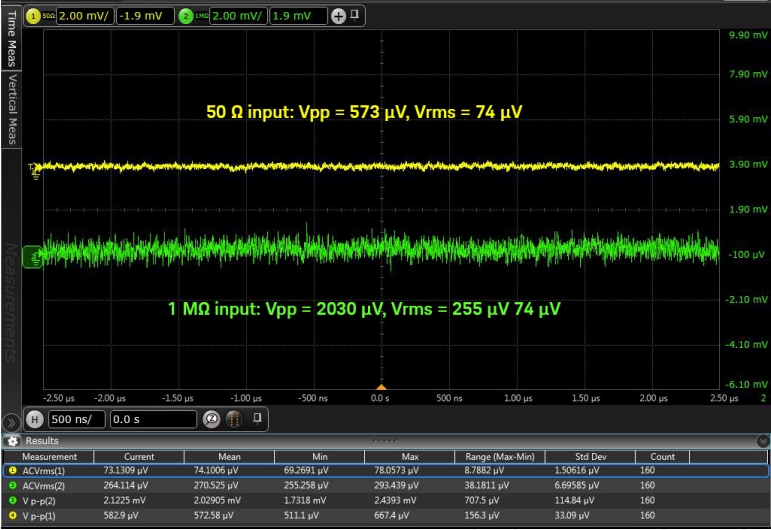

什么是噪聲?

它往往會掩蓋我們希望看到的信號。不需要的信號被定義為噪聲。任何我們不希望在信號中出現的東西都被稱為噪聲。

配電網通常與寄生菌有關。我們在這里討論的寄生蟲是電阻和電感。每次電路切換時,這些寄生電路在晶體管級電路的Vdd和接地節點之間產生噪聲。這稱為電源噪聲。這種噪聲通過軌跡傳播,并在傳播過程中拾取反射和串擾。當信號到達接收器時,它將由最初預期的帶有噪聲和串擾的信號組成。設計者應該設置一個噪聲預算,這樣你就有了一個可以在電路中接受的預定義噪聲水平。

什么是功率完整性?

功率完整性(PI)基本上是從輸入源向負載獲取適當的功率。更具體地說,這一切都是為了給集成電路芯片上的晶體管提供穩定的電源。PI是傳遞到模具上的電路的功率質量。

芯片是在封裝中發現的實際硅片。模具放在包裝上;包裝放在印刷電路板上。

在電子工業中,電源完整性是指分析系統中如何有效地將電源轉換并從電源傳輸到負載。噪聲在兩端(源和負載)產生。VRM和“負載”一樣會產生噪聲,當然,板上的其他任何東西也會通過串擾產生噪聲。電源完整性設計只不過是管理電源噪聲。管理晶體管的電壓和接地端子上的電源噪聲,使其高速工作,這稱為電源完整性設計。

電源完整性是指確保所有的電路和設備都有適當的電源,從而達到電路的預期性能。這不僅僅是保持電壓在允許的范圍內。設備中的大多數電路都是專用于其電源系統的。 “今天的智能手機有50%到80%的電路專用于其電力系統。”因此,設計一個好的PDN成為一個主要方面。

我們從電路將網絡從根本上分為兩類:

信號完整性:這里我們關注所有的互連。傳輸線。依靠Spice軟件進行仿真。我們感興趣的參數是驅動器輸出的反射和上升時間。

配電網:它是一個獨立的實體。我們感興趣的參數是目標阻抗。根據史蒂夫桑德勒的說法,“目標阻抗不起作用,除非阻抗也是平坦的。信號完整性影響電源完整性,電源完整性影響信號完整性。”

審核編輯黃宇

-

電源

+關注

關注

185文章

18364瀏覽量

256194 -

芯片

+關注

關注

459文章

52481瀏覽量

440573 -

PI

+關注

關注

12文章

225瀏覽量

113184 -

信號

+關注

關注

11文章

2851瀏覽量

78258

發布評論請先 登錄

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

電源完整性基礎知識

電源完整性分析及其應用

聽懂什么是信號完整性

淺談電源完整性的重要性

淺談電源完整性的重要性

評論