作者:顧波,張紅濤,劉新宇,邱道尹

隨著國家電力系統(tǒng)兩網(wǎng)改造工程的逐漸推進及“一戶一表,供電到戶”政策的貫徹實施,電力用戶數(shù)量急劇膨脹,用電網(wǎng)絡日益龐大,供電企業(yè)的用電管理任務也越來越重,加之國家供電的發(fā)送配分開,更要求供電企業(yè)加大對各大中小電戶的監(jiān)控力度。而傳統(tǒng)的抄收方式主要是依靠人工每月定期上門抄取,這種做法不僅耗費大量的人力物力,工作效率低,給用戶帶來諸多不便,同時發(fā)生電費拖欠現(xiàn)象,造成電力公司的損失。低壓電力線載波遠程抄表系統(tǒng)是利用現(xiàn)有的低壓電力網(wǎng)和公共電話網(wǎng)作為數(shù)據(jù)采集與傳輸通道,不僅從根本上克服了人工抄表帶來的諸多缺點,實現(xiàn)了對用戶用電量的自動抄表及收費管理等多種功能,而且具有施工量小、可靠性高、成本低等優(yōu)點。 但現(xiàn)有低壓電力線載波遠程抄表系統(tǒng)由于各種原因,存在這樣或那樣的弊端,例如負荷情況復雜、噪聲干擾強且具有時變性、信號衰減大、信道容量小等。如何克服這些缺點,是現(xiàn)階段低壓電力線載波遠程抄表系統(tǒng)設計的主要目標。本文所用的基于令牌存儲技術的采集器設計與實現(xiàn)技術,就是為了克服以上缺點的一種方法。

1 采集器硬件設計

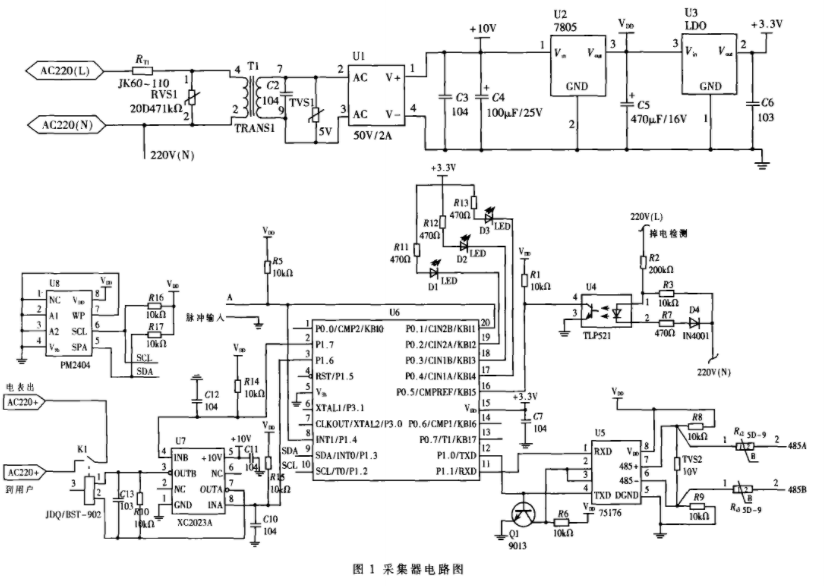

1.1 采集器電路設計

采集器的電路設計如圖1所示。采集器是數(shù)據(jù)進行采集、累計、傳輸?shù)牟考湓O計的好壞將直接影響整個抄表系統(tǒng)的正確性。所以,采集器的設計是整個系統(tǒng)設計最為關鍵的一步,在設計采集器時,需做到以下三點:

(1)實時記錄電表脈沖信號,并按要求保存,可根據(jù)脈沖個數(shù)等參數(shù)計算出當前電表度數(shù)。

(2)可實現(xiàn)繼電器控制、狀態(tài)監(jiān)視并可記錄繼電器狀態(tài)。

(3)可讀取電表度數(shù)、電表地址等信息,并可對其進行參數(shù)設置,進行欠費指示、繼電器通斷等控制。

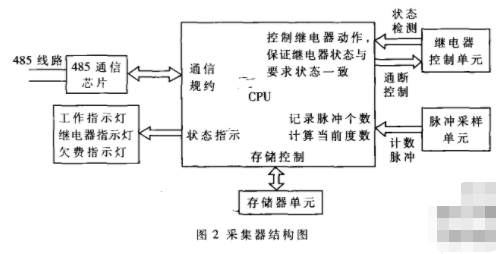

1.2 采集器各部分功能

采集器總體結構如圖2表示,其各部分功能如下:

(1)485通信芯片:主要實現(xiàn)采集器與上位機之間的通信,從而可以從采集器的存儲器中讀取相關數(shù)據(jù),其具體通信協(xié)議以國家標準為主。

(2)狀態(tài)指示:指示當前電表的工作狀態(tài),由3只二極管組成,其中一只表示正常工作;另一只表示用戶欠費;第三只表示繼電器動作,切斷用戶電表。

(3)狀態(tài)檢測:在系統(tǒng)掉電或重新啟動時,確保啟動時的狀態(tài)與掉電前的狀態(tài)相符合。

(4)脈沖采樣:完成脈沖的采集與計數(shù)任務。

(5)存儲控制:主要存儲電表的地址、初始值、變比參數(shù)、已有的脈沖個數(shù)、已記錄的電表數(shù)及繼電器在系統(tǒng)掉電前的狀態(tài)。

2 采集器軟件設計

2.1 基于令牌存儲技術的數(shù)據(jù)存儲設計

在進行采集器的設計時,數(shù)據(jù)準確、安全地存儲和傳輸是非常重要的,其結果決定著其他部分的正常工作。但由于采集器工作在現(xiàn)場的最前端,容易受到環(huán)境的影響,如采集器的突然掉電、數(shù)據(jù)在存儲過程中突然受到計數(shù)脈沖中斷的影響等,這些都會導致寫到存儲器中的數(shù)據(jù)不準確。如何克服這些不足,是采集器設計過程中的一個難點。根據(jù)采集器的實際工作環(huán)境,本文提出一種基于令牌儲存技術的數(shù)據(jù)存儲設計方法,該方法能很好地解決數(shù)據(jù)存儲過程中的不準確和不安全現(xiàn)象。

該方法的具體思路為:在存儲區(qū)中開辟三個互不相連的存儲空間,分別定義為ADDR1、ADDR2、ADDR3,每個存儲區(qū)又分為兩部分,第一部分存儲令牌,用tokening表示(用一個整數(shù)表示),第二部分存儲當前電表度數(shù),用memdata表示。下面詳細說明本算法的思想。

(1)系統(tǒng)初始參數(shù):當系統(tǒng)第一次使用時,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)值全部設置為零,把ADDR1.memdata、ADDR2.memdata和ADDR3.memdata中的數(shù)據(jù)設置為0、0.01、0.02(其中0.01代表0.01度電)。

(2)當用電量有0.01度時,需要將這0.01度電加到存儲區(qū)的用電度數(shù)中。首先把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)相加,其和為0時,則把ADDR1.memdata中的數(shù)據(jù)加0.01,同時改變ADDR1.tokening中的數(shù)據(jù),使其為1。

(3)當用電量第二次到0.01度時,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)相加,其和為1時,由此可以得到ADDR1.memdata剛被存儲過,把ADDR2.memdata中的數(shù)據(jù)加0.01,改變ADDR2.tokening中的數(shù)據(jù),使其為2。

(4)當用電量第三次到0.01度時,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)相加,其和為3時,由此可以判斷ADDR1.memdata和ADDR2.memdata已經(jīng)存儲過,把ADDR3.memdata中的數(shù)據(jù)加0.01,改變ADDR3.tokening中的數(shù)據(jù),使其為4。

(5)當用電量第四次到0.01度時,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)相加,其和為7,這時可以判斷ADDR1.memdata、ADDR2.memdata和ADDR3.memdata都已經(jīng)被存儲過了,重新從ADDR1.memdata開始存數(shù),把ADDR1.memdata中的數(shù)據(jù)加0.01,改變ADDR1.tokening中的數(shù)據(jù),使其為0。

(6)當用電量第五次到0.01度時,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)相加,其和為6,這時可以判斷ADDR1.memdata中數(shù)據(jù)剛改變,應該把數(shù)據(jù)存儲到ADDR2.memdata中,把ADDR2.memdata中的數(shù)據(jù)加0.01,并把ADDR2.tokening中的數(shù)據(jù)改為0。

(7)當用電量第六次到0.01度時,把ADDR1.tokening、ADDR2.tokening和ADDR3.tokening中的數(shù)據(jù)相加,其和為4,這時可以判斷ADDR1.memdata和ADDR2.memdata都已經(jīng)被存儲過了,應該把ADDR3.memdata中的數(shù)據(jù)加0.01度,并把ADDR3.tokening中的數(shù)據(jù)改為0。這時的令牌狀態(tài)又重新回到了初始狀態(tài),并且保證了數(shù)據(jù)區(qū)中的數(shù)據(jù)相差0.01度電,當有新的數(shù)據(jù)到來時,令牌數(shù)據(jù)又重新從初始狀態(tài)開始。

(8)錯誤處理:當系統(tǒng)掉電或被其他干擾影響時,經(jīng)常會出現(xiàn)存儲數(shù)據(jù)不正確的現(xiàn)象,如果使用上述存儲方法,可以克服這些錯誤。每次在更改存儲區(qū)中的數(shù)據(jù)或向上位機發(fā)送電表度數(shù)時,都會首先把三組存儲區(qū)中的數(shù)據(jù)和令牌值取出來,然后根據(jù)令牌值,把三組數(shù)據(jù)兩兩相減,根據(jù)數(shù)據(jù)間的差額可以判斷三組存儲區(qū)中的數(shù)據(jù)是否正確,若正確才進行改變或發(fā)送,否則可以根據(jù)另外兩組數(shù)據(jù)來還原其中一組數(shù)據(jù),從而保證整個數(shù)據(jù)在系統(tǒng)運行期間的正確性。

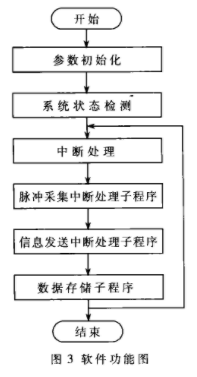

2.2 軟件系統(tǒng)設計

軟件設計的任務主要是實現(xiàn)采集器的各部分功能,如圖3所示。包括485芯片通信功能設計、脈沖采集設計、數(shù)據(jù)存儲設計、狀態(tài)檢測設計、系統(tǒng)初始化等部分功能。

基于令牌儲存技術設計思想設計的采集器,極大地提高了采集器的穩(wěn)定性和數(shù)據(jù)的正確性。采用本技術設計的采集器,在河南鄭州、濟源、周口等地市使用,其抄表成功率在99.8%以上,很好地滿足了用戶要求。

責任編輯:gt

-

芯片

+關注

關注

459文章

52282瀏覽量

437463 -

繼電器

+關注

關注

133文章

5429瀏覽量

151031 -

數(shù)據(jù)采集

+關注

關注

40文章

7014瀏覽量

115918

發(fā)布評論請先 登錄

基于FPGA的軟硬件協(xié)同仿真加速技術

單片機軟硬件聯(lián)合仿真解決方案

支持過程級動態(tài)軟硬件劃分的RSoC設計與實現(xiàn)

基于SoPC的狀態(tài)監(jiān)測裝置的嵌入式軟硬件協(xié)同設計

基于Altera FPGA的軟硬件協(xié)同仿真方法介紹

如何去實現(xiàn)RCC系統(tǒng)時鐘的軟硬件設計呢

單片機測控系統(tǒng)的軟硬件平臺技術

DTMF遠程通信的軟硬件實現(xiàn)技術

基于SoPC的狀態(tài)監(jiān)測裝置的嵌入式軟硬件協(xié)同設計與實現(xiàn)

基于FPGA的軟硬件協(xié)同測試設計影響因素分析與設計實現(xiàn)

電源電路板軟硬件設計

為什么要從“軟硬件協(xié)同”走向“軟硬件融合”?

軟硬件融合的概念和內(nèi)涵

基于令牌儲存技術實現(xiàn)數(shù)據(jù)存儲電路的軟硬件設計

基于令牌儲存技術實現(xiàn)數(shù)據(jù)存儲電路的軟硬件設計

評論