今天關于蔚來最勁爆的消息來自 36kr,說蔚來正在計劃自研自動駕駛芯片,同時內部已經成立了代號為 Smart HW (Hardware)的硬件團隊。

消息出來后,我們打聽了一番,蔚來計劃自研芯片這個事,的確如 36 kr 所言處于推動環節,甚至可以說是「八字沒一撇」,但想法、計劃肯定是有的。

36 kr 文章的關鍵點也正如其所言是「向公司高管和股東們吹吹風,提前做一些溝通。」

至于 Smart HW 這個團隊,我們得到的消息不多,但未收到否認的表態。

很多人對于蔚來的期望,其實不僅僅是一家生產高端智能電動汽車的中國汽車公司,或者新造車公司。更多還是希望它能成為一家布局廣泛、覆蓋智能、軟硬件、具備更多可能性的科技公司。

有關科技公司這個事,我們曾問過李斌。李斌說,蔚來原本就是一家科技公司。

因而,雖然現在「八字沒一撇」,但我們還是期待蔚來真的能向這個方向發展。

剩下的問題有兩個。

第一,按照 36 kr 的報道,蔚來年底會做年度預算,自研芯片的投入資金較大,需要上會,「以李斌現在的聲望,這個項目敲定的難度不會太大。」

第二、項目敲定了,但芯片自研,蔚來能做成嗎?能有像特斯拉 FSD 芯片一樣的蔚來芯片嗎?

前一個問題,我們無法解答。今天主要來談談第二問題,自研芯片的難度在哪里?自研又指的是什么?蔚來需要客服什么困難?

下面開始。

蔚來造芯,需要爬什么坑?

一個前提是:硅芯片行業的準入門檻(說白了就是錢)在不斷提高,而且終有一天會高到無法承受。

但想要把賬算清楚,我們首先要知道制造芯片需要經歷怎樣的步驟,哪些部分特別燒錢,以及預測一下蔚來會選擇怎樣的芯片工藝(不同工藝成本也不一樣)。

想要把芯片造出來不難,找臺積電/三星/格羅方德這樣的代工廠生產,有錢就能搞定。真正需要花心思,并且能體現蔚來自研能力的,是芯片設計。

芯片設計分為兩大步,前端設計(也叫邏輯設計)和后端設計(也叫物理設計)。區分前后端的標志,是前端設計最終得到芯片電路圖,而后端設計則主要包括大量驗證和布局分析。

其中前端設計主要分為規格制定 Formulation→規格設計 Specificcation→HDL 硬件編碼→功能驗證 Function verification→邏輯綜合 Logic Synthesis→形式驗證 Verification。

后端設計則包括可測性設計 Design For Test→布局規劃 FloorPlan→生成版圖數據 Layout GDSII→版圖物理驗證 Layout Physical Verification 等主要步驟。

做完以上所有,芯片的設計就算完成了。問題是,設計芯片要多久?

舉個例子,下面是 2019 年 9 月,AMD 發布的自家 CPU 芯片規劃圖:

可以看到 ZEN 3 架構的芯片在當時屬于「Design Complete 設計完成」階段,而 ZEN 3 在今年 10 月中剛剛發布,預計 11 月開售。ZEN 4 當時處于「in Design 設計中」階段,預計 2021 年底發布。

也就是說,假設蔚來的自動駕駛芯片已經處于設計階段,那么我們最早也要2022 年底才能迎來發布。因為芯片設計完成之后,還需要流片(相當于小規模樣品)和最終的成品驗證環節,這部分也會消耗大量時間。

設計講清楚了,接下來要討論的,是如果蔚來要做自動駕駛芯片,會選擇怎樣的工藝。

其實答案已經呼之欲出——7 納米。

目前主流的自動駕駛芯片均使用了 14 納米世代工藝,像是特斯拉的 FSD 芯片用的是三星 14 納米、英偉達 Xavier 用的是臺積電 12 納米(優化版 14 納米),華為 MDC 搭載的昇騰 Ascend 310 也是用的臺積電 12 納米。

但如果蔚來真的劍指 2023,7 納米才是必由之路。

8 月份,臺積電就已經宣布,特斯拉的下一代自動駕駛芯片將由博通聯合設計,使用臺積電的 7 納米工藝制造。被英特爾收入麾下的Mobileye,也宣布其 EyeQ5 芯片會使用7納米工藝打造。

至于已經開完發布會的英偉達,Drive Orin 大概率也使用了 7 納米工藝(未經官方確定),最終實現增加一半功耗,提升 6 倍性能。

換而言之,如果蔚來想做一枚跟上時代潮流的自動駕駛芯片,7 納米工藝再難也要攻克——但到底有多難呢?

我們開始算賬。

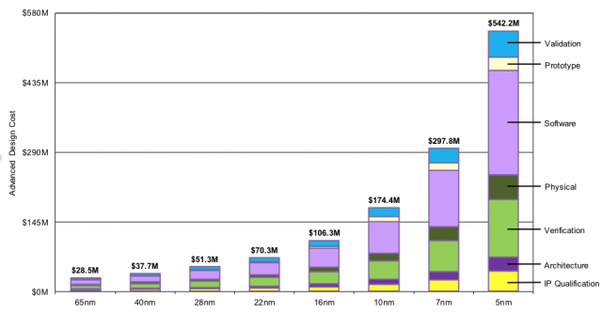

根據 extremetech.com 的估算數據,7 納米工藝芯片的設計成本高達2.97 億美元(19.7 億元),這還最樂觀的,初次流片即成功的成本。

流片 tapeout,指的是在設計完成之后,正式量產之前,芯片設計公司和代工廠之間預產一部分樣品,用于最終驗證的小批量生產環節。根據工藝不一樣,流片的報價也不一樣。

代工廠的流片成本,是世界上被保護得最好的商業機密之一,即使是已經沿用了多年的 14 納米,我們也找不到一份精確的報價。

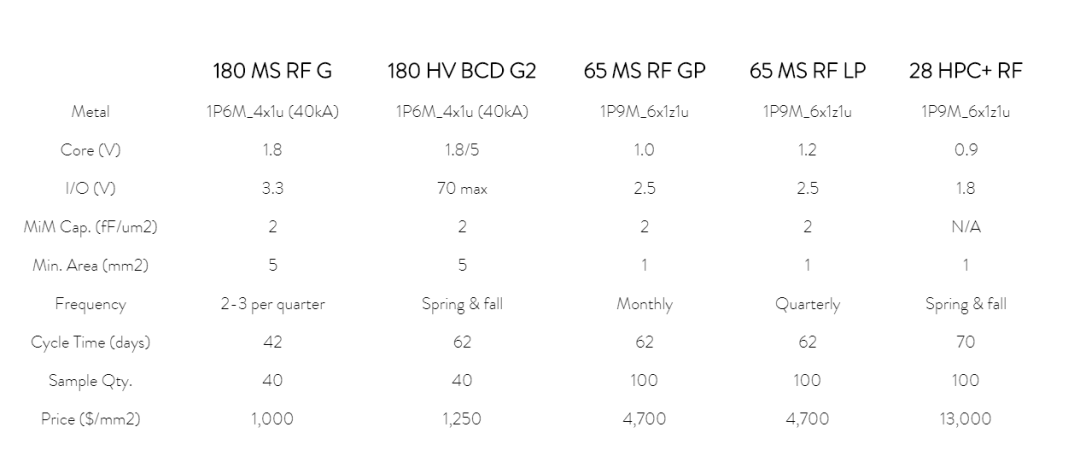

我們能找到且確定真實的,只有「老掉牙」的,10 年前的臺積電 28 納米工藝流片報價——按照芯片表面積算錢,1.3 萬美元每 mm2 每次,是兩個節點之前 65 納米工藝流片單價的近 3 倍。

如果按照每個節點漲一倍估算,28→20→14→10→7 這樣下來,7 納米流片成本就會達到每 mm2 21 萬美元。此前有傳言說華為的麒麟 990(113.31mm2)每次流片成本高達 3000 萬美元(2 億元),單價甚至略高于估算值。

也就是說,蔚來想要自己造性能足夠強悍的自動駕駛芯片,可能要付出20 億左右的前期成本,加上每次接近 2 億的試錯成本,以及起碼兩年,甚至 3 年的時間成本。更不要說到了下一代 5 納米工藝時,研發成本預計會達到 5.7 億美元起(約 40 億元)。

何況以上計算,還沒考慮另一個關鍵因素——人。

特斯拉憑借著馬斯克的個人魅力和不像車企的激進思維,招募來了可能是地球最杰出的芯片架構師 Jim Keller,為 FSD 打下基礎。如今蘋果 A5-A9 芯片的負責人之一 Pete Bannon 還在特斯拉把持大局。英特爾和英偉達則是最近 20 年 CPU 和 GPU 的代名詞,他們都有變態級別的人才儲備。

錢、人、時間缺一不可,這就是蔚來自研芯片需要過的三道關卡。

智能電動時代,自研是車企必修課嗎?

昨天,何小鵬在 P7 第一萬輛下線活動中表示,「未來幾年是科技和裝備的競爭,如果你自己沒有全研發能力,很難在這個領域里面贏。不光要能想到,還要能夠做到。」

「自研」,這兩年越來越成為車企喜歡掛在嘴邊的詞匯。

就連和 Tier1 穿慣了同一條褲子的傳統車企,也都在試圖擺脫供應鏈的帽子,轉而強調「深度合作」、「共同研發」。比如豐田聯合英偉達、寶馬找上 Mobileye。

到底怎樣才叫「自研」?

自動駕駛領域的「自研」定義其實挺廣泛的。自研傳感器(毫米波雷達、攝像頭)、自研算法、自研芯片...做到任意一個,其實都能算「自研」。

其中最核心的、自上而下的,一定是自研芯片。完全的硬件支配權同時可以帶來完全的軟件自由度。而要想達到何小鵬所說的「全研發」,自研芯片是更關鍵的助力。

然而,即使蔚來真的邁出自研芯片這一步,長時間持續且越來越高的芯片研發投入、芯片制造成本如何攤平、怎么從 Mobileye 時代順利過渡、老車型要不要做兼容...等等,都是必須考慮,且非常重要的問題。

當然,誠如我們打探到的「八字還沒一撇」,也許這個 Smart HW 項目還只是在討論階段,甚至不一定會上馬。

但誰能抵擋「垂直整合」的誘惑呢?

責任編輯:xj

原文標題:關注|傳李斌正推動蔚來自研自動駕駛芯片,能成嗎?

文章出處:【微信公眾號:汽車工程師】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

460文章

52520瀏覽量

441086 -

自動駕駛

+關注

關注

790文章

14321瀏覽量

170693 -

蔚來汽車

+關注

關注

1文章

648瀏覽量

20919

原文標題:關注|傳李斌正推動蔚來自研自動駕駛芯片,能成嗎?

文章出處:【微信號:e700_org,微信公眾號:汽車工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

今日看點丨蔚來自研全球首顆車規5nm芯片!;沃爾沃中國區啟動裁員計劃

AI將如何改變自動駕駛?

蔚來自研大鑄件新合金完成驗證并量產

NVIDIA DRIVE技術推動自動駕駛發展

Arbe誠邀您共赴CES 2025,探索未來自動駕駛

一文聊聊自動駕駛測試技術的挑戰與創新

標貝科技:自動駕駛中的數據標注類別分享

標貝科技:自動駕駛中的數據標注類別分享

Lyft攜手Mobileye推動自動駕駛出行服務規模化發展

從小鵬、理想、蔚來布局看自動駕駛發展趨勢

傳李斌正推動蔚來自研自動駕駛芯片:八字沒一撇

傳李斌正推動蔚來自研自動駕駛芯片:八字沒一撇

評論