本應用筆記將介紹帶有異步抽取濾波器的音頻模數轉換。它提出了轉換過程對高頻系統(tǒng)時鐘的要求,并提出了這種音頻轉換的解決方案。

介紹

現代高性能 delta-sigma 模數 (A/D) 和數模 (D/A) 音頻轉換系統(tǒng)需要高頻系統(tǒng)時鐘(主時鐘)用于其轉換過程,通常超過 12 MHz .該時鐘上的抖動是這些系統(tǒng)性能下降的一個重要來源。在包含轉換器和基于晶體的時鐘的產品中,這通常不是問題。然而,這在網絡音頻系統(tǒng)中可能是一個特別難以解決的問題,錄音系統(tǒng)是轉換節(jié)點和網絡以采樣率或在同一時鐘域內運行。在這些系統(tǒng)中恢復低抖動主時鐘的最常見方法是使用鎖相環(huán) (PLL)。PLL 電路有多種形式,各有優(yōu)勢。然而,

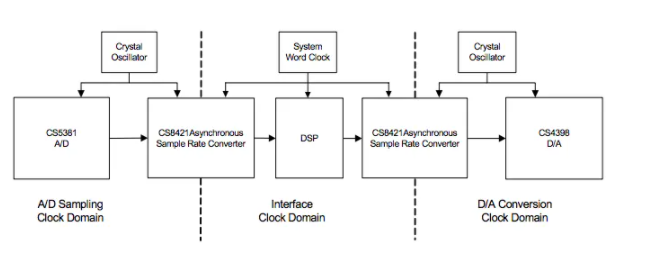

另一種方法是創(chuàng)建一個系統(tǒng)架構,其中 A/D 和 D/A 轉換節(jié)點在獨立于網絡或系統(tǒng)時鐘域的本地時鐘域內運行。使用采樣率轉換器 (SRC) 可以輕松實現具有獨立時鐘域的系統(tǒng),如圖 1 所示。該架構還允許轉換過程以固定采樣率運行,該采樣率始終高于網絡或接口采樣率。這種方法的基本優(yōu)點是轉換過程不受接口時鐘抖動的影響,并由本地無抖動晶體振蕩器控制。

具有獨立時鐘域的音頻系統(tǒng)架構

CRD5381概述

CRD5381 是一種 4 通道參考設計,它結合了 CS5381 模數轉換器和 CS8421 異步采樣率轉換器,以創(chuàng)建本應用筆記中所述的模數轉換系統(tǒng)。CRD5381 本質上是一種 2 通道設計,其中已復制 2 通道模塊以創(chuàng)建第 3 和第 4 通道。每個 2 通道部分包括所需的模擬輸入緩沖器、CS5381 A/D 轉換器和 CS8421 異步采樣率轉換器。該參考設計還包括時鐘生成、狀態(tài)報告和所需的系統(tǒng)復位功能。此外,雙 CS8421 器件可以配置為 4 通道時分復用 (TDM) 接口。

編輯:hfy

-

模數轉換器

+關注

關注

26文章

3306瀏覽量

128034 -

模數轉換

+關注

關注

1文章

220瀏覽量

37389

發(fā)布評論請先 登錄

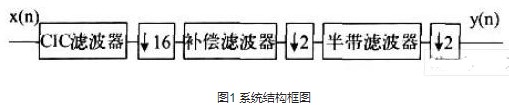

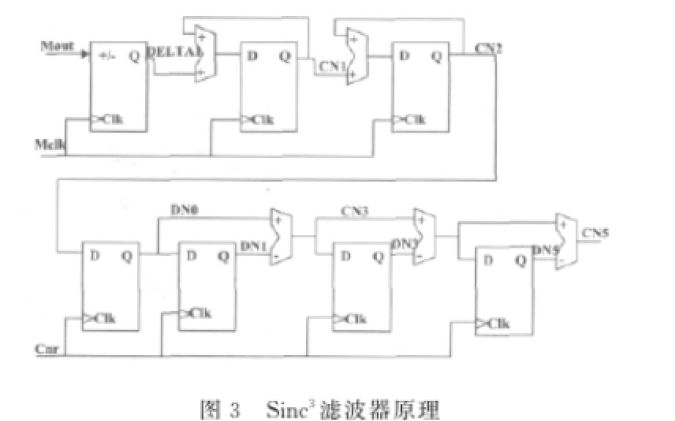

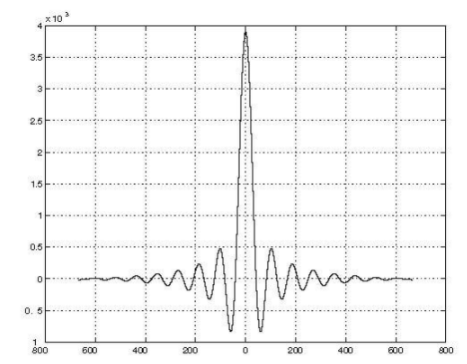

講述Δ-Σ模數轉換器數字濾波器最常用的正弦濾波器

Σ-Δ模數轉換器之數字濾波器類型與用途

CIC抽取濾波器MATLAB仿真和FPGA實現

數字抽取濾波器的DSP優(yōu)化設計

級聯COSINE濾波器在抽取濾波中的研究

數字下變頻中抽取濾波器的設計及FPGA實現

以FPGA為基礎的Σ-? 轉換中抽取濾波器的設計過程詳解

高頻數字抽取濾波器的設計

FPGA的FIR抽取濾波器設計詳細教程

改進型64倍降采樣數字抽取濾波器的設計與仿真分析

怎么樣使用FPGA設計ADC數字抽取濾波器

關于抽取和插值濾波器的介紹

淺談帶有異步抽取濾波器的音頻模數轉換

淺談帶有異步抽取濾波器的音頻模數轉換

評論