本文介紹了基于FPGA、以并行多相濾波結構為算法基礎的超寬帶數字下變頻技術。設計過程包括高速AD信號降速預處理,應用SysGen開發環境完成的數字混頻、多相濾波和數據抽取,并通過仿真驗證了算法

2014-02-22 10:23:41 3144

3144 本帖最后由 eehome 于 2013-1-5 10:03 編輯

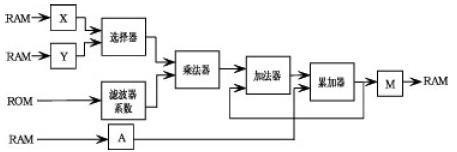

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

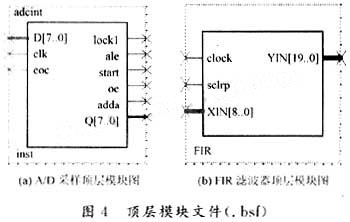

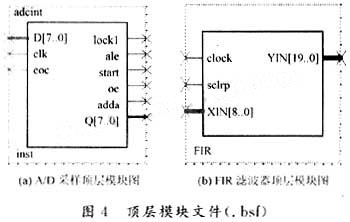

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

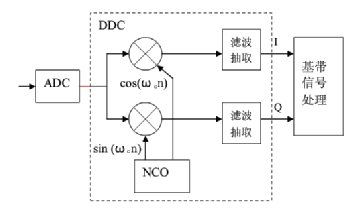

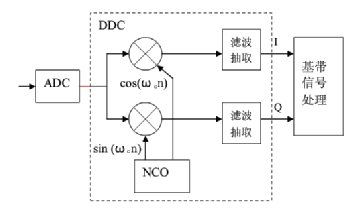

實現FPGA數字下變頻的多類濾波器分組級聯技術分析1 引 言 本文針對以下高效算法做了總結,進行合理的分組級聯并引入流水線技術以便于在FPGA上實現。數字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

AD采樣80MHz,中頻信號60MHz,在數字下變頻時NCO輸出頻率設置為多少?

2017-02-15 16:00:19

數字下變頻中的抽取和直接降低AD的采樣率有什么區別?比如AD采樣率100M,下抽倍數為4倍,和AD采樣率25M有什么區別。

2017-11-03 21:53:13

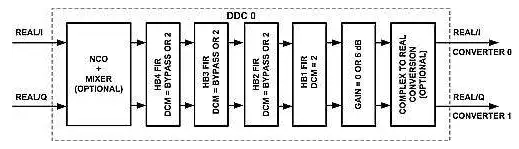

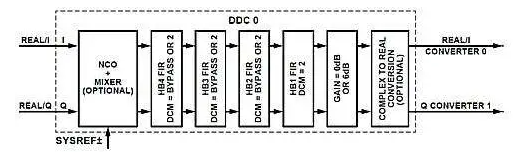

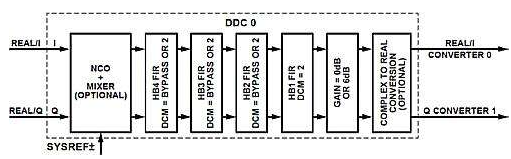

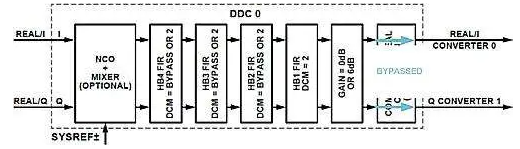

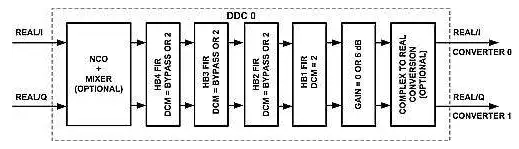

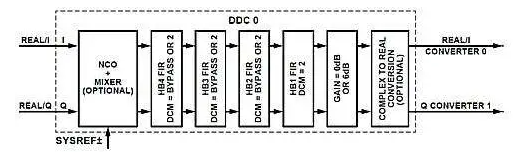

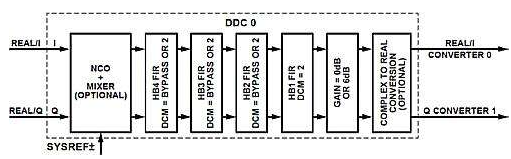

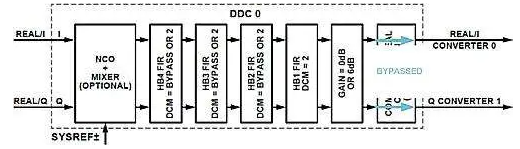

抽取濾波器,DDC可實現處理增益,并使SNR改善達10 dB。在表1中,我們可以看到當DDC工作于實數模式和復數模式時,不同的抽取濾波器選擇所提供的可用帶寬、抽取率、輸出采樣速率和理想SNR改善情況

2018-10-18 11:05:38

時的輸入時鐘為368.64 MHz,模擬 輸入頻率為270 MHz。首先,理解AD9680中數字處理模塊的 設置很重要。AD9680將設為使用數字下變頻器(DDC),其輸 入為實數,輸出為復數,數控

2018-11-01 11:19:48

各位大俠,小弟最近要設計一個用于sigma-delta ADC的數字抽取濾波器,甚是著急,但是苦于毫無頭緒,敬請各位高手指點啊。下面是設計指標: 信號頻率為250hz,調制器采樣頻率頻率為

2012-02-26 22:00:16

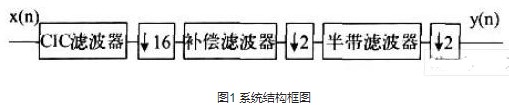

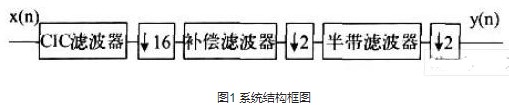

256KHZ,輸出1bit數字信號,現需要降采樣,抽取因子128,要求最終輸出24bit,擬用三級結構,第一級為5階的抽取率為32的cic濾波器,第二級為抽取率為2的cic補償濾波器,第三極為半帶濾波器,濾波器的截止頻率為1K。硬件實現,望各位大俠指點。wbpotato@163.com qq:446497438.

2012-02-26 15:52:55

CIC抽取濾波器MATLAB仿真和FPGA實現(1)設計理想濾波器目標:1、濾波器在有效頻段內紋波滿足設計要求。2、抽取或內插處理后在有效頻段內不產生混疊。3、濾波器實現簡單,需要資源較少。這個

2021-08-17 08:27:40

本帖最后由 eehome 于 2013-1-5 10:01 編輯

IIR數字濾波器的Matlab和FPGA實現

2012-08-20 22:16:49

。【關鍵詞】:CIC抽取濾波器;;余弦濾波器;;ISOP濾波器;;遞歸結構;;部分多相結構【DOI】:CNKI:SUN:GLDZ.0.2010-02-006【正文快照】:數字下變頻技術是從寬帶高速的數據流

2010-06-02 10:07:03

近年來,軟件無線電已經成為通信領域一個新的發展方向,數字下變頻技術(Digital Down Converter-DDC)是軟件無線電的核心技術之一,也是計算量最大的部分。基于FPGA的DDC

2019-10-12 08:17:00

近年來,軟件無線電已經成為通信領域一個新的發展方向,數字下變頻技術(Digital Down Converter-DDC)是軟件無線電的核心技術之一,也是計算量最大的部分。基于FPGA的DDC

2019-09-20 06:13:11

DSPBuilder設計了一個4階FIR濾波器,并用QuartusII進行硬件仿真,仿真結果表明設計FIR濾波器的正確性。同時使用IPCore開發基于FPGA的FIR數字濾波器,利用現有的IPCore在FPGA器件上實現濾波器設計。

2012-08-11 15:32:34

數字濾波器、DSP器件或可編程邏輯器件(如FPGA)實現。因為,用FPGA實現數字濾波器具有實時性強、靈活性高、處理速度快以及小批量生產成本低等優點,所以得到了較為廣泛的應用。本文以巴特沃思數字

2019-07-08 07:18:25

下變頻,抽取,封裝為幀,再通過千兆以太網傳輸到PC進行保存。但是由于這個系統的開發是比較復雜的,因此本人想在進行實際硬件系統設計之前先進行仿真,仿真的目的主要用于驗證在FPGA中進行數字信號處理

2015-04-28 09:56:02

基于FPGA設計了一高速數字下變頻系統,在設計中利用并行NCO和多相濾波相結合的方法有效的降低了數據的速率,以適合數字信號處理器件的工作頻率。

2019-09-26 07:06:35

得到數字中頻信號,但其數據率過高,故其成為數字處理的瓶頸。一般需要使用數字正交解調技術將信號搬移至基帶,然后通過多速率信號處理技術來設計抽取濾波器,以降低數據率,最終實現數字FIR濾波器。

2019-06-05 06:30:45

采用ADC(LTC2208)、FPGA和SDRAM(HY57V561620)設計高速的數據采集及正交下變頻系統,其中數據采樣速率90MSPS;實現70M中頻的數字正交下變頻…………請求大牛的幫助啊,我是小菜鳥,這方面還需要你們的大力提攜啊,萬分感謝

2014-04-01 10:44:33

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。

2019-08-21 06:24:03

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字上下變頻的FPGA實現方法,以及Altera提供的一種數字信號處理的工具,DSP BUILDER。

2019-09-25 08:22:51

處理器(FPGA,DSP)是一個“瓶頸”;基于多相濾波的信道化接收機抽取在濾波之前,運算量小,且輸出速率低,便于FPGA實現,這使得在一片FPGA中實現數字信道化成為可能。

2019-08-22 08:01:34

數字上變頻/下變頻(DUC/DDC, digital up convert/ digital down convert)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率

2019-08-09 06:52:39

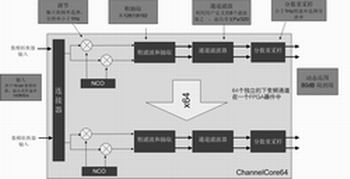

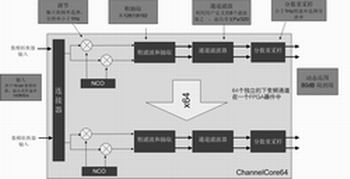

如何使用一個FPGA實現64個獨立的下變頻通道?

2021-04-29 06:37:05

濾波器在FPGA中的實現用FPGA來實現濾波器的設計優點用FPGA來設計濾波器,不但設計簡單,而且成本小,可靠性好。且無需像傳統的設計芯片一樣進行測試。主要優點:設計簡潔。若設計有誤,則只需

2021-07-30 07:03:10

濾波器是任何信號處理系統的關鍵組成部分,隨著現代應用的日趨復雜,濾波器設計的復雜程度也日益提高。采用 FPGA 設計和實現的高性能濾波器的能力是模擬方法所望塵莫及的。另外,采用FPGA

2019-09-18 08:28:47

收發器,只為在后續處理中對寬帶數據進行抽取和濾波時,就會產生不必要的系統負擔。賽靈思FPGA收發器資源可以得到更好的分配,以接收所需的低帶寬并疏導來自多個ADC的數據。可在FPGA的多相濾波器組信道器中

2019-07-29 07:14:03

我是Xilinx的全新用戶,請耐心等待。我想實現數字下變頻器,但我需要的參數不同于ISE中提供的DUC / DDC編譯器。例如,我沒有使用特定的無線標準,我的通道帶寬是10 kHz而不是提供的選擇

2019-02-12 10:58:29

本文將針對中頻PCM/DPSK遙測信號全軟化解調器中數字級聯抽取濾波器的設計及軟化實現進行研究。

2021-06-04 07:07:09

本文以實現抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現FIR抽取濾波器的設計方法。

2021-05-07 06:02:47

的頻譜。當需要窄帶時,ADC采樣、處理并消耗功率傳輸寬帶頻譜的效率很低。沒有必要在后期處理中使用大量FPGA收發器來抽取和過濾寬帶數據。高性能GSPS ADC讓數字下變頻(DDC)進駐到ADC內部。減少

2018-10-24 09:56:03

【作者】:李學易;郝祿國;盧曉鋒;【來源】:《電視技術》2010年02期【摘要】:就DVB/CMMB數字回波消除直放站研發中涉及的抗混頻數字抽取濾波器這一關鍵技術進行了詳細研究,對3種數字抽取濾波器

2010-04-22 11:30:26

簡要闡述數字下變頻器的發展和更新

2021-05-19 06:22:14

數字濾波器的實現一般有哪幾條途徑?寬帶無線通信的數字上下變頻是什么?濾波器的輸入數據流有什么特點?

2021-04-14 06:21:44

適合應用在多速率信號處理的前端,作為抗混疊濾波器來用,或者是作為后端的抗混疊插值濾波器。七、多級 Hogenauer CIC抽取濾波器的FPGA實現 Hogenauer CIC抽取濾波器是一種特殊

2015-08-29 15:25:38

,所以抽取器打開,此時才開始進行輸入數據與濾波器系數的卷積運算,如果再將抽取器后面的部分展開就是這樣的:當然,我們這個例子的濾波器長度為26,所以可以繼續往上加三、多相分解算法的FPGA實現首先當然是先將

2015-08-29 15:37:11

討論了軟件無線電接收機中數字下變頻處理技術中的CIC抽取濾波器結構原理,分析了CIC濾波器級聯ISOP濾波器進行抽取濾波的設計技術。驗證了ISOP濾波器對CIC濾波器帶內衰減補償的有

2009-05-26 20:44:21 21

21 探討了DDC中抽取濾波系統的設計方法和基于DSP Builder的具體實現方案,采用CIC濾波器、HB濾波器、FIR濾波器三級級聯的方式來降低采樣率,并進行了模型仿真,結果表明設計是可行的

2009-09-17 11:35:08 23

23 本文介紹了數字下變頻的組成結構,并通過一個具體的實例,給出了FPGA 實現的具體過程。

2009-11-30 14:11:52 34

34 在軟件無線電的下變頻模塊中,級聯梳狀積分濾波器有著重要的應用,其主要作用是信號的抽取與低通濾波。文中總結了級聯梳狀積分抽取濾波器的理論要點,并介紹了采用FPGA

2010-01-06 15:16:45 31

31 數字濾波器在FPGA中的實現

2010-02-09 10:21:27 76

76 FPGA在軟件無線電中的工程應用之數字上下變頻篇

2010-02-09 11:10:36 59

59 介紹了一種基于新型FPGA的高速數字下變頻的實現方法,它充分利用數字下變頻的優化算法以及FPGA領域的新技術,去除由于數據速率過高而造成的各種瓶頸,極大地減少了計算量和FPG

2010-07-02 16:49:24 21

21 數字下變頻是軟件無線電系統的重要組成部分,主要完成對信號的混頻、濾波、抽取和整形等工作,包括數字混頻模塊和抽取濾波模塊。在數字下變頻系統實現方案中,輸入的模擬

2010-11-02 15:26:27 48

48 基于FPGA芯片Stratix II EP2S60F672C4設計了一個適用于寬帶數字接收機的帶寬可變的數字下變頻器(VB-DDC)。該VB-DDC結合傳統數字下變頻結構與多相濾波結構的優點,實現了對輸入中頻信

2010-11-11 15:56:54 57

57 IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

摘 要:本文介紹了一種采用級聯結構在FPGA上實現任意階IIR數字濾波器的方法。此

2008-01-16 09:45:39 2276

2276

基于FPGA的數字濾波器的設計與實現

在信息信號處理過程中,如對信號的過濾、檢測、預測等,都要使用到濾波器,數字濾波器是數字信號處理中使用最廣泛的一

2010-01-07 10:45:35 3475

3475

使用一個FPGA便可實現的64通道下變頻器

RF Engines公司的ChannelCore64使設計者能夠用一個可對FPGA編程的IP核來替代多達16個DDC(直接下變頻器)ASIC,可顯著減少PCB面積

2010-01-18 16:34:34 1147

1147

摘 要:為了降低地震數據采集系統的成本和功耗,采用數字信號處理器(DSP)實現-△模數轉換器中的數字抽取濾波器算法。通過采取查表法、倒序循環遍歷法以及模擬循環尋址法等優化方法,以較低工作頻率實現了四通道四級抽取濾波運算,達到了系統設計的要求。

2011-02-25 16:00:23 68

68 為補償傳統CIC濾波器的通帶衰減,提出一種改進型的CIC抽取濾波器,即在SCIC濾波器之后級聯一個二階多項式內插濾波器。基于硬件實現的要求,給出改進型CIC濾波器的FPGA高效實現原理圖。仿真結果表明改進的CIC濾波器具有更好的通阻帶特性。

2011-03-15 14:06:35 52

52 數字下變頻是軟件無線電系統的重要組成部分,主要完成對信號的混頻、 濾波、抽取和整形等工作,包括數字混頻模塊和抽取濾波模塊。在數字下變頻系 統實現方案中,輸入的模擬中

2011-03-29 10:02:47 96

96 為了解決高速抽取濾波器系統中傳統CIC濾波器旁瓣抑制不夠的問題,通過對級聯COSINE抽取濾波器和傳統CIC抽取濾波器的原理推導進行對比,分析出級聯COSINE濾波器在幅頻特性上同CIC濾波

2011-05-03 18:11:53 31

31 基于多速率信號處理原理,設計了用于下變頻的CIC抽取濾波器,由于CIC濾波器結構只用到加法器和延遲器,沒有乘法器,很適合用FPGA來實現,所以本文分析了CIC濾波器的原理,性能及影

2011-08-26 15:12:11 160

160 寬帶短波信道模擬器是一種運用仿真技術對真實的短波信道進行模擬的儀器。首先指出數字下變頻在寬帶短波信道模擬器中的作用。然后,闡述了數字下變頻中的數控振蕩器、CIC 濾波器

2011-09-15 18:30:21 1669

1669

文中基于多速率數字信號處理原理,設計了用于數字下變頻技術的CIC抽取濾波器。通過分析CIC濾波器的原理及性能參數,利用MATLAB設計了符合系統要求的CIC濾波器,并通過FPGA實現了CI

2013-04-15 19:29:28 71

71 結構類型的fir數字濾波器的fpga實現、不同結構fft的fpga實現、數字正交下變頻的fpga實現、cordic和dds的fpga實現等。

2015-12-23 11:07:46 44

44 FPGA在軟件無線電中的工程應用之數字上下變頻篇

2016-04-25 09:38:10 8

8 基于FPGA的DDC數字下變頻設計,有興趣的同學可以下載學習

2016-04-27 16:18:12 59

59 設計和實現了基于FPGA的可編程數字下變頻器(DDC),用于寬帶數字中頻軟件無線電接收機中,主要完成了數字下變頻、數據抽取等功能。采用自頂向下的模塊化設計方法,將整個下變頻器劃分為基本單元,實現這些

2017-11-22 09:09:56 5706

5706

前端的調制器利用過采樣的方法將量化噪聲搬移到高頻段,后端的數字抽取濾波器必須再將高頻噪聲濾除,所以數字抽取濾波器的性能在整個Σ-? ADC中起著非常重要的作用。我們選用了一種抽取濾波器Sinck數字濾波器,它可以有效的濾除高頻噪聲滿足設計的需要,并且這種濾波器的算法中不需要乘法。

2018-07-18 18:31:00 3664

3664

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字

2017-11-25 02:31:01 259

259

設計數字下變頻器的抽取濾波器是一項艱巨任務。本文介紹一種能夠完成此項任務的簡便、易于理解的流程。

2018-07-13 08:13:00 2893

2893 數字下變頻是 無線通信 鏈路層的重要組成部分, 寬帶 信號和窄帶信號的下變頻由于信號帶寬不同而抽取因子不同,使得同時具有寬帶和窄帶信號的系統采用基于 FPGA 的系統很難實現。本文提出采用專用數字

2017-12-05 09:49:31 3044

3044

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字上下變頻的FPGA實現方法,以及Altera提供的一種數字信號處理的工具,DSP BUILDER。

2019-03-13 15:16:58 1743

1743

設計了采樣頻率為640 MHz、過采樣率為64的高頻數字抽取濾波器。該數字抽取濾波器由CIC(Cascaded Integrator Comb)濾波器(降16倍)、CIC補償濾波器

2018-02-21 12:08:00 1815

1815

文介紹了FIR抽取濾波器的工作原理,重點闡述了用XC2V1000實現FIR抽取濾波器的方法,并給出了仿真波形和設計特點。

2018-04-19 11:34:00 1846

1846

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2018-04-28 11:50:00 1073

1073

數字抽取濾波器是ΣΔADC(ΣΔAnolog-to-Digital Converter)的重要組成部為分,旨在從高速、低分辨率的調制信號中重構出高分辨率、奈奎斯特頻率的信號。為節約硬件資源,同時滿足

2018-06-29 14:32:00 11289

11289

∑-△調制器與數字抽取濾波器是∑-△ ADC 實現16bit 以上精度的關鍵電路模塊。∑-△調制器依靠過采樣與高階閉環負反饋控制實現的噪聲整形技術,將基帶內的量化噪聲搬移到高頻段,而數字抽取濾波器

2019-05-08 08:18:00 3969

3969

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字

2018-09-15 04:57:00 2800

2800 用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3 本文檔的主要內容詳細介紹的是使用FPGA實現數字下變頻器DDC的設計資料合集免費下載。

2020-08-10 17:27:46 26

26 針對Σ△ADC輸出端存在的高頻噪聲問題,設計了一種 Sinc數字抽取濾波器,實現了Σ-△調制器輸出信號的高頻濾波。分析了Sinc濾波器的結構原理,基于 Spartan6FPGA進行濾波器的設計與實現

2020-08-26 17:12:00 14

14 研究了高倍抽取的數字下變頻設計,重點分析了基于級聯積分梳狀濾波器和級聯半帶濾波器的多級抽樣頻率算法。并提出了用最新的Systemgenerator軟件實現FPGA 的設計、仿真方案,縮短了開發周期

2020-11-05 17:04:55 14

14 基于FPGA的DDC(數字下變頻)設計與實現(電源技術審稿費多少)-該文檔為基于FPGA的DDC(數字下變頻)設計與實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 12:04:22 28

28 基于FPGA的數字下變頻器(DDC)的設計(ups電源技術轉讓)-基于FPGA的數字下變頻器(DDC)的設計.適合新手學習參考

2021-09-16 11:43:52 37

37 基于FPGA的_ADC數字抽取濾波器Sinc_3設計(現代電源技術基礎楊飛)-該文檔為基于FPGA的_ADC數字抽取濾波器Sinc_3設計總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 13:58:04 20

20 積分梳狀濾波器(CIC,Cascaded Integrator Comb),一般用于數字下變頻(DDC)和數字上變頻(DUC)系統。

2023-06-01 11:05:41 1166

1166

回想一下示例中,AD9680-500的工作輸入時鐘為491.52 MHz,模擬輸入頻率為150.1 MHz。AD9680設置為使用數字下變頻器(DDC),具有實輸入、復數輸出、155 MHzNCO

2023-06-30 15:18:00 717

717

在本例中,我們將介紹AD9680-500,其工作輸入時鐘為491.52 MHz,模擬輸入頻率為150.1 MHz。AD9680將設置為使用數字下變頻器(DDC),具有實際輸入、復數輸出、155

2023-06-30 15:20:25 747

747

我們將再次以AD9680為例。在這種情況下,無論速度等級如何,歸一化抽取濾波器響應都是相同的。抽取濾波器響應僅隨采樣速率成比例。在此包含的示例濾波器響應圖中,沒有準確給出具體的插入損耗與頻率的關系

2023-06-30 15:43:41 1667

1667

我們將繼續以AD9680為例,就像在第1部分中所做的那樣。與DDC的實際模式操作類似,無論速度等級如何,歸一化抽取濾波器響應都是相同的。我想再次提到,對于此處包含的示例濾波器響應圖,沒有準確給出

2023-06-30 15:44:38 936

936

電子發燒友App

電子發燒友App

評論