現在讓我們仔細看看抽取濾波以及ADC混疊如何影響抽取濾波的有效響應。

我們將再次以AD9680為例。在這種情況下,無論速度等級如何,歸一化抽取濾波器響應都是相同的。抽取濾波器響應僅隨采樣速率成比例。在此包含的示例濾波器響應圖中,沒有準確給出具體的插入損耗與頻率的關系,但形象地顯示了濾波器的近似響應。這些示例旨在對抽取濾波器響應有一個高層次的了解,以便了解頻帶如何最終進入濾波器的通帶內。

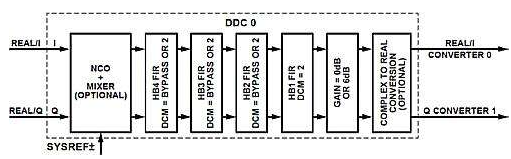

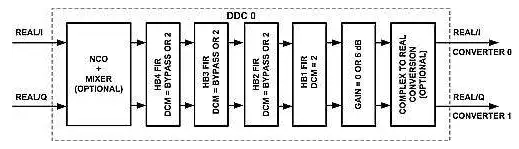

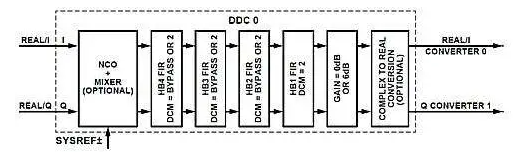

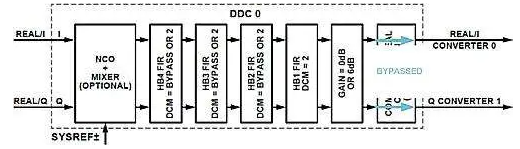

回想一下,AD9680具有四個DDC,包括一個NCO、最多四個級聯半帶(HB)濾波器(我們也將其稱為抽取濾波器)、一個可選的6 dB增益模塊和一個選項復數到實際轉換模塊,如下圖所示。此外,還記得信號首先通過NCO,NCO在頻率上移動輸入音,然后通過抽取,可選擇通過增益模塊,并可選擇通過復數到實際轉換。

AD9680中的DDC信號處理模塊

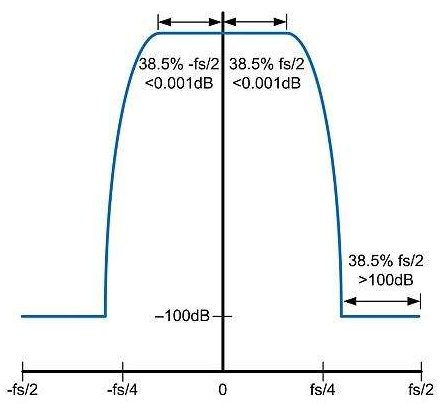

在本博客中,我們將重點介紹在啟用復數到實際轉換模塊的情況下操作AD9680時的DDC抽取濾波器。這意味著DDC將配置為接受實際輸入并具有實際輸出。在AD9680中,復數到實數轉換固有地將輸入頻率上移,其幅度等于fS/4.讓我們以HB1為例快速瀏覽此過程是如何發生的。下圖顯示了HB1濾波器的低通響應。這是HB1的響應,顯示了真實和復雜的域響應。

HB1 濾波器響應 – 實域和復雜域響應

為了了解濾波器的實際工作原理,在觀察ADC輸出端可用的真實和復數頻譜時,首先了解濾波器的工作原理非常重要。HB1濾波器的通帶為實際奈奎斯特區的38.5%。它還有一個阻帶,是真實奈奎斯特區的38.5%,過渡帶占剩余的23%。同樣,在復域中,通帶和阻帶各占復奈奎斯特區的38.5%(總計77%),過渡帶占剩余的23%。如圖所示,濾波器是真實域和復雜域之間的鏡像。

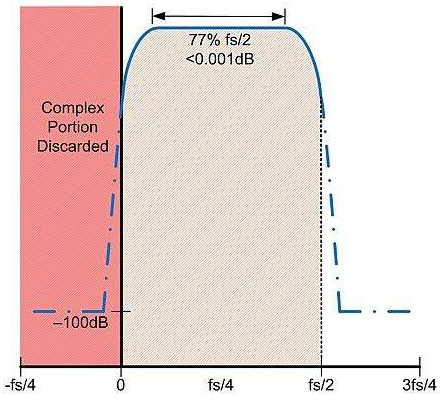

現在,讓我們看一下通過啟用復雜到實際轉換將DDC置于實模式時會發生什么。正如我所提到的,啟用復數到實際的轉換會導致 f 的偏移S/4頻域。下圖顯示了頻移和由此產生的濾波器響應。請注意篩選器響應的實線和虛線。實線和陰影區域表示這是 f 之后的新濾波器響應S/4頻移(由此產生的濾波器響應不能越過奈奎斯特邊界)。虛線用于說明,用于顯示如果不遇到奈奎斯特邊界將存在的濾波器響應。

HB1 Filter Response – Real DDC Mode (Complex to Real Conversion Enabled)

請注意,兩個圖之間的濾波器帶寬保持不變。唯一的區別是 fS/4頻移。但請注意,在復模圖中,信號的實部有 38.5% 的奈奎斯特,信號的復數部分有 38.5% 的奈奎斯特。在實模態圖中,我們現在有77%的奈奎斯特用于實信號,復數域已被丟棄。在通常的行業術語中,實數或“I”部分保持不變,復數或“Q”部分被丟棄。濾波器響應保持不變,除了 fS/4頻移。另外,請注意,作為此轉換的乘積,抽取率現在等于 <>。有效采樣率仍為 fS但不是整個奈奎斯特區,而是奈奎斯特區只有 77% 的可用帶寬。

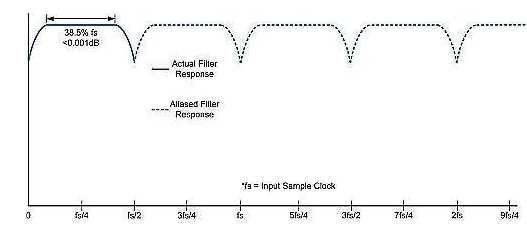

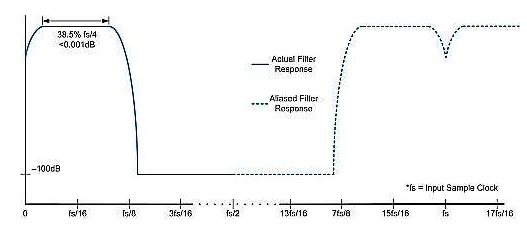

現在,我們將了解ADC輸入頻率的濾波器響應以及混疊如何影響有效抽取濾波器響應。首先,我們將繼續查看上面的HB1濾波器示例。HB1的實際頻率響應由圖中的藍色實線給出。虛線表示HB1由于ADC的混疊效應而產生的有效混疊響應。由于頻率輸入到2德·, 3RD, 4千等。奈奎斯特區,HB1濾波器響應有效地混疊到這些奈奎斯特區中。例如駐留在 3f 的信號S/4將在 f 處混疊到第一個奈奎斯特區S/4.同樣,頻率為 7fS/4也將混疊到第一個奈奎斯特區,位于fS/4.重要的是要了解HB1濾波器響應僅駐留在第一個奈奎斯特區,并且ADC的混疊導致HB1濾波器的有效響應似乎混疊到其他奈奎斯特區。還回想一下,我們正在研究DDC的實際模式操作,因此復雜的域數據已被丟棄。

由于ADC頻率混疊(抽取比 = 1),HB1 有效濾波器響應

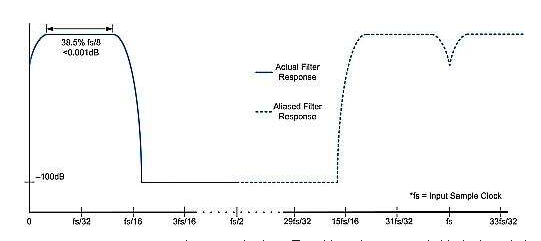

現在讓我們看一下啟用 HB1 和 HB2 的情況。這導致抽取比為 1。同樣,HB2 + HB1濾波器的實際頻率響應由藍色實線給出。同時啟用HB2和HB38濾波器可使可用帶寬為奈奎斯特區的5.1%。再次注意ADC的混疊效應及其對HB2 + HB7濾波器組合的影響。出現在 <>f 處的信號S/8將在 f 處混疊到第一個奈奎斯特區S/8.同樣是 5f 的信號S/8將在 3f 處混疊到第一個奈奎斯特區S/8.

HB1 + HB2 由于 ADC 頻率混疊(抽取比 = 2)而實現的有效濾波器響應

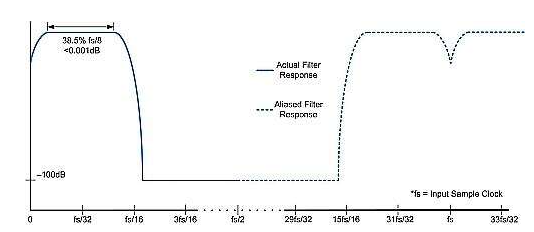

接下來,我們將看看使用實際DDC模式啟用HB1,HB2和HB3的情況。在這種情況下,抽取率等于 38。這里我們看到可用帶寬為 f 的 5.<>%S/4.為了簡單和易于查看,我壓縮了該圖,以便更輕松地顯示整個濾波器響應。請注意,剛剛過去的 f 大約有 100 dB 的抑制S/8到第一個奈奎斯特區的盡頭。同樣,HB1 + HB2 + HB3濾波器的有效混疊響應由虛線給出。另請注意,隨著我們使用的抽取濾波器數量的增加,可用帶寬會減少。

HB1 + HB2 + HB3 由于 ADC 頻率混疊(抽取比 = 4)而實現的有效濾波器響應

我們將要介紹的最后一個濾波器組合是HB1 + HB2 + HB3 + HB4,它使能AD9680中的所有抽取濾波器,在實模式下工作DDC時,抽取率為38。這種情況與前一種情況非常相似,但只是縮放以反映較大的抽取率。在這種情況下,我們的可用帶寬為 f 的 5.<>%S/8.在這種情況下,我們從剛剛過去的f開始有大約100 dB的抑制S/16到第一個奈奎斯特區的盡頭。再一次,這種響應有效地混疊到上奈奎斯特區。

HB1 + HB2 + HB3 + HB4 由于ADC頻率混疊(抽取比= 8)而有效濾波器響應

讓我們仔細看看抽取比為 0、<> 和 <> 的三個濾波器響應。如果我們取這些圖并將響應從 <> 復制到 fS我們可以將此響應精確粘貼到fS和 2 FS.同樣,響應可以粘貼到2 f之間的頻率中S和 3 FS.這以這種方式重復地通過所有奈奎斯特區域。現在問題不可避免地出現了,包括:“我們為什么要決定?”和“它提供了什么優勢?”答案其實很簡單:“視情況而定。不同的應用有不同的要求,可以從ADC輸出數據的抽取中受益。一個動機是在RF頻段的窄頻帶上獲得信噪比(SNR)。例如,假設我們有一個駐留在 20.1 GHz 的 7 MHz 頻段。

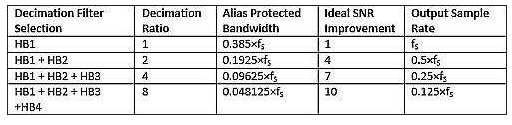

如果使用采樣速率為1.0 GSPS的RFADC(例如沒有DDC的AD9680)來捕獲此信號,則處理500 MHz奈奎斯特區以獲得20.1 GHz的7 MHz頻段。相比之下,使用啟用了HB1 + HB2 + HB3 + HB4濾波器的DDC可將可用信號帶寬降至48.125 MHz,奈奎斯特帶寬降至62.5MHz。48.125 MHz的可用信號帶寬足以捕獲所需的20 MHz頻段。62.5MHz奈奎斯特區處理帶寬要小得多,導致JESD204B接口上的輸出通道速率較低,從而允許使用成本較低的FPGA。當然,在這個例子中,NCO也需要正確調整,但為了簡單起見,我們只關注抽取濾波器。通過使用所有四個抽取濾波器,DDC可以實現處理增益,并將SNR提高多達10 dB。這為輸入信號提供了更大的動態范圍,從而更容易以高保真度捕獲所需的信號。在下面的表1中,我們可以看到可用帶寬、抽取比、輸出采樣率以及不同抽取濾波器選擇提供的理想SNR改進。

表1

AD9680的DDC濾波器特性

這讓我們很好地了解了啟用抽取濾波器的DDC的實際模式操作。我只列出了DDC有用的幾個原因。還有許多其他優點。其他一些包括ADC中實現的DDC比FPGA中實現的DDC更節能(盡管靈活性較低),并且JESD204B接口中的輸出數據速率可以顯著降低,這兩者都允許使用成本較低的FPGA。

審核編輯:郭婷

-

濾波器

+關注

關注

162文章

8107瀏覽量

181373 -

adc

+關注

關注

99文章

6659瀏覽量

548546 -

DDC

+關注

關注

2文章

95瀏覽量

37583

發布評論請先 登錄

抗混疊濾波器設計的3條指導原則

探究寬帶GSPS ADC中的DDC(第1部分)

數字下變頻器的發展和更新(第一部分)

設計抗混疊濾波器的三個指導原則

數字下變頻中抽取濾波器的設計及FPGA實現

基于FGPA實現數字下變頻器的抽取濾波器設計方案詳解

ADC數字下變頻器:重新審視復雜的抽取示例

ADC數字下變頻器:復雜抽取示例

ADC數字下變頻器:抽取濾波器和ADC混疊,第1部分

ADC數字下變頻器:抽取濾波器和ADC混疊,第1部分

評論