在第一部分中,我們開始研究當(dāng)復(fù)數(shù)到實(shí)際轉(zhuǎn)換使能且輸出數(shù)據(jù)僅為實(shí)數(shù)時DDC中的抽取濾波。現(xiàn)在我們將看看當(dāng)我們將DDC置于復(fù)雜模式并且輸出數(shù)據(jù)很復(fù)雜(I和Q)時會發(fā)生什么。

我們將繼續(xù)以AD9680為例,就像在第1部分中所做的那樣。與DDC的實(shí)際模式操作類似,無論速度等級如何,歸一化抽取濾波器響應(yīng)都是相同的。我想再次提到,對于此處包含的示例濾波器響應(yīng)圖,沒有準(zhǔn)確給出具體的插入損耗與頻率的關(guān)系,而是形象地顯示以說明濾波器的近似響應(yīng)。這有助于全面了解濾波器響應(yīng)如何受到ADC混疊的影響。

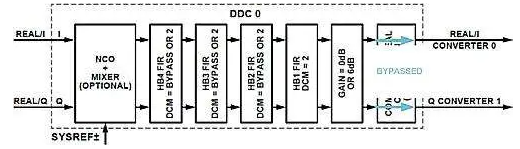

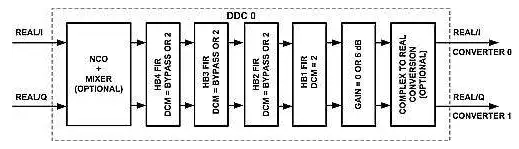

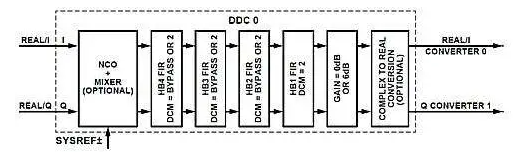

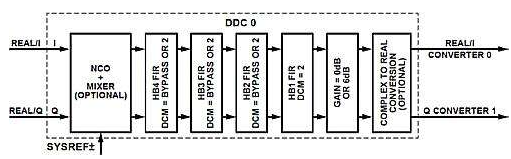

讓我們再次看一下AD9680中的DDC模塊,它由一個NCO、最多四個級聯(lián)半帶(HB)濾波器(我們也稱之為抽取濾波器)、一個可選的6 dB增益模塊和一個選項復(fù)數(shù)到實(shí)際轉(zhuǎn)換模塊組成,如下圖所示。回想一下,AD9680具有四個這樣的DDC模塊。對于此處提供的示例,將繞過(禁用)復(fù)雜到實(shí)際的轉(zhuǎn)換塊。回顧一下,來自ADC的信號首先通過NCO,NCO在頻率上移動輸入音,然后通過抽取濾波器,可選擇通過增益模塊,如果啟用,則通過復(fù)數(shù)到實(shí)數(shù)轉(zhuǎn)換(同樣,本博客中的示例將繞過該模塊)。

AD9680中的DDC信號處理模塊

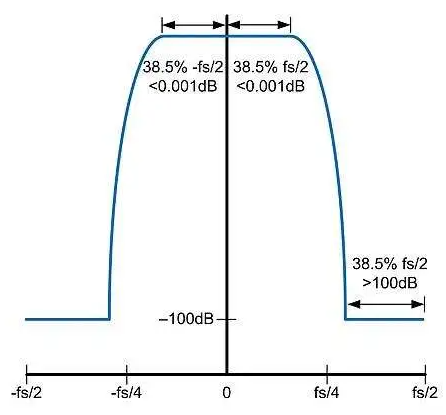

當(dāng)DDC處于復(fù)數(shù)模式時,它被配置為具有復(fù)數(shù)輸出,該輸出由實(shí)頻域和復(fù)頻域組成,通常稱為I和Q.回顧第1部分HB1濾波器的低通響應(yīng)(如下圖所示)。HB1濾波器的通帶為實(shí)際奈奎斯特區(qū)的38.5%。它還有一個阻帶,是真實(shí)奈奎斯特區(qū)的38.5%,過渡帶占剩余的23%。同樣,在復(fù)域中,通帶和阻帶各占復(fù)奈奎斯特區(qū)的38.5%(總計77%),過渡帶占剩余的23%。

HB1 濾波器響應(yīng) – 實(shí)域和復(fù)雜域響應(yīng)

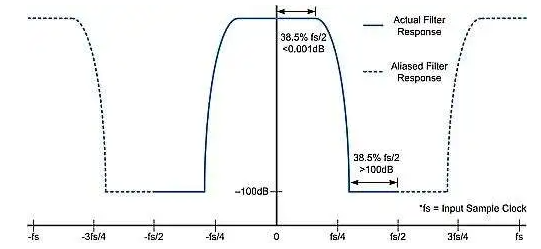

讓我們繼續(xù)查看 HB1 篩選器并查看混疊響應(yīng)。在復(fù)數(shù)輸出模式下操作DDC并啟用HB1濾波器時,抽取比等于38,輸出采樣速率是輸入采樣時鐘的一半。濾波器的通帶包括 f 的 5.<>%SI(真實(shí))數(shù)據(jù)和 2.38% f 的 /5S/2 Q(復(fù)雜)數(shù)據(jù)。藍(lán)色實(shí)線表示實(shí)際濾波器響應(yīng),藍(lán)色虛線表示濾波器由于ADC的混疊效應(yīng)而產(chǎn)生的有效混疊響應(yīng)。7 f 時的輸入信號S/8 將在 f 處混疊到第一個奈奎斯特區(qū)S/8將其置于HB1濾波器的通帶中。同一信號的復(fù)雜圖像位于–7 f處S/8并將在復(fù)雜域中別名為 – fS/8將其放置在復(fù)域中HB1濾波器的通帶中。

由于ADC頻率混疊(抽取比= 1)引起的HB2有效濾波器響應(yīng) – 復(fù)數(shù)

現(xiàn)在讓我們看一下啟用 HB1 和 HB2 的情況。這導(dǎo)致每個I和Q輸出的抽取比為1。同樣,HB2 + HB1濾波器的實(shí)際頻率響應(yīng)由藍(lán)色實(shí)線給出。同時啟用HB2和HB38濾波器會導(dǎo)致每個實(shí)域和復(fù)域中抽取奈奎斯特區(qū)的可用帶寬為5.38%(f的5.<>%S/4其中 fS是輸入采樣時鐘)。再次注意ADC的混疊效應(yīng)及其對HB1 + HB2濾波器組合的影響。在 15 f 處出現(xiàn)的信號S/16 將在 f 處混疊到第一個奈奎斯特區(qū)S/16.該信號在–15 f處具有復(fù)雜的圖像S/16在復(fù)域中,并將混疊到復(fù)域中的第一個奈奎斯特區(qū) – fS/16.

HB1 + HB2 由于 ADC 頻率混疊(抽取比 = 4)而實(shí)現(xiàn)的有效濾波器響應(yīng) – 復(fù)數(shù)

現(xiàn)在,讓我們啟用 HB1、HB2 和 HB3 篩選器,并在復(fù)雜的 DDC 模式下觀察結(jié)果。在這種情況下,抽取率等于 38。這里我們看到可用帶寬為 f 的 5.<>%S/8在每個復(fù)雜領(lǐng)域和真實(shí)領(lǐng)域。為了簡單和易于查看,我壓縮了該圖,以便更輕松地顯示整個濾波器響應(yīng)。與前兩張圖一樣,HB1 + HB2 + HB3濾波器的有效混疊響應(yīng)由藍(lán)色虛線給出,而藍(lán)色實(shí)線表示實(shí)際濾波器響應(yīng)。另請注意,隨著我們使用的抽取濾波器數(shù)量的增加,可用帶寬會減少。然而,抽取濾波的一個好處是處理增益在ADC的信噪比(SNR)中看到。除HB1外,每個啟用抽取濾波器的SNR都會提高約3 dB(僅HB1將SNR提高約1 dB)。

HB1 + HB2 + HB3 由于 ADC 頻率混疊(抽取比 = 8)而實(shí)現(xiàn)的有效濾波器響應(yīng) – 復(fù)數(shù)

我們將要介紹的最后一個濾波器組合是HB1 + HB2 + HB3 + HB4,它使能AD9680中的所有抽取濾波器,在復(fù)數(shù)模式下操作DDC時,抽取比為38。這種情況與前一種情況非常相似,但只是縮放以反映較大的抽取率。在這種情況下,我們的可用帶寬為 f 的 5.<>%S/8每個真實(shí)域和復(fù)雜域。啟用所有四個半帶抽取濾波器后,我們從剛剛過去的f開始有大約100 dB的抑制S/16到第一個奈奎斯特區(qū)的盡頭。再一次,這種響應(yīng)有效地混疊到上奈奎斯特區(qū)。

HB1 + HB2 + HB3 + HB4 由于 ADC 頻率混疊(抽取比 = 16)而實(shí)現(xiàn)的有效濾波器響應(yīng) – 復(fù)數(shù)

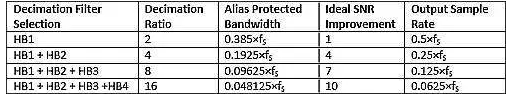

上次我們看了以下問題:“我們?yōu)槭裁匆x擇?”和“它有什么優(yōu)勢?”正如我們在本博客的第一部分中了解到的,不同的應(yīng)用有不同的要求,可以從ADC輸出數(shù)據(jù)的抽取中受益。一個動機(jī)是在RF頻段的窄頻帶上獲得信噪比(SNR)。我們研究的另一個原因是,需要處理的帶寬較少,導(dǎo)致JESD204B接口上的輸出通道速率較低,從而允許使用成本較低的FPGA。通過使用所有四個抽取濾波器,DDC可以實(shí)現(xiàn)處理增益,并將SNR提高多達(dá)10 dB。在下面的表1中,我們可以看到可用帶寬、抽取比、輸出采樣率,以及在復(fù)數(shù)模式下操作DDC時,不同抽取濾波器選擇所提供的理想SNR改進(jìn)。

表1

AD9680的DDC濾波器特性 – 復(fù)數(shù)

現(xiàn)在,我們對AD9680中DDC的實(shí)際和復(fù)雜工作模式有了很好的了解。我們可以看到抽取濾波的優(yōu)勢。此外,我們還可以了解DDC的靈活性。DDC可以在實(shí)模式或復(fù)雜模式下工作,并允許用戶根據(jù)特定應(yīng)用的需要使用不同的接收器拓?fù)洹?/p>

審核編輯:郭婷

-

濾波器

+關(guān)注

關(guān)注

162文章

8003瀏覽量

180383 -

adc

+關(guān)注

關(guān)注

99文章

6608瀏覽量

547647 -

DDC

+關(guān)注

關(guān)注

2文章

94瀏覽量

37475

發(fā)布評論請先 登錄

相關(guān)推薦

Σ-Δ ADC數(shù)字濾波器類型

抗混疊濾波器設(shè)計的3條指導(dǎo)原則

數(shù)字下變頻器的發(fā)展和更新第二部分

數(shù)字下變頻器的發(fā)展和更新(第一部分)

ADC的過采樣與抗混疊濾波器

設(shè)計抗混疊濾波器的三個指導(dǎo)原則

數(shù)字下變頻中抽取濾波器的設(shè)計及FPGA實(shí)現(xiàn)

基于FGPA實(shí)現(xiàn)數(shù)字下變頻器的抽取濾波器設(shè)計方案詳解

基于FPGA的_ADC數(shù)字抽取濾波器Sinc_3設(shè)計

ADC數(shù)字下變頻器:重新審視復(fù)雜的抽取示例

ADC數(shù)字下變頻器:復(fù)雜抽取示例

ADC數(shù)字下變頻器:抽取濾波器和ADC混疊,第1部分

ADC數(shù)字下變頻器:抽取濾波器和ADC混疊,第2部分

ADC數(shù)字下變頻器:抽取濾波器和ADC混疊,第2部分

評論