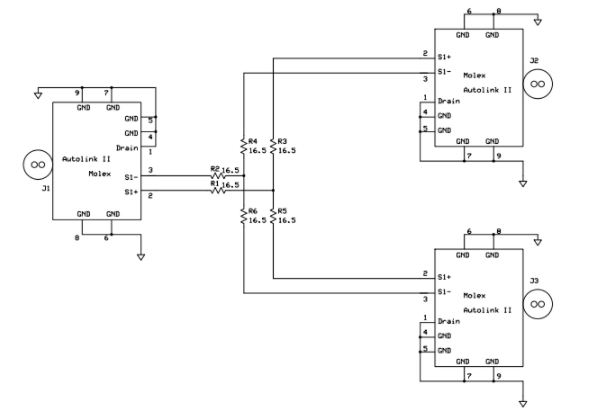

在某些應(yīng)用程序中,單個(gè)數(shù)據(jù)源需要將LVDS數(shù)據(jù)發(fā)送到兩個(gè)目的地。一個(gè)示例是單個(gè)視頻源,它將數(shù)據(jù)發(fā)送到兩個(gè)LCD面板,就像在汽車后座娛樂系統(tǒng)中可能會(huì)看到的那樣。傳統(tǒng)上,SERDES鏈路是點(diǎn)對點(diǎn)的單個(gè)發(fā)送器,通過電纜或電路板將串行數(shù)據(jù)發(fā)送到單個(gè)接收器。如果系統(tǒng)要求將相同的數(shù)據(jù)發(fā)送到兩個(gè)目的地,則需要兩個(gè)完整的鏈接(4個(gè)SERDES芯片和2條電纜)。圖1中顯示了一個(gè)示例。為方便顯示圖片,將顯示器靠近在一起顯示,但在最終應(yīng)用中,顯示器之間可能相距一米或更多。

提出一種允許系統(tǒng)設(shè)計(jì)人員拆分LVDS電纜的技術(shù),以便單個(gè)ISL76341或ISL76321發(fā)送器可以驅(qū)動(dòng)兩個(gè)接收器。這樣可以從BOM中省去一個(gè)SERDES芯片,并縮短了系統(tǒng)中的電纜總長度。在整個(gè)數(shù)據(jù)路徑中保持100Ω差分阻抗環(huán)境對于消除反射和維持共模電壓至關(guān)重要。由于這是降低成本的標(biāo)準(zhǔn)電路板,因此必須采用設(shè)計(jì)技術(shù)。

分離器設(shè)計(jì)

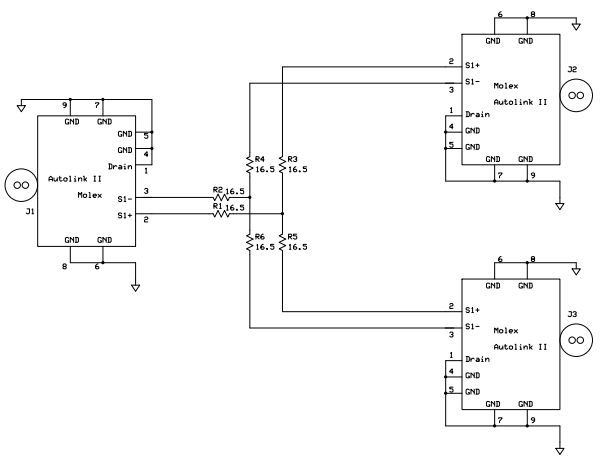

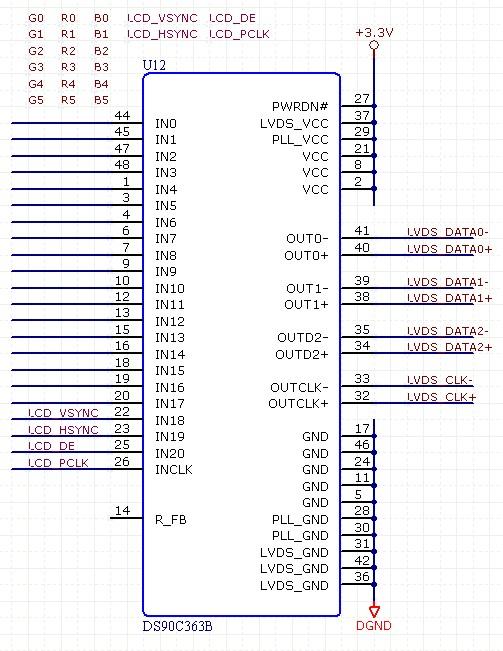

為了實(shí)現(xiàn)這些目標(biāo),需要將單個(gè)板添加到系統(tǒng)中,以將LVDS信號(hào)分成兩個(gè)相同的信號(hào)。雖然預(yù)計(jì)會(huì)有一些信號(hào)損失,但我們希望將其降至最低。必須保持信號(hào)完整性,以免增加EMI。隔板的原理圖如圖2所示。

圖2 LVDS分離器原理圖

每個(gè)發(fā)射器和接收器的阻抗均為100。分析上部分支時(shí),我們從該100Ω開始。當(dāng)我們將R3和R4相加時(shí),該分支的阻抗為133Ω。并聯(lián)的兩個(gè)接收器分支的阻抗為66.5Ω。最后,從發(fā)射器輸出看,我們將來自發(fā)射支路R1和R2的兩個(gè)串聯(lián)電阻的33Ω相加,總計(jì)為99.5Ω。每個(gè)分支的分析都相同,因此每個(gè)SERDES芯片承受100Ω負(fù)載。六個(gè)16.5Ω電阻是標(biāo)準(zhǔn)的1%SMT值。這些電阻流過的電流很小,因此可以使用任何尺寸的SMT電阻。

電路板設(shè)計(jì)

分離器可以以2層或4層板設(shè)計(jì)實(shí)現(xiàn)。關(guān)鍵在于維持50Ω單端和100Ω差分傳輸線環(huán)境。造成這一挑戰(zhàn)的原因是,由于信號(hào)需要交叉,因此至少有一對需要從電路板的頂層到底層。對于4層板,通過將內(nèi)部層用作參考平面(GND)并將頂層和底層用作信號(hào),可以更輕松地保持阻抗控制。信號(hào)路徑中所需的過孔只會(huì)增加少量電感,而特性阻抗的變化可忽略不計(jì)。

編輯:hfy

-

接收器

+關(guān)注

關(guān)注

14文章

2529瀏覽量

73056 -

分離器

+關(guān)注

關(guān)注

1文章

82瀏覽量

15295 -

發(fā)射器

+關(guān)注

關(guān)注

6文章

863瀏覽量

54046 -

lvds

+關(guān)注

關(guān)注

2文章

1076瀏覽量

66859

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA編程LVDS信號(hào)圖像處理技術(shù)

功率分裂器

什么是lvds信號(hào)

LVDS信號(hào)電平特性

LVDS信號(hào)的PCB設(shè)計(jì)

LVDS技術(shù)原理和設(shè)計(jì)簡介

電感分裂式推挽換向軟開關(guān)技術(shù)的研究

LVDS信號(hào)的PCB設(shè)計(jì)和仿真分析

淺談分離LVDS信號(hào)設(shè)計(jì)技術(shù)

LVDS信號(hào)的信號(hào)傳輸

LVDS傳輸?shù)氖鞘裁?b class='flag-5'>信號(hào)?判斷LVDS信號(hào)正常的方法

什么叫做LVDS信號(hào)?請問TTL信號(hào)與LVDS信號(hào)有什么區(qū)別?

LVDS中的時(shí)鐘脈沖信號(hào)是干什么的?

【電磁兼容技術(shù)案例分享】LVDS信號(hào)因經(jīng)連接器轉(zhuǎn)接導(dǎo)致RS問題整改分析案例

淺談分裂LVDS信號(hào)設(shè)計(jì)技術(shù)

淺談分裂LVDS信號(hào)設(shè)計(jì)技術(shù)

評論