時序就是為了維持數據信號與其參考時鐘信號之間的相對位置,保證在時鐘上升沿或者下降沿附近的數據能夠維持穩定,這樣數據就能被有效的讀取。怎么讓這些時序關系在系統運行中有效的實現呢?PCB設計中,是通過定義時序參數來實現的,下面就來看看這些時序參數的具體含義。

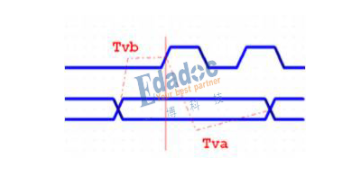

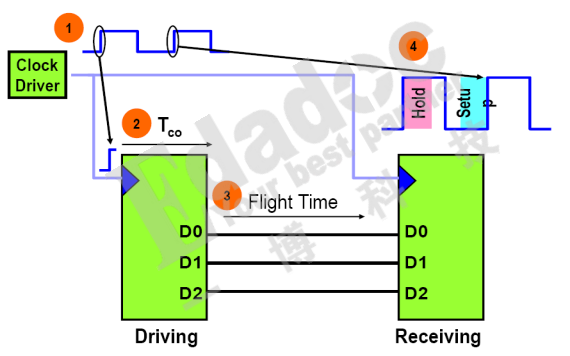

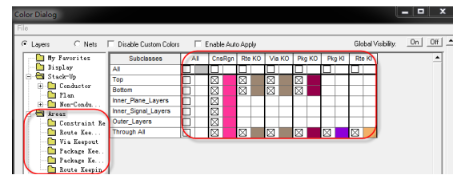

這里作者按照自己的理解把時序參數分成了三類,一類是用來描述驅動端的,一類是用來描述接收端的,還有一類是用來描述傳輸通道的。對于驅動端,描述它的時序參數是Tco,Tco是指時鐘觸發開始到有效數據輸出的器件內部所有延時的總和。這個參數描述了最開始信號從芯片出來的時候,時鐘與數據之間的一個位置關系。對于源同步時序,不是直接用Tco來定義的,而是使用Tvb和Tva,如下圖1

圖1

圖1中,Tvb指的是在驅動端,時鐘上升沿之前(before)數據的有效時間;Tva指的是時鐘上升沿之后,數據的有效時間。這些參數在驅動芯片手冊上可以查到。

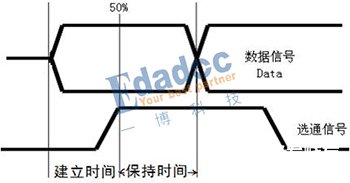

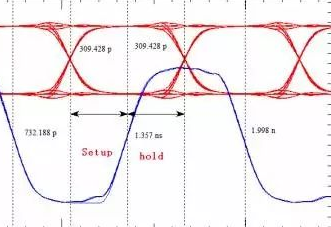

對于接收端,主要是建立時間和保持時間,這兩個時序參數是時序分析中提到最多的兩個參數,如下圖2所示:

圖2

看圖2,有沒有覺得和圖1很相似呢,它們都是以時鐘信號為參考。對于接收端來說,數據在時鐘信號上升沿之前的有效時間稱為建立時間,在時鐘上升沿之后的叫保持時間。和驅動端對比,它們的叫法不一樣罷了,定義方式都是相似的。時序分析的最終目的就是要保證數據被接收端有效的讀取,所以我們在評估一個系統的時序是否滿足要求,是通過評估建立時間和保持時間的裕量來實現的。

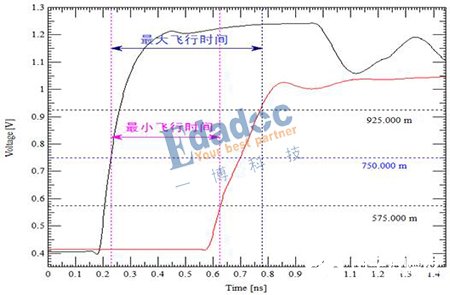

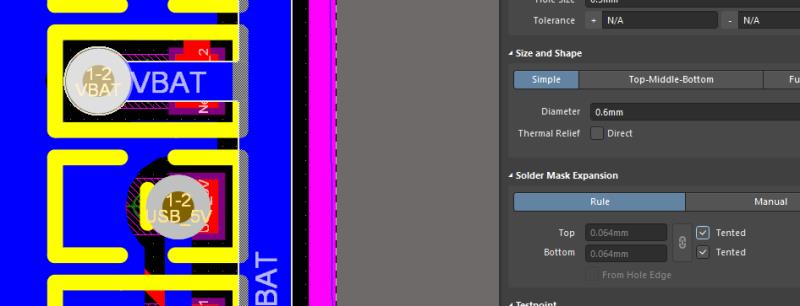

對于傳輸通道來說,是通過飛行時間來描述的。飛行時間包括最大飛行時間和最小飛行時間。最大最小飛行時間和傳輸線的長度有關,也和負載的輕重有關,負載較重會導致上升時間變緩,定義方式如下圖3

在理解這些時序參數的含義之后,就可以進行時序裕量的計算了。這里以數據信號為例進行說明,我們知道,DDR總線中,數據信號是參考DQS的,在寫方向:

Data信號從驅動到接收總的延時為:Tdata=Tco_data+Tflt_data (1)

DQS信號從驅動到接收總的延時為:Tstrobe=Tco_strobe+Tflt_strobe+Tdelay (2)

式中:Tco和Tflt分別代表數據、選通信號在器件的內部延遲和信號傳輸的飛行時間;Tdelay是指數據信號和選通信號之間的延遲,由系統內延時器件決定。建立時序裕量的公式為:Tsetup_margin=Tstrobe-Tdata-Tsetup(3)

把式(1)和式(2)帶入得式(3)得:

Tsetup_margin=Tco_strobe+Tflt_strobe+Tdelay- (Tco_data+Tflt_data)-Tsetup(4)

式中:Tsetup表示接收數據端數據的建立時間,從器件手冊上獲取;將數據和Strobe信號在器件內的延時差異定義為Tvb,其值從器件手冊上獲取;

Tvb=Tco_strobe+Tdelay-Tco_data (5)將PCB走線引起的延時差異,定義為Tpcb_skew:Tpcb_skew= Tflt_data- Tflt_strobe(6)將式(5)和式(6)帶入式(4),這樣可以得到一個簡單的建立時間裕量方程:

Tsetup_margin=Tvb-Tsetup- (Tflt_data(max)-Tflt_strobe(min))(7)

使用同樣的方法分析,保持時間裕量:

Thold_margin=(Tco_strobe+Tflt_strobe+Tdelay)-(Tco_data+Tflt_data)-Thold(9)

同樣定義:

Tva=Tco_strobe+Tdelay-Tco_data(10)

Tpcb_skew=Tflt_data-Tflt_strobe(11)

Thold_margin=Tva-Thold+(Tflt_data(min)-Tflt_strobe(max))(12)

綜上所述,我們可以看出,對于DDR的時序來說,影響時序裕量的關鍵因素是驅動芯片的Tva與Tvb,以及接收端的建立時間與保持時間。我們布線可以控制的只是數據與選通時鐘之間的長度差值。數據線與數據選通線長度的差值有正負之分,從(7)和(9)式可以看出,建立時間很保持時間與Tpcb_skew之間的關系,在增大建立時間的時候必然會犧牲保持時間。所以在布線的時候,數據與數據選通即DQ與同組的DQS之間應該保持嚴格的等長,這樣可以減少Tpcb_skew,增大建立時間裕量。

時序問題是很復雜的,文中分析的情況沒有考慮Jitter與串擾。我們也很少會手動計算一個系統的時序關系,一般會借助軟件分析。

編輯:hfy

-

PCB設計

+關注

關注

396文章

4789瀏覽量

89490 -

Data

+關注

關注

0文章

63瀏覽量

38655

發布評論請先 登錄

【PCB設計】PCB設計中的過孔分析

應對高速PCB設計的時序問題

PCB中TOP PASTE和TOP SOLDER的區別_PCB層的含義詳解

PCB設計有哪些誤區PCB設計的十大誤區下部分內有上部分鏈接

PCB設計中的EMC/EMI問題分析

DDR布線在PCB設計中的應用解析

pcb設計中各種不同區域的設計

PCB設計中時序參數的具體含義

PCB設計中時序參數的具體含義

評論