多倫多—有時問題可以變成它自己的解決方案。

對于CEA-Leti科學(xué)家而言,這意味著先前被視為“非理想”的電阻性RAM(ReRAM)器件的特性可能是克服開發(fā)基于ReRAM的邊緣學(xué)習(xí)系統(tǒng)的障礙的答案,自然電子公司最近的出版物題為“通過馬爾可夫鏈蒙特卡洛采樣利用內(nèi)在憶阻器可變性進(jìn)行原位學(xué)習(xí)”。它描述了如何使用RRAM或憶阻器技術(shù)來創(chuàng)建智能系統(tǒng),該系統(tǒng)在邊緣獨(dú)立于云進(jìn)行本地學(xué)習(xí)。

托馬斯·達(dá)爾加蒂

法國格勒諾布爾大學(xué)(CEA-Leti)的CEA-Leti科學(xué)家Thomas Dalgaty解釋說,該團(tuán)隊(duì)如何能夠解決ReRAM技術(shù)固有的非理想性-當(dāng)前基于ReRAM的邊緣方法中使用的學(xué)習(xí)算法無法與設(shè)備編程的隨機(jī)性相協(xié)調(diào),或者可變性等。在EE Times的電話采訪中,他說解決方案是在制造好的芯片中實(shí)施馬爾可夫鏈蒙特卡洛(MCMC)采樣學(xué)習(xí)算法,該芯片充當(dāng)貝葉斯機(jī)器學(xué)習(xí)模型,該模型積極利用憶阻器隨機(jī)性。

出于研究目的,Dalgaty說,清楚定義邊緣系統(tǒng)的含義很重要。它不僅不可能連接到具有大內(nèi)存和標(biāo)記數(shù)據(jù)的基本云計算資源,而且它的系統(tǒng)并未真正連接到大能源。他說,這很重要,因?yàn)樵谶吘壥褂肦eRAM的吸引力之一是存儲器的低功耗。“在邊緣,您必須擁有許多未標(biāo)記的數(shù)據(jù),以便在本地了解自己的情況。”

Dalgaty說,機(jī)器學(xué)習(xí)模型通常使用基于von Neumann架構(gòu)的通用硬件進(jìn)行訓(xùn)練,該架構(gòu)不太適合邊緣學(xué)習(xí),因?yàn)檫吘墝W(xué)習(xí)系統(tǒng)是分布式,受能量限制和受內(nèi)存限制的系統(tǒng)。“ ReRAM對這類系統(tǒng)很有趣的原因是,一旦您開始使用設(shè)備的模擬屬性進(jìn)行計算,就不必關(guān)心所謂的馮·諾依曼存儲區(qū)中的自存儲信息并將其傳輸?shù)教幚磉^程中了。中心。”

他說,盡管有很大的潛力可以減少這些邊緣系統(tǒng)中使用的能源,但ReRAM器件對于實(shí)現(xiàn)標(biāo)準(zhǔn)的機(jī)器學(xué)習(xí)算法而言過于隨機(jī)。憶阻器可變性意味著您不能對學(xué)習(xí)模型的參數(shù)進(jìn)行特定更改,而這種可變性是需要克服的。

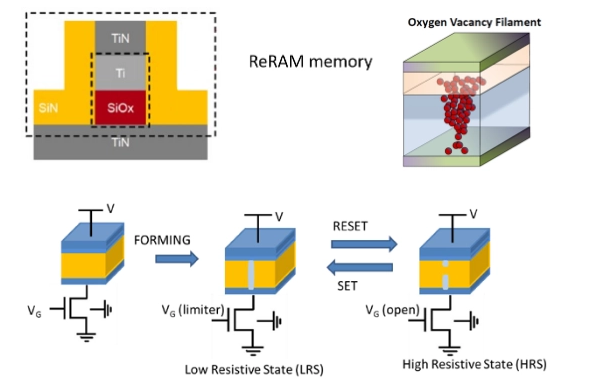

CEA-Leti研究人員在制造的芯片中實(shí)施了馬爾可夫鏈蒙特卡洛(MCMC)算法,以積極利用憶阻器隨機(jī)性ReRAM進(jìn)行邊緣學(xué)習(xí)系統(tǒng)的使用。(由CEA-Leti提供)

Dalgaty說,研究人員一直在撞墻,試圖減輕憶阻器的可變性以利用ReRAM器件的效率,然后意識到答案是使用憶阻器可變性而不是試圖與之對抗。隨機(jī)變異性。在制造的芯片中實(shí)施MCMC采樣學(xué)習(xí)算法可減輕隨機(jī)性,而無需任何能源密集型技術(shù)。

他說,通過利用隨機(jī)性而不是防止隨機(jī)性,可以通過將納秒級的電壓脈沖應(yīng)用于納米級ReRAM存儲設(shè)備來實(shí)現(xiàn)高效的原位機(jī)器學(xué)習(xí)。實(shí)際上,與該算法的標(biāo)準(zhǔn)CMOS實(shí)施相比,該方法所需的能源要少五個數(shù)量級(研究團(tuán)隊(duì)采用了與CMOS兼容的二氧化ha技術(shù))。Dalgaty說,這類邊緣計算系統(tǒng)的真實(shí)例子可以是植入式醫(yī)療系統(tǒng),該系統(tǒng)可以根據(jù)患者的發(fā)展?fàn)顩r在本地更新其操作。該研究小組已經(jīng)通過實(shí)驗(yàn)將其基于ReRAM的MCMC應(yīng)用于訓(xùn)練多層貝葉斯神經(jīng)網(wǎng)絡(luò),以從心電圖記錄中檢測出心律不齊,

他說,這是一個正在研究的應(yīng)用程序的例子,但是與所有這種性質(zhì)的研究一樣,在此方法要在現(xiàn)實(shí)世界中找到商業(yè)應(yīng)用程序之前,還有許多工作要做,并且尚不清楚所有這些內(nèi)容是什么。他們可能是。最終,希望是它可以使機(jī)器學(xué)習(xí)處于盡頭,而無需當(dāng)前所需的大量能量和內(nèi)存。

ReRAM被認(rèn)為是人工智能(AI)和機(jī)器學(xué)習(xí)應(yīng)用的良好候選者,并且具有模仿人腦如何在神經(jīng)元和突觸級學(xué)習(xí)和處理信息的潛力。擴(kuò)展神經(jīng)形態(tài)架構(gòu)被認(rèn)為將從ReRAM設(shè)備中受益,因?yàn)樗鼈儽仁褂?a href="http://m.xsypw.cn/tags/dram/" target="_blank">DRAM,閃存甚至是高帶寬內(nèi)存(HBM)的當(dāng)前AI數(shù)據(jù)中心要小得多,并且能效更高。

ReRAM的制造商,例如Weebit Nano,已經(jīng)通過最近的研究合作關(guān)系投入了時間和資源,其中包括與德里印度理工學(xué)院(IITD)的非易失性存儲器小組合作進(jìn)行的一項(xiàng)合作研究項(xiàng)目,該項(xiàng)目將采用Weebit的氧化硅(SiOx)ReRAM技術(shù)用于AI的計算機(jī)芯片。最近,米蘭理工大學(xué)(米蘭理工大學(xué))的研究人員在與該公司的論文中進(jìn)行了聯(lián)合研究,該研究詳細(xì)介紹了基于Weebit的SiOx ReRAM的新型AI自學(xué)演示,概述了靈感來自大腦的AI系統(tǒng)如何在不受監(jiān)督的情況下執(zhí)行以高精度結(jié)果學(xué)習(xí)任務(wù)。

Weebit的ReRAM單元由兩層金屬層和一層氧化硅(SiOx)層組成,這兩層之間的材料可用于現(xiàn)有生產(chǎn)線中,從而使其成為AI和機(jī)器學(xué)習(xí)架構(gòu)的潛在成本效益,低功耗選擇(Courtesy Weebit Nano )。

Weebit Nano已經(jīng)與CEA-Leti建立了長期合作伙伴關(guān)系,以開發(fā)其ReRAM技術(shù),但是與嵌入式ReRAM計劃相比,其對神經(jīng)形態(tài)應(yīng)用的研究工作的優(yōu)先級較低,這對推動公司收入至關(guān)重要,并且其重點(diǎn)是響應(yīng)客戶對分立的ReRAM存儲器組件的需求。但是,它并不是唯一一家對AI機(jī)會感興趣的ReRAM制造商-在2019年,一個由SCAiLE(邊緣學(xué)習(xí)的可管理AI)組成的財團(tuán)成立了,其中包括ReRAM制造商Crossbar來創(chuàng)建使用ReRAM的AI平臺。

無論內(nèi)存類型如何,內(nèi)存都將駐留在AI和機(jī)器學(xué)習(xí)架構(gòu)中成為重點(diǎn)關(guān)注的領(lǐng)域。大數(shù)據(jù)應(yīng)用程序已經(jīng)推動了對使內(nèi)存更接近計算資源的體系結(jié)構(gòu)的需求。人工智能和機(jī)器學(xué)習(xí)已經(jīng)放大了這種需求,因?yàn)樗鼈兺ㄟ^神經(jīng)網(wǎng)絡(luò)對龐大的數(shù)據(jù)矩陣進(jìn)行多次累積操作。由于機(jī)器學(xué)習(xí)是通過處理數(shù)據(jù)來學(xué)習(xí)的,因此有很大的動力來尋找將計算和內(nèi)存更緊密地結(jié)合在一起的方法,這最終將節(jié)省功耗并提高性能。

編輯:hfy

-

嵌入式

+關(guān)注

關(guān)注

5142文章

19561瀏覽量

315378 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8493瀏覽量

134161 -

reram

+關(guān)注

關(guān)注

1文章

52瀏覽量

25631

發(fā)布評論請先 登錄

機(jī)器學(xué)習(xí)的算法應(yīng)用

Spark機(jī)器學(xué)習(xí)庫的各種機(jī)器學(xué)習(xí)算法

機(jī)器學(xué)習(xí)算法常用指標(biāo)匯總

基于ReRAM的機(jī)器學(xué)習(xí)算法

基于ReRAM的機(jī)器學(xué)習(xí)算法

評論