在線調(diào)試

在線調(diào)試也稱作板級(jí)調(diào)試,它是將工程下載到FPGA芯片上后分析代碼運(yùn)行的情況。有人會(huì)以為,我們不是已經(jīng)做了仿真了,甚至是時(shí)序仿真都通過了,還會(huì)存在問題么?在實(shí)際中,存在這么些情況我們需要用到在線調(diào)試:

仿真不全面而沒有發(fā)現(xiàn)的FPGA設(shè)計(jì)錯(cuò)誤。很多情況下,由于太復(fù)雜,無法做到100%的代碼覆蓋率;

在板級(jí)交互中,存在異步事件,很難做仿真,或者仿真起來時(shí)間很長(zhǎng),無法運(yùn)行;

除了本身FPGA外,還可能存在板上互連可靠性問題、電源問題和IC之間的信號(hào)干擾問題,都可能導(dǎo)致系統(tǒng)運(yùn)行出錯(cuò);

其他潛在問題:

在線調(diào)試的方式主要有兩種,一種是利用外部測(cè)試設(shè)備,把內(nèi)部信號(hào)傳送到FPGA針腳上,然后用示波器或者邏輯分析儀觀察信號(hào);另一種就是利用嵌入式邏輯分析儀,在設(shè)計(jì)中插入邏輯分析儀,利用JTAG邊緣數(shù)據(jù)掃描和開發(fā)工具完成數(shù)據(jù)交互。

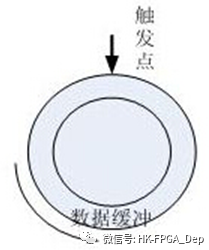

嵌入式邏輯分析儀的原理相當(dāng)于在FPGA中開辟一個(gè)環(huán)形存儲(chǔ)器,存儲(chǔ)器的大小決定了能夠查看的數(shù)據(jù)的深度,是可以人為設(shè)定的,但是不得超出資源。在FPGA內(nèi)部,根據(jù)設(shè)置的需要查看的信號(hào)節(jié)點(diǎn)信息和驅(qū)動(dòng)的采樣時(shí)鐘,對(duì)信息進(jìn)行采樣,并放置到設(shè)定的存儲(chǔ)空間里,存儲(chǔ)空間是環(huán)形的,內(nèi)容隨時(shí)間更新。然后通過判斷觸發(fā)點(diǎn)來檢查采集數(shù)據(jù),一旦滿足觸發(fā)條件,這個(gè)時(shí)候會(huì)停止掃描,然后將觸發(fā)點(diǎn)前后的一些數(shù)據(jù)返回給PC端的測(cè)試工具進(jìn)行波形顯示,供開發(fā)者進(jìn)行調(diào)試。

目前的調(diào)試工具都是和本身的FPGA開發(fā)平臺(tái)掛鉤的,不同F(xiàn)PGA廠商都會(huì)有開發(fā)軟件平臺(tái),嵌入式邏輯分析儀也就不同。Altera 廠家提供的是SignalTapII,而 Xilinx廠家提供的是 ChipScope,這些工具的具體使用在后面工具中詳解。

當(dāng)然這里除了嵌入式邏輯分析儀外,各廠家還提供了一些其他的在線調(diào)試工具,例如SignalProbe等等,但是或多或少的用的人不是很多,有興趣的可以找到該功能使用的說明手冊(cè)。

配置及固化

好了,到了我們最后一個(gè)環(huán)節(jié)就可以完成FPGA的流程了。這一部分我們分四個(gè)小節(jié)來講,首先是針對(duì)大家很多人不是太清楚的FPGA配置過程安排的,隨后一節(jié)為了更加深理解,舉了altera 的FPGA敘述配置全過程,第三小節(jié)是探討FPGA主要的配置模式,最后一節(jié)就是針對(duì)這些配置模式展開的對(duì)比選擇探討。

FPGA配置過程

在FPGA正常工作時(shí),配置數(shù)據(jù)存儲(chǔ)在SRAM中,這個(gè)SRAM單元也被稱為配置存儲(chǔ)器(configure RAM)。由于SRAM是易失性存儲(chǔ)器,因此在FPGA上電之后,外部電路需要將配置數(shù)據(jù)重新載入到芯片內(nèi)的配置RAM中。在芯片配置完成之后,內(nèi)部的寄存器以及I/O管腳必須進(jìn)行初始化(initialization),等到初始化完成以后,芯片才會(huì)按照用戶設(shè)計(jì)的功能正常工作,即進(jìn)入用戶模式。

FPGA上電以后首先進(jìn)入配置模式(configuration),在最后一個(gè)配置數(shù)據(jù)載入到FPGA以后,進(jìn)入初始化模式(initialization),在初始化完成后進(jìn)入用戶模式(user-mode)。在配置模式和初始化模式下,F(xiàn)PGA的用戶I/O處于高阻態(tài)(或內(nèi)部弱上拉狀態(tài)),當(dāng)進(jìn)入用戶模式下,用戶I/O就按照用戶設(shè)計(jì)的功能工作。

舉例——altera FPGA配置全過程

一個(gè)器件完整的配置過程將經(jīng)歷復(fù)位、配置和初始化等3個(gè)過程。FPGA正常上電后,當(dāng)其nCONFIG管腳被拉低時(shí),器件處于復(fù)位狀態(tài),這時(shí)所有的配置RAM內(nèi)容被清空,并且所有I/O處于高阻態(tài),F(xiàn)PGA的狀態(tài)管腳nSTATUS和CONFIG_DONE管腳也將輸出為低。當(dāng)FPGA的nCONFIG管腳上出現(xiàn)一個(gè)從低到高的跳變以后,配置就開始了,同時(shí)芯片還會(huì)去采樣配置模式(MSEL)管腳的信號(hào)狀態(tài),決定接受何種配置模式。隨之,芯片將釋放漏極開路(open-drain)輸出的nSTATUS管腳,使其由片外的上拉電阻拉高,這樣,就表示FPGA可以接收配置數(shù)據(jù)了。在配置之前和配置過程中,F(xiàn)PGA的用戶I/O均處于高阻態(tài)。

在接收配置數(shù)據(jù)的過程中,配置數(shù)據(jù)由DATA管腳送入,而配置時(shí)鐘信號(hào)由DCLK管腳送入,配置數(shù)據(jù)在DCLK的上升沿被鎖存到FPGA中,當(dāng)配置數(shù)據(jù)被全部載入到FPGA中以后,F(xiàn)PGA上的CONF_DONE信號(hào)就會(huì)被釋放,而漏極開路輸出的CONF_DONE信號(hào)同樣將由外部的上拉電阻拉高。因此,CONF_DONE管腳的從低到高的跳變意味著配置的完成,初始化過程的開始,而并不是芯片開始正常工作。

INIT_DONE是初始化完成的指示信號(hào),它是FPGA中可選的信號(hào),需要通過Quartus II工具中的設(shè)置決定是否使用該管腳。在初始化過程中,內(nèi)部邏輯、內(nèi)部寄存器和I/O寄存器將被初始化,I/O驅(qū)動(dòng)器將被使能。當(dāng)初始化完成以后,器件上漏極開始輸出的INIT_DONE管腳被釋放,同時(shí)被外部的上拉電阻拉高。這時(shí),F(xiàn)PGA完全進(jìn)入用戶模式,所有的內(nèi)部邏輯以及I/O都按照用戶的設(shè)計(jì)運(yùn)行,這時(shí),那些FPGA配置過程中的I/O弱上拉將不復(fù)存在。不過,還有一些器件在用戶模式下I/O也有可編程的弱上拉電阻。在完成配置以后,DCLK信號(hào)和DATA管腳不應(yīng)該被浮空(floating),而應(yīng)該被拉成固定電平,高或低都可以。

如果需要重新配置FPGA,就需要在外部將nCONFIG重新拉低一段時(shí)間,然后再拉高。當(dāng)nCONFIG被拉低后,nSTATUS和CONF_DONE也將隨即被FPGA芯片拉低,配置RAM被清,所有I/O都變成三態(tài)。當(dāng)nCONFIG和nSTATUS都變?yōu)楦邥r(shí),重新配置就開始了。

配置模式

這一塊分成兩部分,一部分是在線調(diào)試配置,另一塊是固化,即將工程配置到相應(yīng)存儲(chǔ)單元中,上電后,通過存儲(chǔ)在存儲(chǔ)器中的內(nèi)容配置FPGA。

1)在線配置

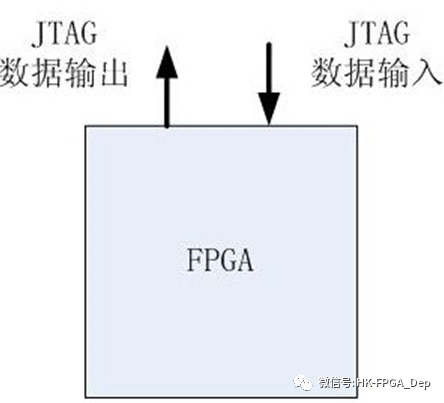

第一部分在線調(diào)試配置過程是通過JTAG模式完成的,如下圖所示,在JTAG模式中,PC和FPGA通信的時(shí)鐘為JTAG接口的TCLK,數(shù)據(jù)直接從TDI進(jìn)入FPGA,完成相應(yīng)功能的配置。

JTAG接口是一個(gè)業(yè)界標(biāo)準(zhǔn)接口,主要用于芯片測(cè)試等功能。FPGA基本上都可以支持JTAG命令來配置FPGA的方式,而且JTAG配置方式比其他任何方式優(yōu)先級(jí)都高。JTAG接口由4個(gè)必需的信號(hào)TDI, TDO, TMS和TCK以及1個(gè)可選信號(hào)TRST構(gòu)成,其中:

TDI,用于測(cè)試數(shù)據(jù)的輸入;

TDO,用于測(cè)試數(shù)據(jù)的輸出;

TMS,模式控制管腳,決定JTAG電路內(nèi)部的TAP狀態(tài)機(jī)的跳變;

TCK,測(cè)試時(shí)鐘,其他信號(hào)線都必須與之同步;

TRST,可選,如果JTAG電路不用,可以將其連到GND。

2)固化

第二部分固化程序到存儲(chǔ)器中的過程可以分為兩種方式,主模式和從模式。主模式下FPGA器件引導(dǎo)配置操作過程,它控制著外部存儲(chǔ)器和初始化過程;從模式下則由外部計(jì)算機(jī)或控制器控制配置過程。主、從模式從傳輸數(shù)據(jù)寬度上,又分別可以分為串行和并行。

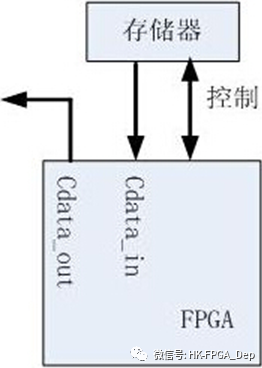

I)主串模式

主串模式是最簡(jiǎn)單的固化模式,如下圖所示,這個(gè)模式過程不需要為外部存儲(chǔ)器提供一系列地址。它利用簡(jiǎn)單的脈沖信號(hào)來表明數(shù)據(jù)讀取的開始,接著由FPGA提供給存儲(chǔ)器時(shí)鐘,存儲(chǔ)器在時(shí)鐘驅(qū)動(dòng)下,將數(shù)據(jù)輸入到FPGA Cdata_in端口。

II)主并模式

主并模式其實(shí)和主串模式的一樣機(jī)理,只不過是在主串的基礎(chǔ)上,同周期數(shù)內(nèi)傳送的數(shù)據(jù)變成8位,或者更高,如下圖。這樣一來,主并行相比主串行的速度要優(yōu)先了。現(xiàn)代有些地方已采用這種方式來配置FPGA的了。

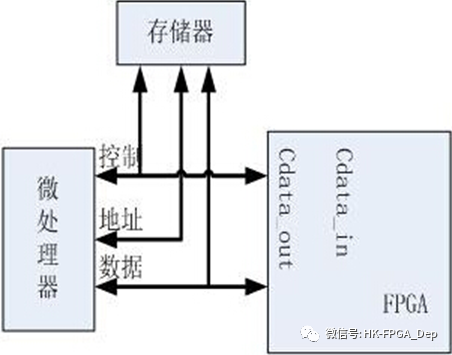

III)從并模式

從上面看到,主模式下的連接還是很簡(jiǎn)單的。但是有時(shí)候,系統(tǒng)可能用其他微處理器來對(duì)FPGA進(jìn)行配置。這里的微處理器可以指FPGA內(nèi)嵌的處理器,比如說Nios。微處理器控制著何時(shí)配置FPGA,從哪讀取配置文件。如下圖,這種方式的優(yōu)點(diǎn)是處理器可以靈活隨時(shí)變更FPGA配置,同時(shí)配置的速度也快。微處理器先從外部存儲(chǔ)設(shè)備里讀取一個(gè)字節(jié)的數(shù),然后寫到FPGA里。

IV)從串模式

理解了從并模式,從串模式就不用很多解釋了,它的特點(diǎn)就是節(jié)約FPGA管腳I/O。

V)多片級(jí)聯(lián)

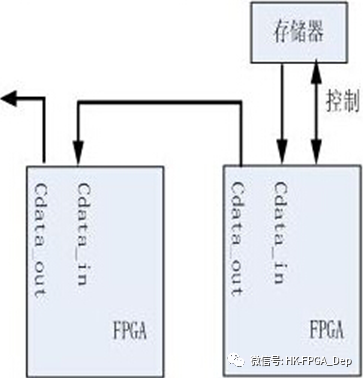

多片模式有兩種,一種是采用菊花鏈的思想,多片F(xiàn)PGA共享一個(gè)存儲(chǔ)器,另外一個(gè)是可以使用其他存儲(chǔ)器配置不同的FPGA。如果所示是一個(gè)共享型的結(jié)構(gòu),顯示啟動(dòng)了。這里分主FPGA和從FPGA,主FPGA和存儲(chǔ)器是使用串行主模式來配置,而后面那個(gè)的配置是通過第一配置好的FPGA上微處理器進(jìn)行協(xié)調(diào)的。

模式選擇

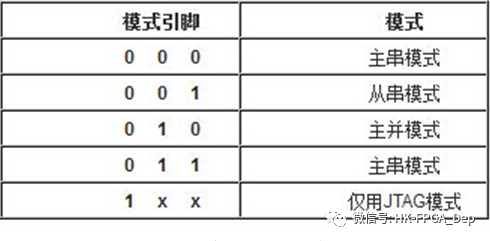

現(xiàn)今FPGA應(yīng)該可以支持上面五種配置模式,是通過3個(gè)模式引腳來實(shí)現(xiàn)的,具體的映射如下表,在今后模式還是有可能增加的。

在PS模式下,如果你用電纜線配置板上的FPGA芯片,而這個(gè)FPGA芯片已經(jīng)有配置芯片在板上,那你就必須隔離纜線與配置芯片的信號(hào)。一般平時(shí)調(diào)試時(shí)不會(huì)把配置芯片焊上的,這時(shí)候用纜線下載程序。只有在調(diào)試完成以后,才把程序燒在配置芯片中, 然后將芯片焊上.或者配置芯片就是可以方便取下焊上的那種。這樣出了問題還可以方便地調(diào)試.。

對(duì)FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通過一條下載線進(jìn)行燒寫的話,那么開始的”nCONFIG,nSTATUS”應(yīng)該上拉,要是考慮多種配置模式,可以采用跳線設(shè)計(jì)。讓配置方式在跳線中切換,上拉電阻的阻值可以采用10K一般在做FPGA實(shí)驗(yàn)板的時(shí)候,用AS+JTAG方式,這樣可以用JTAG方式調(diào)試,而最后程序已經(jīng)調(diào)試無誤了后,再用AS模式把程序燒到配置芯片里去。

責(zé)任編輯人:CC

-

FPGA

+關(guān)注

關(guān)注

1644文章

22007瀏覽量

616375 -

FPGA開發(fā)

+關(guān)注

關(guān)注

1文章

44瀏覽量

15372

原文標(biāo)題:詳解FPGA開發(fā)在線調(diào)試&配置及固化

文章出處:【微信號(hào):HK-FPGA_Dep,微信公眾號(hào):FPGA技術(shù)支持】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA實(shí)戰(zhàn)演練邏輯篇69:基于FPGA的在線系統(tǒng)調(diào)試概述

Xilinx FPGA在線更新配置數(shù)據(jù)交流

玩轉(zhuǎn)Zynq連載5——基于Vivado的在線板級(jí)調(diào)試概述

FPGA在線配置模塊和自動(dòng)測(cè)試模塊實(shí)現(xiàn)過程

基于USART接口的STM32F2xx如何開發(fā)在線應(yīng)用編程

可在線升級(jí)的FPGA并行配置方法的實(shí)現(xiàn)

簡(jiǎn)化Xilinx和Altera FPGA調(diào)試過程

簡(jiǎn)化FPGA配置設(shè)計(jì)過程

FPGA開發(fā)板使用和配置方式

chipscope使用教程以及FPGA在線調(diào)試的方法

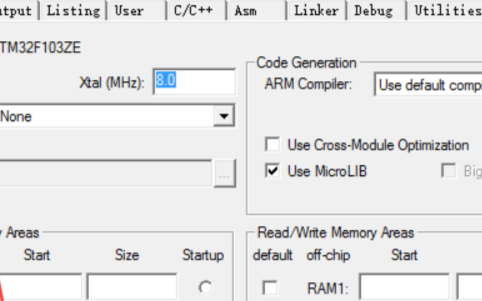

STM32內(nèi)部RAM在線調(diào)試配置方法及詳細(xì)說明 (基于Keil開發(fā)工具)

STM8S 使用IAR在線調(diào)試配置

RISC-V MCU開發(fā) (五):調(diào)試配置

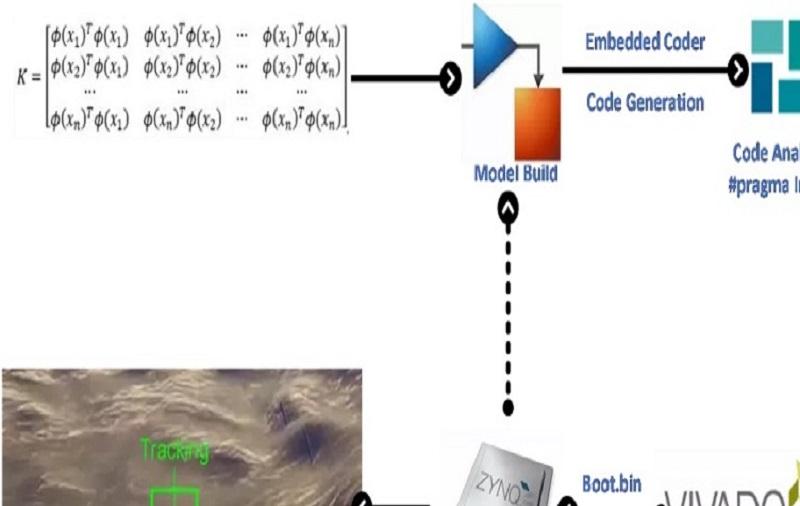

7.22在線研討會(huì) | 基于高層級(jí)設(shè)計(jì)的FPGA開發(fā)快速迭代

介紹FPGA在線調(diào)試的一大利器—VIO

FPGA開發(fā)在線調(diào)試和配置過程

FPGA開發(fā)在線調(diào)試和配置過程

評(píng)論