目前,國內生產的部分在線仿真調試器可以對部分嵌入式芯片進行仿真調試。但從本質上,這些仿真調試器無法對所有帶在線調試功能的嵌入式芯片進行仿真調試。BDI2000和TRACE32等仿真器可以在不改變硬件條件下,通過下載針對特定嵌入式芯片的調試“核”來實現對不

2011-01-16 11:02:01 737

737

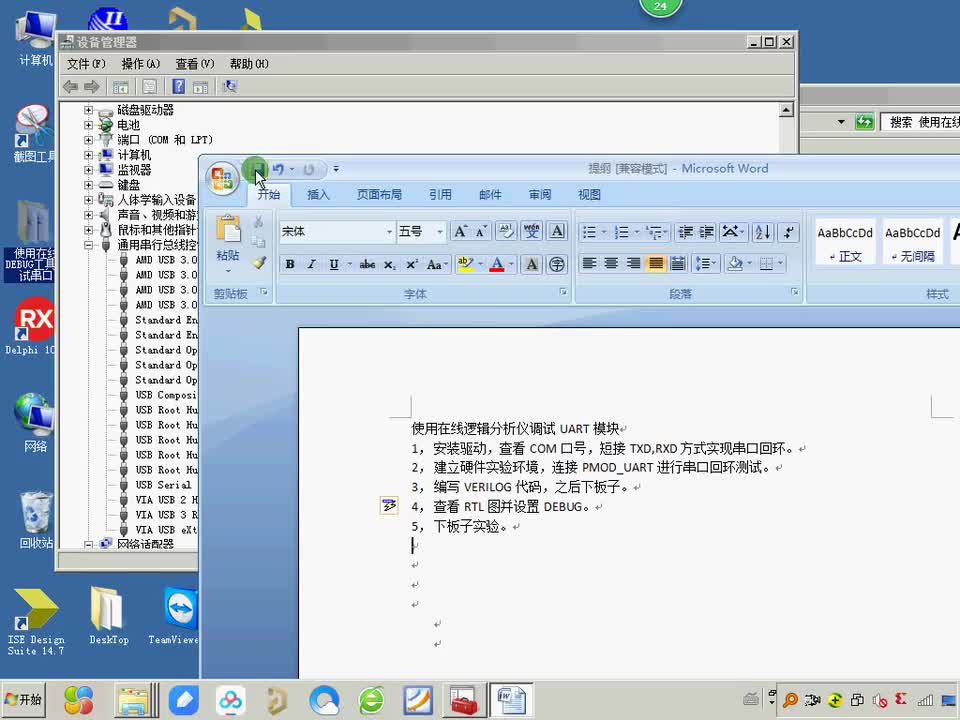

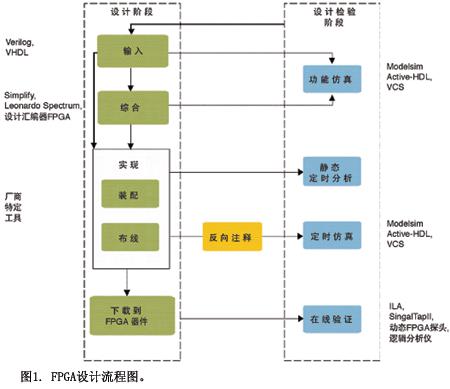

FPGA調試時硬件設計中及其重要的一步,本文就在FPGA調試過程中存在3種常見的誤解,進行一些討論....

2018-09-19 09:27:50 4045

4045 日常的FPGA開發常常會遇到“編碼與上機調試使用各自的電腦”的場景,解決方法一般如下。

2023-05-25 14:36:44 1751

1751

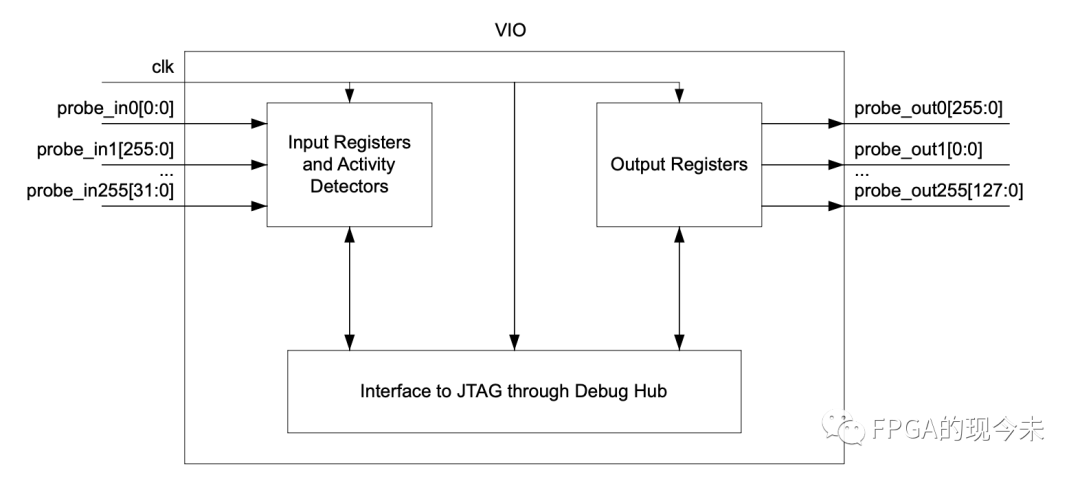

在以往的項目中,要控制FPGA內部某個信號的值,往往是通過配置寄存器來實現的。其實Xilinx還提供了一個叫VIO的core,可以動態改變FPGA內部某個信號的值,但是一直沒有用過,一來對于以前的項目來說,沒有應用場景,通過寄存器就可以配置了;二來感覺這個東西不是很“實用”。

2023-12-11 18:26:52 697

697

STM8,STM32 - 調試器(在線/在系統)

2024-03-14 22:29:44

FPGA調試技術資料“中國高速列車網絡控制系統”課題組提供資料FPGA常用調試技術?查看綜合報告?仿真測試?在線調試?其他工具FPGA調試技術資料[hide][/hide]

2012-03-09 14:33:28

在線調試方式大都是通過FPGA器件引出的JTAG接口,同時使用了一些FPGA片內固有的邏輯、存儲器或布線資源就能夠實現的。這些調試功能通常也只需要隨著用戶設計所生產的配置文件一同下載到目標FPGA器件中

2015-09-02 18:39:49

This application note covers key methods of debugging FPGAs along with technologies that reduce the number of pins needed for debug.

2019-08-08 12:24:46

本帖最后由 eehome 于 2013-1-5 10:00 編輯

該培訓教程介紹了一個通過串口即可完成在線調試仿真所有51單片機的調試系統-MSUODS,該系統無需額外硬件支持,只需用戶目標

2011-08-07 22:51:08

在高溫下具有更低功耗的優勢。本文根據Actel公司的產品手冊及相關文件,設計了一種由DSP控制實現FPGA在線編程的方案,使Actel的FPGA能應用于需要在線升級的應用場合中,充分發揮其高溫高可靠性

2019-06-13 05:00:07

提示:文章寫完后,目錄可以自動生成,如何生成可參考右邊的幫助文檔文章目錄前言一、簡介二、特點三、安裝四、使用說明總結前言FreeMaster為NXP公司為用戶提供的一款運行在PC機上的圖形化在線調試

2021-07-14 06:25:48

你好,

AD7982的VREF與VDD/VIO之間是否有時序要求?手冊里沒查到。

在目前我們的設計中,VREF(5V)先于VDD(2.5V)和VIO(2.5V)上電,不知是否會有問題。謝謝。

2023-12-14 06:44:01

大家好,我在使用Arty(Artix 7 FPGA)進行調試時遇到了一些麻煩。背景:我使用ILA在Zybo(Zynq)和Nexys 4 DDR(也是Artix 7)上調試我的程序,一切正常。我

2020-08-26 15:20:18

在之前的系列文章中,我為大家詳細講解了Lattice開發工具的一些基本的使用方法,如怎樣申請Diamond License、如何生成IP核、如何新建工程……今天我將繼續介紹Diamond軟件

2019-12-13 16:11:44

1. GDB調試利器1.1. GDB簡介在單片機開發中,KEIL、IAR、ADS1.2等集成開發環境下的調試工具對程序開發有很大的幫助, 尤其是出現各種疑難雜癥的bug時,往往只能通過單步調試、堆棧

2021-11-03 08:25:58

flash。IAP在線升級的確是個好東西,對于那些已經安裝好的設備來說,真是一大利器。IAP的核心理論其實比較簡單:總共有兩個程序,一個叫bootloader,一個叫app。其中bo

2021-08-06 07:07:07

請問VIO輸出的控制信號的類型該如何設置?如圖有三種類型分別是什么意思

2019-04-27 15:50:33

KEIL在線調試1 程序調試方式(1) 使用SEGGER J-Flash(J-Link)下載程序到閃存中運行。(2) 使用串口ISP 來下載HEX 文件到CPU 中運行。(3) J-Link

2021-07-22 06:04:53

怎么對STC12的單片機實現在線調試

2023-10-13 07:47:02

請問TMS570系列怎么設置在RAM下在線調試?一直在FLASH下在線調試,現在怎么改成在RAM下在線調試?

2018-05-25 00:48:02

的JTAG Chain和Debug Core,因此本文提出一種比較方便的調試方法來同時使用這兩個core:ILA通過analyzer查看,VIO通過TCL控制。使用步驟:使用CoreGEN生成VIO

2012-03-08 15:29:11

我想要對FPGA實現脫離仿真器在線升級的功能,要能防掉電,不知道大家有做過的沒? 我現在的想法是通過外部cpu來對FPGA進行配置和升級,FPGA采用從模式,比如用一個DSP來配置FPGA,上電

2017-01-17 20:00:09

`Xilinx FPGA入門連載40:SRAM讀寫測試之Chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2015-12-25 15:04:32

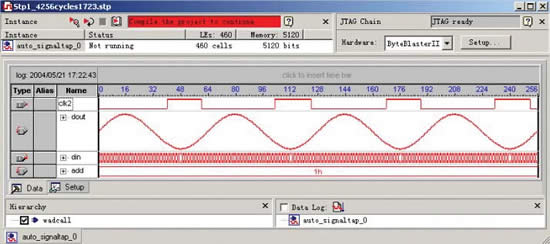

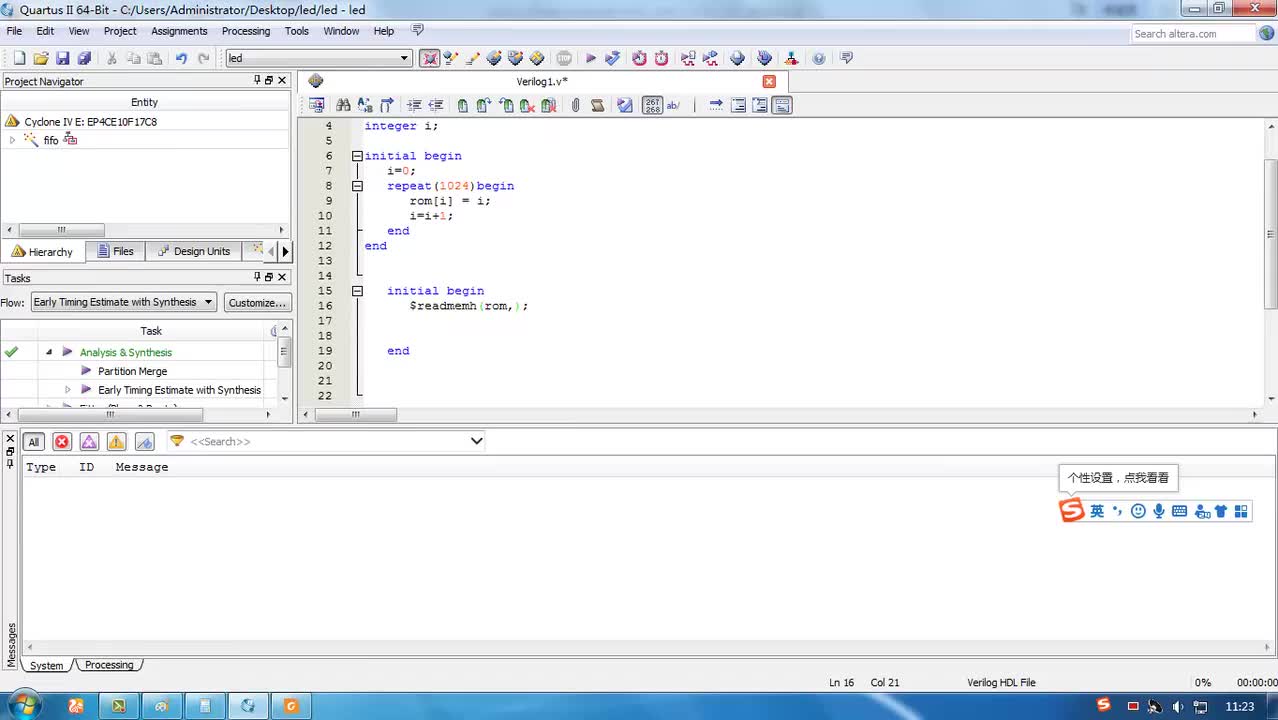

`Xilinx FPGA入門連載46:FPGA片內ROM實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm

2016-01-18 12:30:14

Xilinx FPGA入門連載50:FPGA片內RAM實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-01-27 13:10:35

`Xilinx FPGA入門連載54:FPGA 片內FIFO實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-04 13:13:12

`Xilinx FPGA入門連載58:FPGA 片內異步FIFO實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:13:05

`Xilinx FPGA入門連載61:FPGA 片內ROM FIFO RAM聯合實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com

2016-03-21 12:19:39

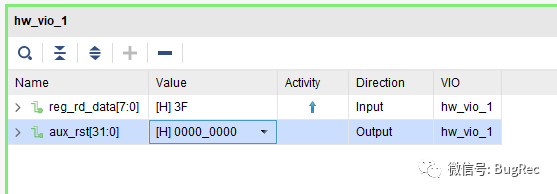

DSP的CCS軟件在線調試,不僅能觀察數據,還能在線修改參數值,我想問一下vivado在線調試有這個功能嗎,我看見debug好像只能在線觀察,我想把bit文件下載到板上,我不僅要觀察,還想在線改變一些參數值(不需重新編譯),vivado有這個功能嗎??急求,謝謝大家了!!!

2017-12-20 14:03:27

、位圖輸出C文件等眾多功能于一身的綜合型調試軟件,并擁有在線更新功能,真正做到了緊握潮流脈搏的要求。 單片機多功能調試助手優勢:●保持為單文件狀態,不會因為需要保存配置信息而創建其他其他文件,易于攜帶

2012-12-08 16:37:55

在設計基于FPGA的電子系統時,一般需要用示波器、邏輯分析儀等外部測試設備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設備上進行觀察分析。當然,前提是需要保留足夠多的引腳,以便能選擇信號來驅動

2019-08-19 08:03:56

大家好。我使用VIO IP在ISE Design SUite軟件中調試設計。當我運行工具有以下錯誤:檢查擴展設計...錯誤:NgdBuild:604 - 類型為'chipscope_vio'的邏輯塊

2019-08-02 08:10:22

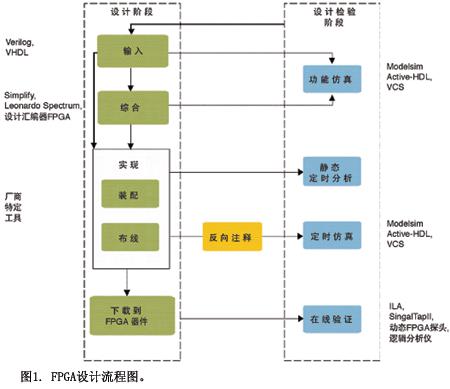

摘要:隨著FPGA的設計速度、尺寸和復雜度明顯增長,在整個設計流程中的實時驗證和調試部分成為當前FPGA系統的關鍵部分。獲得FPGA內部信號有限、FPGA封裝和印刷電路板(PCB)電氣噪聲,這一

2019-06-25 07:51:47

在TI網站上網頁在線設計了一個電源模塊,下載下來的原理圖和PCB如圖,請教一下PCB那一大片的紅色和綠色是什么東西?謝謝

2016-06-09 16:05:22

過Quartus軟件里自帶的signaltap進行線上調試,但是這個軟件不知車CPLD芯片,想問問各位前輩。1.在線調試CPLD有什么好用的軟件推薦,簡單點的?2.各位在調試的時候線下仿真沒有問題之后,在線仿真功能不實現一般都是因為什么問題?多謝各位大神,好人一生平安!

2017-03-31 09:35:33

本帖最后由 神奇艾爾斯 于 2019-10-28 10:50 編輯

如題,我想寫一個計數器,我設置一個值開始加,加到1000停止;count在always塊里,是reg型,好像無法連到vio上

2019-10-28 09:57:38

智能駕駛數據后處理分析利器—INTEWORK-VDA

2021-01-13 06:27:40

【FPGA入門教程】《HELLO FPGA》 - 項目實戰篇http://t.elecfans.com/981.html,重要的是免費在線學習。小梅哥FPGA設計思想與驗證方法視頻教程http

2018-09-11 09:38:25

遠程在線更新FPGA程序系統的硬件結構是怎樣構成的?怎樣去設計一種遠程在線更新FPGA程序系統?

2021-06-18 09:16:18

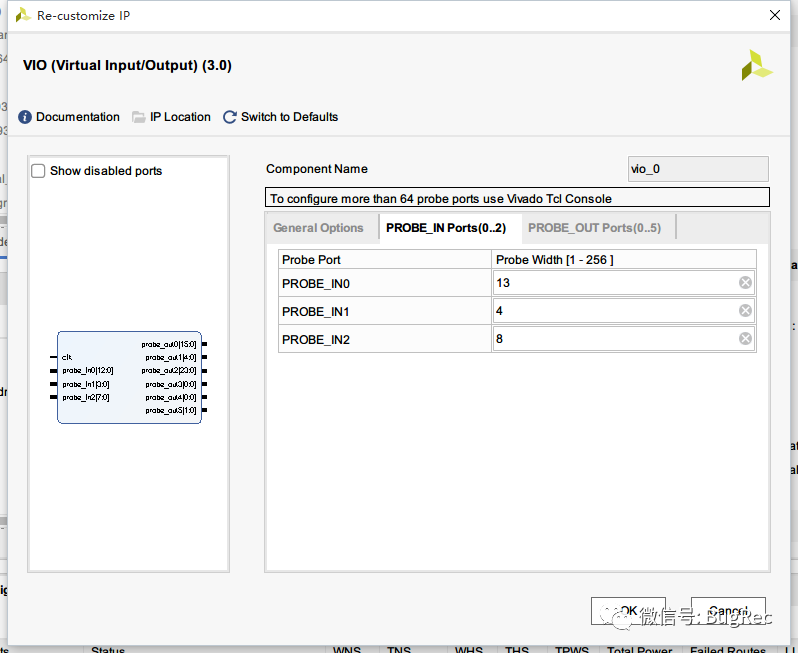

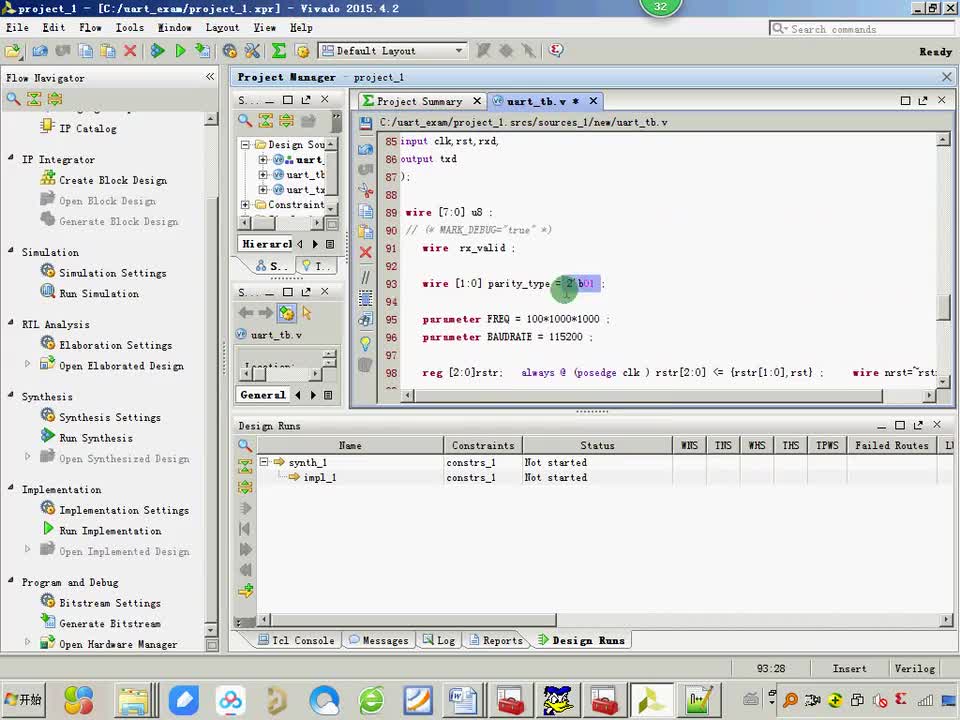

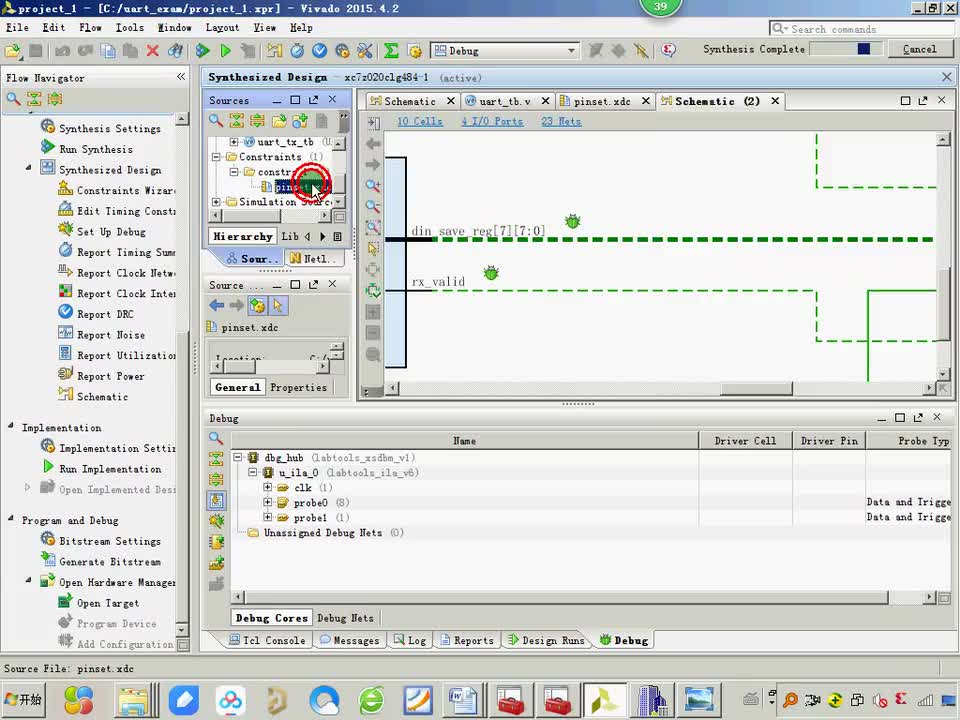

1概述基于Vivado的板級調試介紹,可以參考文檔《玩轉Zynq-基礎篇:基于Vivado的在線板級調試概述.pdf》。這里我們以zstar_ex55工程為例,對FPGA的Virtual IO

2019-11-18 15:08:59

` 1概述本實例(zstar_ex55)在zstar_ex54的基礎上,增加VirtualIO(VIO)實現在線板級調試的功能,意圖讓大家學會VIO這種基于FPGA的簡單實用的在線板級調試手段。2

2019-11-21 10:04:31

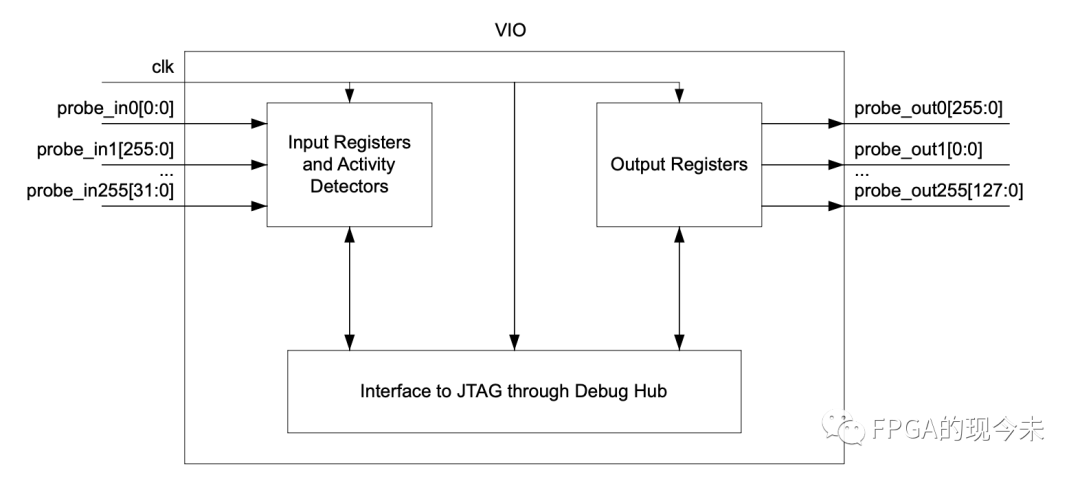

使用VIO功能實現FPGA內部信號實時的監控或驅動。VIO調試應用的主要場景可能是速率要求不高,但又希望可以在線交互的一些信號接口,比如一些開關信號的控制或狀態信號的實時查看。VIO功能模塊只能通過配置

2019-05-24 15:16:32

SRIO不正常的工作情況。具體描述如下:1、在線調試時,DSP的外設SRIO能正常接收每個時隙下FPGA發過來的四組數據和四個doorbell信號(每一組數據后緊跟一個doorbell信號),DSP

2018-07-25 08:53:49

請問NXP在線調試工具FreeMaster怎么使用?

2021-10-11 07:27:28

官網介紹:http://www.mornship.com/MSUODS/MSUODSInfo.htm曉舟通用在線調試系統(MSUODS)簡介 曉舟通用在線調試系統(MornShip

2011-08-24 22:30:09

FPGA調試工具chipscope,學習與使用FPGA必用的工具。。

2009-03-23 09:45:00 86

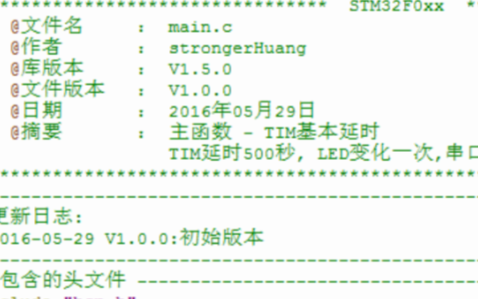

86 本文主要講述的是單片機的在線調試方法。

2009-04-22 16:43:23 33

33 混合CPU_FPGA系統的調試方法:

2009-07-23 10:44:07 7

7 針對基于SRAM 結構的FPGA,詳細介紹了一種采用可在線升級的SST89V564RD微處理器對其進行上電PPA(被動并行異步)配置,不僅實現了FPGA 的在線配置,而且通過微處理器的IAP 技術

2009-09-15 16:27:50 23

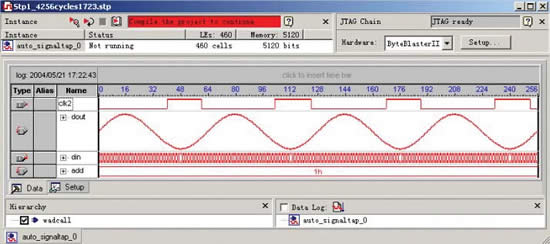

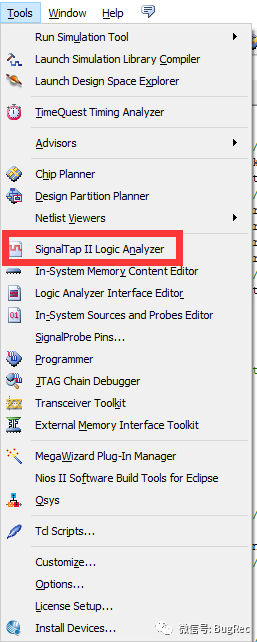

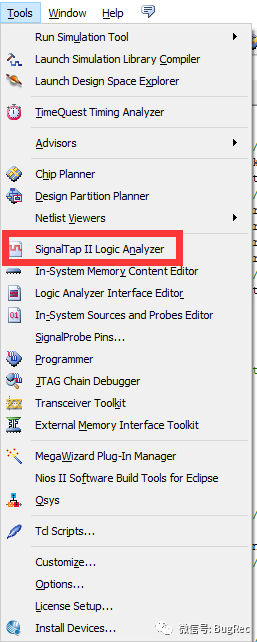

23 本文介紹了可編程邏輯器件開發工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設計實例,詳細介紹使用SignalTap II對FPGA調試的具體方法和步驟。關鍵字 : S

2009-11-01 14:49:39 45

45 本章介紹常用的調試命令,利用在線匯編,各種設置斷點進行程序調試的方法,并通過實例介紹這些方法的使用。

2010-01-09 11:29:58 62

62 實用FPGA的調試工具—ChipScope Pro

ChipScope Pro應用于FPGA調試階段,它具有傳統邏輯分析儀的功能,可以觀察FPGA內部的任何信號,觸發條件,數據寬度和深度等的設

2010-02-09 15:10:46 95

95 摘 要 :本文介紹了可編程邏輯器件開發工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設計實例,詳細介紹使用SignalTap II對FPGA調試的具體方

2009-06-20 10:42:18 1366

1366

電壓比較器VIO的開環測試

輸入失調電壓(VIO)是電壓比較器(以下簡稱比較器)一個重要的電性能參數,GB/T 6798-1996中,將其定義為“使輸出電壓為規定

2010-01-15 17:57:47 1790

1790 FPGA硬件系統的調試方法

在調試FPGA電路時要遵循一定的原則和技巧,才能減少調試時間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進行

2010-02-08 14:44:42 2558

2558 本文提出了一種基于SoPC的FPGA在線測試方法,是對現有FPGA在線測試方法的一種有效的補充。

2011-04-18 11:46:20 1145

1145

縱觀數字集成電路的發展歷史,電子產品的市場正在逐漸細分。本書主要重點介紹相關問題和技巧,幫助您在調試 FPGA 系統是提高您的工作效率。希望對您的工作學習有所幫助!

2011-07-11 16:49:37 403

403 集成運放輸入失調電壓VIO的測試 失調電壓VIO ,即室溫及標準電源電壓下,運放兩輸入端間信號為零時,為使輸出為零,在輸入端加的補償電壓。 下圖為失調電壓測試電路:

2011-09-10 23:38:50 118

118 在調試FPGA電路時要遵循必須的原則和技巧,才能降低調試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執行 FPGA硬件系統的調試。 1、在焊接硬件電路前,首先要測試電路板

2013-01-16 11:59:58 4665

4665 一、基礎知識 1.1、Ollydbg Ollydbg(簡稱OD)是Windows平臺下Ring3級的程序調試利器。程序調試有靜態調試和動態調試兩種。靜態調試是指將程序源代碼編譯成可執行程序之前,用手

2017-10-09 18:36:55 2

2 在設計基于FPGA的電子系統時,一般需要用示波器、邏輯分析儀等外部測試設備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設備上進行觀察分析。當然,前提是需要保留足夠多的引腳,以便能選擇信號來驅動

2018-02-14 09:19:00 645

645 本文檔內容介紹了基于chipscope使用教程以及FPGA在線調試的方法,供參考

2018-03-02 14:09:49 9

9 在線調試工具E1

2018-07-23 00:08:00 3512

3512 在線調試工具minicube2

2018-07-20 01:56:46 3793

3793 在線調試工具e8a

2018-07-20 01:40:00 3905

3905 在線調試工具EZ-CUBE

2018-07-20 05:05:00 5541

5541 本文重點介紹在調試FPGA系統時遇到的問題及有助于提高調試效率的技術,針對Altera和Xilinx的FPGA調試提供了最新的方法和工具。

2018-11-28 08:43:00 2095

2095

信號線設置成類似于CPU總線的結構,監測計數器或者狀態寄存器編成相應的地址,輪詢讀取回PC,在PC上通過TCL或者其它語言捕獲數據。甚至可以將多個FPGA芯片都通過VIO進行調試,遠程操作,效率也可以大大提升。另外,也可以設置專門的測試幀,在里面打各種不同大小的閉環,層層檢測,發現問題。

2019-07-19 10:19:15 6570

6570

Keil(MDK-ARM)系列教程(八)_在線調試(Ⅰ)

2020-03-20 14:54:55 3111

3111

Keil(MDK-ARM)使用教程(三)_在線調試

2020-04-07 14:30:13 4977

4977

SMT貼片機分為離線編程和在線編程調試,在線編程調試就是在SMT貼片機上對離線編程的程序進行優化調試編輯。SMT貼片機在線編程調試總體上就是兩個步驟,一個是離線編程的程序進行編程,然后就是總體檢查并備份到貼片機電腦內。

2020-03-10 11:19:03 8483

8483 對于FPGA調試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環境下進行仿真和調試,開發板類型EP4CE15F17。

2020-03-29 11:37:00 1142

1142 FPGA概述FPGA調試介紹調試挑戰設計流程概述■FPGA調試方法概述嵌入式邏輯分析儀外部測試設備■使用 FPGAVIEW改善外部測試設備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 9

9 在線調試也稱作板級調試,它是將工程下載到FPGA芯片上后分析代碼運行的情況。

2020-11-01 10:00:49 3948

3948

開發板(在本文中將其簡稱為“FPGA開發板”)和專用 JTAG 調試器(在本文中將其簡稱為“JTAG 調試器”)。

2021-03-23 10:00:28 41

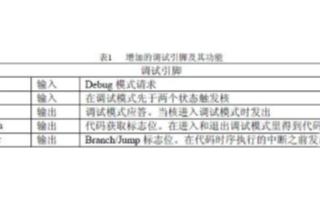

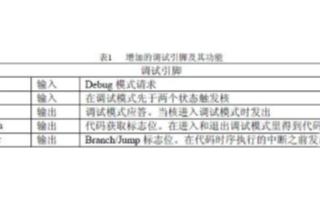

41 為了能讓嵌入式微處理器的片上調試功能也能夠像高級語言編程工具那樣支持斷點設置、單步執行、寄存器內容的查看和內存內容查看等功能,文章提出了一種在線調試模塊設計,此設計為嵌入式微處理器增加了一些專用

2021-03-23 14:55:48 2207

2207

本文檔介紹了如何使用MPLAB ICD 4在線調試器作為開發工具在目標板上仿真和調試固件,以及如何對器件編程。

2021-05-12 09:45:07 15

15 和FPGA設計進行連接。由于VIO核與被監視和驅動的設計同步,因此應用于設計的時鐘約束也適用于VIO核內的元件。當使用這個核進行實時交互時,需要使用Vivado邏輯分析特性。 接下來將介紹VIO的原理及應用,內容主要包括設計原理、添加VIO核、生成比特流文件和下載并調試設計。 設計原理

2021-09-23 16:11:23 6841

6841

1. GDB調試利器1.1. GDB簡介在單片機開發中,KEIL、IAR、ADS1.2等集成開發環境下的調試工具對程序開發有很大的幫助, 尤其是出現各種疑難雜癥的bug時,往往只能通過單步調試、堆棧

2021-11-02 14:06:20 12

12 STM8S103單片機使用IAR進行程序開發和調試1.在程序調試沒有錯誤后 選擇 “Options” 進行配置2.選擇“Debugger”選項“ST-LINK”3.選擇其中一個進行在線調試注:兩種調試模式的區別

2021-12-03 10:21:02 15

15 大家好,我是痞子衡,是正經搞技術的痞子。今天痞子衡給大家分享的是MCUXpresso IDE下在線調試時使用不同復位策略的現象總結。本篇實際上是《IAR在線調試時設不同復位類型可能會導致i...

2021-12-04 12:21:06 8

8 使用Jtag Master調試FPGA程序時用到tcl語言,通過編寫tcl腳本,可以實現對FPGA的讀寫,為調試FPGA程序帶來極大的便利,下面對FPGA調試過程中常用的tcl語法進行介紹,并通過tcl讀FIFO的例子,說明tcl在實際工程中的應用。

2022-02-19 19:44:34 2272

2272 對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 1900

1900

一般情況下ILA和VIO都是用在chipscope上使用,VIO可以作為在chipscope時模擬IO。

2022-06-12 15:51:54 1682

1682 AWPLC 除了提供打印日志的調試方式外,還提供了在線調試的功能。本文用我們之前講過的定時器例子,來演示如何使用在線調試功能。

2022-11-17 11:51:51 601

601 Xilinx被AMD收購的事情把我震出來了,看了看上上一篇文章講了下仿真的文件操作,這篇隔了很久遠,不知道該從何講起,就說說FPGA的在線調試的一些簡單的操作方法總結。

2023-06-19 15:52:21 1225

1225

剖析》分析了用戶在進行大規模原型驗證過程中的多FPGA聯合調試難題,并介紹了一種新型FPGA原型驗證深度跟蹤調試解決方案,用于幫助客戶在SoC開發過程中解決調試問

2022-06-16 10:16:48 628

628

視覺慣性融合技術應用于機器人和自動駕駛方面。單目相機和低成本IMU成為最佳選擇。因為VIO系統的高度非線性,初值對視覺慣性系統很重要,但很難獲得精確的初始狀態。

2023-06-21 09:22:07 581

581

1 推動FPGA調試技術改變的原因 進行硬件設計的功能調試時,FPGA的再編程能力是關鍵的優點。CPLD和FPGA早期使用時,如果發現設計不能正常工作,工程師就使用“調試鉤”的方法。先將要觀察

2023-12-20 13:35:01 147

147

電子發燒友App

電子發燒友App

評論