電子裝備系統是星鏈、火星探測器、玉兔、嫦娥等航天器的重要支撐,而宇航級芯片則是航天航空電子裝備的心臟。江湖中流傳這樣一個傳說,Xilinx的一款宇航級FPGA芯片,其單價約500萬元,為史上最貴芯片。這個傳說并不是說完全沒有依據,宇航級芯片必須具備抗輻照特性,其身價往往是我們生活中常見的消費級芯片的數十倍,甚至成百上千倍。

那么,與消費級芯片相比,這些昂貴的宇航級芯片在設計階段有什么特別之處呢?

1.宇航級芯片所處的空間環境

在航天器運行的空間環境中,存在著大量的高能粒子和宇宙射線。這些粒子和射線會穿透航天器屏蔽層,與元器件的材料相互作用產生輻射效應,引起器件性能退化或功能異常,影響航天器的在軌安全。引起器件輻射效應的主要空間輻射源包括地球輻射帶、銀河宇宙射線、太陽宇宙線和人工輻射。

其中,對芯片工作影響最為嚴重的輻射效應當屬“單粒子效應”。據數據統計,從 1971 年到 1986 年間,國外發射的 39 顆同步衛星共發生了 1589 次故障,有 1129 次故障與空間輻射有關,且其中的 621 次故障是由于單粒子效應導致的。這些統計數據說明了航天應用中電子器件的主要故障來自于空間輻射,而單粒子效應導致的故障在其中占較大比重。

這些故障中,部分是永久性不可逆的,如發生單粒子鎖定導致芯片內部局部短路從而產生大電流燒毀器件。針對此類錯誤可以應用一些特定工藝或器件庫來避免。

而太空中大部分錯誤是由于半導體器件的邏輯狀態跳變而導致的可恢復的錯誤,如單粒子翻轉導致存儲器存儲內容錯誤。

單粒子翻轉(Single-Event Upsets,SEU)指的是元器件受輻照影響引起電位狀態的跳變,“0”變成“1”,或者“1”變成“0”,但一般不會造成器件的物理性損傷。正因為“單粒子翻轉”頻繁出現,因此在芯片設計階段需要重點關注。

這也是這篇文章的重點。2.在芯片設計階段如何防護“單粒子翻轉”(1) 選擇合適的工藝制程在航天領域,并不是工藝制程越小越好。

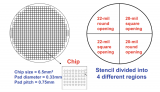

通常來講,工藝制程越小,抗輻照能力越差。因此,為了確保可靠性,一般會選擇較大線寬的制程,比如0.18um、90nm、65nm等,而不會一味追求摩爾定律的前沿制程。

(2)加固標準單元工藝庫

標準單元工藝庫是數字芯片的基石。如果把數字芯片看做一個建筑,標準單元工藝庫就是構成建筑的磚塊。標準單元工藝庫包括反相器、與門、寄存器、選擇器、全加器等多種基本單元,每一個標準單元對應著多個不同尺寸(W/L)、不同驅動能力的單元電路,基于這些基本單元即可構成復雜的數字芯片。

鑒于數字芯片的超大規模,已經很難通過全定制電路結構的方式來設計,而直接對商用工藝庫進行加固則是設計成本最低的選擇。

在制造廠商提供的標準單元庫基礎上結合抗輻照加固措施,使設計出來的輸入輸出單元庫具有抗輻照能力。加固之后的工藝庫需要晶圓廠流片驗證。

(3)設計冗余化

在抗輻照加固方法中,三模冗余(TMR)是最具有代表的容錯機制。同一時間三個功能相同的模塊分別執行一樣的操作,鑒于單粒子翻轉瞬時僅能打翻1路,“三選二”的投票器將會選出其余兩路的正確結果,增強電路系統的可靠性。三模冗余最顯著優點是糾錯能力強,且設計簡單,大大提高電路可靠性;但缺點也是顯而易見,會將電路增大3倍以上。

TMR的方法較為靈活,可根據性能需求在寄存器級、電路級、模塊級等任意層次設計TMR,部分EDA工具也可自動插入。

錯誤檢測與糾正電路(Error Detection And Correction,EDAC)也是一種簡單高效的防護單粒子翻轉的電路設計方法。EDAC 主要依據檢錯、糾錯的原理,通過轉換電路將寫入的數據生成校驗碼并保存,當讀出時靠對校驗碼進行判定,若只有一位出錯系統則自動糾正并將正確的數據輸出,同時還會進行數據的回寫從而覆蓋原來出錯的數據。

EDAC盡管糾錯能力強大,但是需要糾錯、譯碼電路,因此結構較為復雜,不適宜用于高性能的數據通道中。EDAC也可用于糾正多bit出錯的情況,但是糾錯電路會更加復雜。

權衡TMR和EDAC的優缺點,通常會在邏輯電路設計中使用TMR,在存儲器讀寫電路中使用EDAC。

(4)模塊獨立化

單粒子翻轉頻繁出現,必須考慮到翻轉發生之后不影響芯片的整體功能。因此,在架構設計中需要盡可能確保模塊之間保持較強的獨立性,盡可能具備獨立的復位功能,使得在單粒子打翻信號值之后,一方面出錯電路能夠盡快通過復位信號恢復正常;另一方面,確保其他正常工作的模塊不受影響。

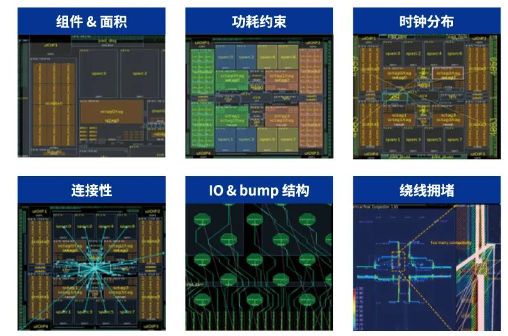

此外,還需增加異常檢測電路,發現異常即可對電路進行復位。小結雖然上述方法可以很好地防護單粒子翻轉效應,但是也給邏輯綜合、布局布線帶來很多困擾,在芯片物理實現過程中需要小心謹慎應對。

除上述方法外,還可引入Muller C單元、雙互鎖存儲單元結構(DICE)對晶體管級電路進行防護,也可在版圖階段使用環形柵替換條形柵。

總之,在航天領域中,芯片的性能并不是第一考慮要素,可靠性才是重中之重。只有芯片具備抗輻照能力,才能確保航天器正常運行。

責任編輯:lq

-

存儲器

+關注

關注

38文章

7641瀏覽量

166654 -

芯片設計

+關注

關注

15文章

1074瀏覽量

55511 -

航天器

+關注

關注

0文章

200瀏覽量

21197

原文標題:航天航空火了,可是你知道航天器中的宇航級芯片設計有什么特別之處?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PanDao:光學設計階段透鏡系統的可生產性分析

移動設備中的MDDESD防護挑戰:微型化封裝下的可靠性保障

多款CANFD芯片單粒子效應對比分析

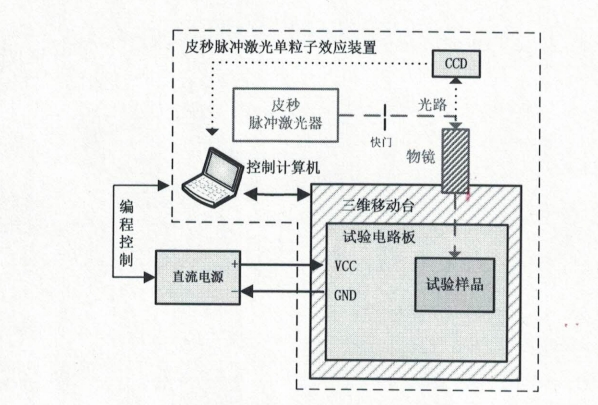

皮秒脈沖激光技術在AS32S601單粒子效應評估中的應用

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片如何設計

RISC-V雙核鎖步高性能抗輻照MCU芯片技術解析與應用

ASP4644四通道降壓穩壓器的抗輻照特性與應用驗證

軟錯誤防護技術在車規MCU中應用

CANFD芯片應用中關鍵功能和性能指標分析

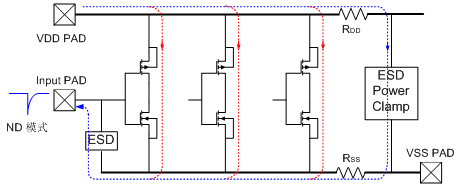

全芯片ESD防護網絡

在芯片設計階段如何防護“單粒子翻轉”

在芯片設計階段如何防護“單粒子翻轉”

評論