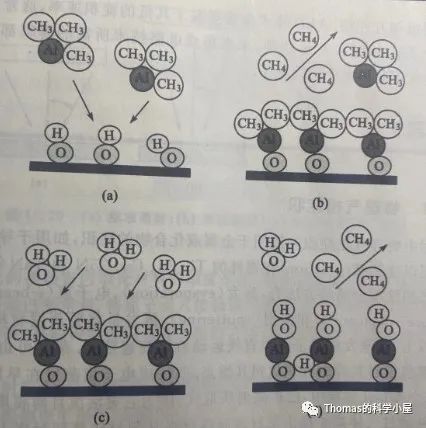

原子層沉積技術(shù)(Atomic layer deposition, ALD)近年在集成電路制程設(shè)備產(chǎn)業(yè)中受到相當(dāng)大的矚目,對(duì)比于其他在線鍍膜系統(tǒng),原子層沉積技術(shù)具有更優(yōu)越的特點(diǎn),如絕佳的鍍膜批覆性以及精準(zhǔn)的鍍膜厚度控制。隨著邏輯制程演進(jìn),原本二維的晶體管架構(gòu)已經(jīng)被三維的鰭魚式晶體管(FinFET)取代,關(guān)鍵尺寸(Critical dimension, CD)也由深次微米進(jìn)入到目前只有單一數(shù)字的納米大小,對(duì)于鍍膜的批覆性與厚度控制都有最嚴(yán)苛的要求,這讓原子層沉積技術(shù)成為先進(jìn)鰭魚式晶體管與將來(lái)環(huán)繞式柵極(Gate-all-around, GAA,或其他類似結(jié)構(gòu))晶體管制程最重要的鍍膜技術(shù)。

原子層沉積技術(shù)除了上述在集成電路制程上的應(yīng)用外,還有一個(gè)尚未沒(méi)被報(bào)導(dǎo)過(guò)的應(yīng)用: 可以將原子層沉積技術(shù)應(yīng)用在材料分析上,例如穿透式電子顯微鏡(Transmission electron microscope, TEM),用來(lái)制備一層在欲分析試片上的保護(hù)層。我們都知道,目前制備TEM試片(lamella)最常用的工具是聚焦離子束(Focused ion beam, FIB),F(xiàn)IB制備過(guò)程中,為了保護(hù)欲分析位置,一般的作法是在試片表面制備一層保護(hù)層,保護(hù)層常用的材料為碳系的膠類或是金屬,其保護(hù)層厚度大約介于數(shù)十納米到500納米之間,主要可以利用旋轉(zhuǎn)涂覆或是真空鍍膜系統(tǒng)制備。既然是用來(lái)保護(hù)欲分析的試片,所以在制備保護(hù)層過(guò)程中是不能改變?cè)嚻Y(jié)構(gòu),造成事后材料分析上的困擾,依據(jù)不同的制備機(jī)制(尤其是真空鍍膜),有兩項(xiàng)主要會(huì)影響欲分析試片結(jié)構(gòu)的因素需要被嚴(yán)肅看待,分別是溫度與離子轟擊效應(yīng)。對(duì)于較舊制程的試片(大于28納米),試片結(jié)構(gòu)與材料都相當(dāng)穩(wěn)定與堅(jiān)固,根據(jù)我們多年的經(jīng)驗(yàn),一般制備條件都不會(huì)改變或損傷欲分析試片的結(jié)構(gòu)。

當(dāng)分析的結(jié)構(gòu)為先進(jìn)制程的試片時(shí)(16納米以下),情況則變得相當(dāng)復(fù)雜,不但關(guān)鍵尺寸持續(xù)的微縮外,制程過(guò)程中也引進(jìn)了不少新材料, 例如,已經(jīng)開始應(yīng)用在7納米與未來(lái)環(huán)繞式柵極制程的深紫外光光阻(Extreme ultraviolet photoresist, EUV-PR)。根據(jù)國(guó)際期刊報(bào)導(dǎo),深紫外光光阻相當(dāng)脆弱,而且對(duì)于溫度與離子轟擊相當(dāng)?shù)孛舾校绻褂眠\(yùn)用在舊制程試片上的傳統(tǒng)方式制備保護(hù)層,欲分析試片的結(jié)構(gòu)很有可能因溫度或離子轟擊而損傷或變形,造成分析上的困難。另外,利用傳統(tǒng)制備方式對(duì)于較小關(guān)鍵尺寸的結(jié)構(gòu),如貫孔(via)或溝(trench),保護(hù)層的批覆性也會(huì)是個(gè)難題,小尺寸結(jié)構(gòu)開口處容易造成保護(hù)層材料堆積而縮口,產(chǎn)生孔洞或氣泡,這些人為的結(jié)構(gòu)都有可能會(huì)在FIB制備時(shí)產(chǎn)生不必要的刀痕,甚至在判讀TEM影像上造成困難。

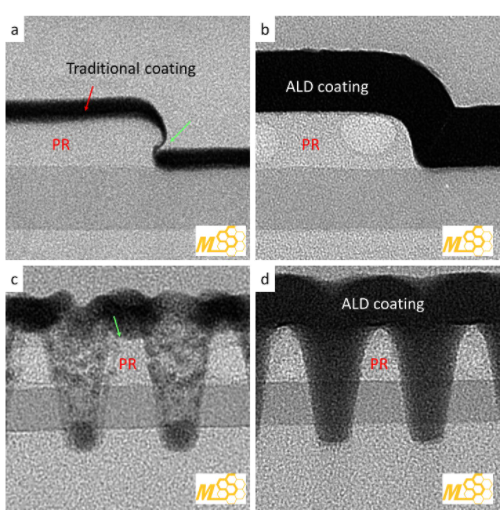

圖 1. 兩種光阻結(jié)構(gòu)分別利用兩種制備保護(hù)層方式的TEM照片。a與b為一組,c與d為另一組,其中a與c是使用傳統(tǒng)鍍膜方式制備保護(hù)層,b與d則是使用低溫真空原子層沉積技術(shù)制備。綠色箭號(hào)標(biāo)示處為光阻變形最明顯的區(qū)域。

為了解決上述這些問(wèn)題,泛銓科技跳脫舊有窠臼,提出一個(gè)革命性的想法,利用低溫真空原子層沉積技術(shù)取代傳統(tǒng)鍍膜,制備欲分析試片的保護(hù)層。原子層沉積技術(shù)有絕佳的鍍膜批覆性,即使是貫孔、溝、或甚至小關(guān)鍵尺寸的結(jié)構(gòu)都能輕易制備保護(hù)層,不會(huì)形成人為孔洞,為了避免FIB制備時(shí)造成的刀痕與TEM觀察時(shí)高能量電子束的轟擊損傷,保護(hù)層都會(huì)制備厚于50納米,這層保護(hù)層就像讓欲分析的脆弱結(jié)構(gòu)穿上無(wú)堅(jiān)不摧的鎧甲,有效抵御高能量離子束造成的損傷。針對(duì)試片表面的特性與分析目的,我們可以選用不同的保護(hù)層材料,但最重要的是,不管選用哪種材料,制備溫度都只比室溫高一些,遠(yuǎn)遠(yuǎn)比傳統(tǒng)制備方式低很多,此低溫制備對(duì)于最脆弱的深紫外光光阻尤其重要。有了上述這些利用低溫真空原子層沉積技術(shù)保護(hù)試片的做法,我們才能獲得精準(zhǔn)的材料分析結(jié)果。

圖1a與1c分別是利用傳統(tǒng)鍍膜方式制備保護(hù)層在兩種光阻結(jié)構(gòu)上的TEM照片,圖1b與1d為與1a與1c試片有相同結(jié)構(gòu)與材料但不同試片的對(duì)照組,,保護(hù)層制備是采用泛銓所提出的低溫真空原子層沉積技術(shù)概念。由這些圖可以清楚比較出,傳統(tǒng)鍍膜制備方式確實(shí)對(duì)光阻造成程度不一的損傷,尤其在綠色箭號(hào)標(biāo)示處,光阻變形的相當(dāng)嚴(yán)重。反觀使用低溫真空原子層沉積技術(shù)制備的試片(圖1b & 1d),光阻結(jié)構(gòu)并沒(méi)有明顯的變形。

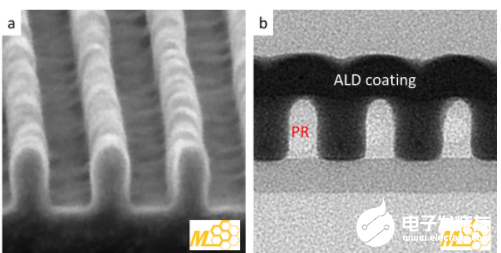

為了確認(rèn)低溫真空原子層沉積技術(shù)制備保護(hù)層確實(shí)不會(huì)造成光阻材料變形與損傷,我們利用高分辨率的掃描電子顯微鏡(Scanning tunneling microscope, SEM)來(lái)觀察在沒(méi)有任何制備下最原始的光阻試片狀況(圖2a),其對(duì)應(yīng)相同結(jié)構(gòu)與材料的TEM結(jié)果則呈現(xiàn)在圖2b中,比較這兩圖,可以清楚地看到SEM影像中所觀察到的結(jié)構(gòu)細(xì)節(jié)也都有出現(xiàn)在TEM影像中,這證明泛銓科技所提出使用低溫真空原子層沉積技術(shù)制備保護(hù)層的概念確實(shí)不會(huì)對(duì)脆弱材料造成損傷。

圖 2. a 高分辨率SEM照片,該光阻試片沒(méi)有經(jīng)過(guò)任何鍍膜處理,為原始表面照片。相同的試片再經(jīng)過(guò)低溫真空原子層沉積技術(shù)制備保護(hù)層后的TEM照片則呈現(xiàn)在b。比較兩圖可以清楚看到光阻結(jié)構(gòu)并沒(méi)有

低溫真空原子層沉積技術(shù)概念不但可以應(yīng)用在分析脆弱材料的保護(hù)層制備上,也可以將其應(yīng)用擴(kuò)展到故障分析與表面分析上,尤其如果試片的保護(hù)層需要在最嚴(yán)苛條件制備時(shí),低溫真空原子層沉積技術(shù)都能派上用場(chǎng)。泛銓科技所提出的這項(xiàng)革命性的概念也在2020年獲得專利,相信將來(lái)會(huì)有越來(lái)越多的材料會(huì)需要用到該技術(shù)。

編輯:hfy

-

集成電路

+關(guān)注

關(guān)注

5393文章

11632瀏覽量

363409 -

電子顯微鏡

+關(guān)注

關(guān)注

1文章

96瀏覽量

9904

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

集成電路封裝技術(shù)專題 通知

COMS工藝制程技術(shù)與集成電路設(shè)計(jì)指南

集成電路芯片類型和技術(shù)介紹

請(qǐng)問(wèn)一下8寸 原子層沉積設(shè)備ALD,單晶片。國(guó)內(nèi)設(shè)備大約在什么價(jià)位啊?

什么是集成電路?

北方華創(chuàng)微電子ALD設(shè)備以競(jìng)標(biāo)方式,進(jìn)駐上海集成電路研發(fā)中心

原子層沉積(ALD)工藝助力實(shí)現(xiàn)PowderMEMS技術(shù)平臺(tái)

晶圓制造的三大核心之薄膜沉積的原子層沉積(ALD)技術(shù)

專用集成電路技術(shù)是什么意思 專用集成電路技術(shù)有哪些

專用集成電路技術(shù)是什么意思 專用集成電路技術(shù)應(yīng)用有哪些

專用集成電路包括什么設(shè)備和設(shè)備 專用集成電路包括什么功能和作用

中微推出自研的12英寸原子層金屬鎢沉積設(shè)備Preforma Uniflex AW

原子層沉積(ALD, Atomic Layer Deposition)詳解

集成電路制程設(shè)備領(lǐng)域原子層沉積技術(shù)解析

集成電路制程設(shè)備領(lǐng)域原子層沉積技術(shù)解析

評(píng)論