一、時鐘相關概念

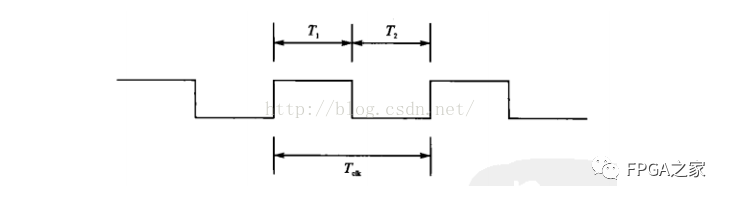

理想的時鐘模型是一個占空比為50%且周期固定的方波。Tclk為一個時鐘周期,T1為高脈沖寬度,T2為低脈沖寬度,Tclk=T1+T2。占空比定義為高脈沖寬度與周期之比,即T1/Tclk。

圖1 理想時鐘波形

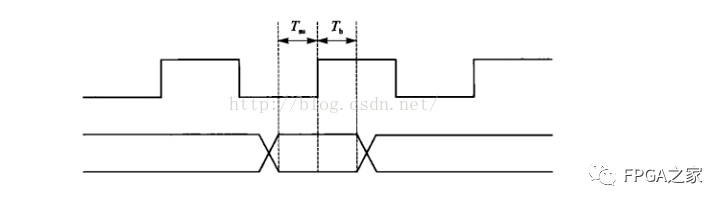

建立時間(Tsu):是指在時鐘上升沿到來之前數據必須保持穩定的時間;

保持時間(Th):是指在時鐘上升沿到來以后數據必須保持穩定的時間。如圖2所示。

圖2 建立和保持時間

一個數據需要在時鐘的上升沿鎖存,那么這個數據就必須在這個時鐘上升沿的建立時間和保持時間內保持穩定。

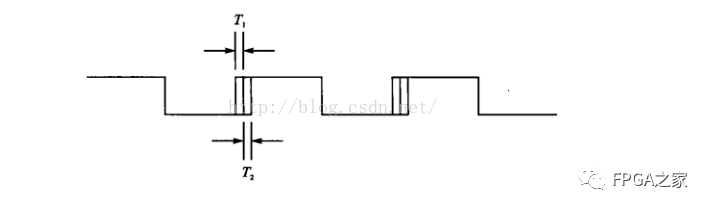

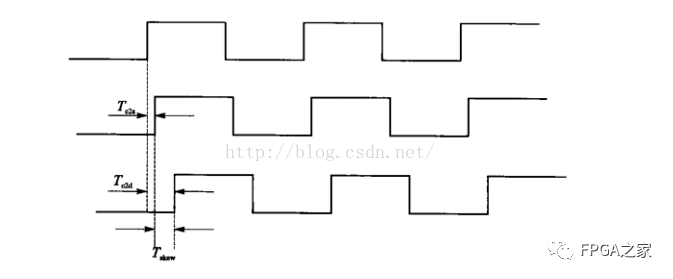

上面列舉的是一個理想的時鐘波形,而實際時鐘信號的分析要比這復雜得多。時鐘本身也具有一些不確定性,如時鐘抖動(jitter)和時鐘偏斜(sknew)等。時鐘的邊沿變化不可能總是理想的瞬變,它會有一個從高到低或者從低到高的變化過程,實際的情況抽象出來就如圖3所示,時鐘信號邊沿變化的不確定時間稱之為時鐘偏斜(clock skew)。再回到之前定義的建立時間和保持時間,嚴格的說,建立時間就應該是Tsu+T1,而保持時間就應該是Th+T2。

圖3 時鐘抖動模型

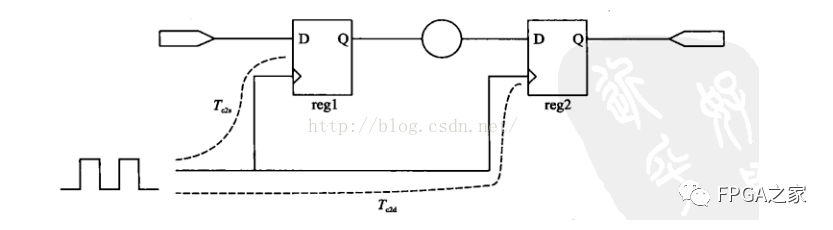

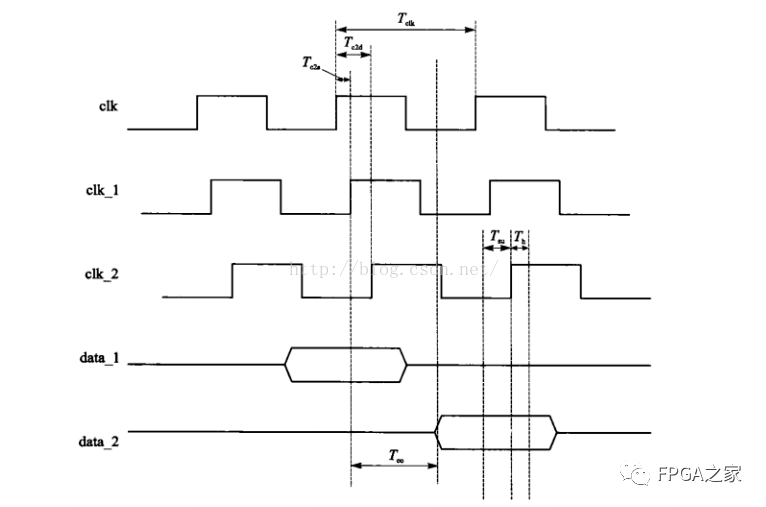

時鐘分析的起點是源寄存器(reg1),終點是目的寄存器(reg2)。時鐘和其他信號的傳輸一樣都會有延時。圖4中,時鐘信號從時鐘源傳輸到源寄存器的延時定義為Tc2s,傳輸到目的寄存器的延時定義為Tc2d,時鐘網絡延時就定義為Tc2d與Tc2s之差,即Tskew=Tc2d-Tc2s。

圖4 時鐘偏斜的寄存器傳輸模型

圖5是時鐘偏斜模型的波形表示。

圖5 時鐘偏斜的波形圖

clk是源時鐘,可以認為是一個理想的時鐘模型。clk_1是時鐘傳輸到源寄存器reg1的波形(延時Tc2s),clk_2是時鐘傳輸到目的寄存器reg2的波形(延時Tc2d)。data_1是數據在源寄存器reg1的傳輸波形,data_2是數據在目的寄存器reg2的傳輸波形。

圖6 數據與時鐘關系

原文標題:時鐘相關概念

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1641文章

21910瀏覽量

611668 -

數據

+關注

關注

8文章

7232瀏覽量

90711 -

時鐘

+關注

關注

11文章

1855瀏覽量

132637

原文標題:時鐘相關概念

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA時序約束之設置時鐘組

AD9547雙路/四路輸入網絡時鐘發生器/同步器技術手冊

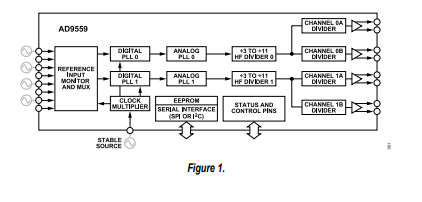

AD9559雙路PLL四通道輸入多服務線路卡自適應時鐘轉換器技術手冊

AD9554四路PLL、四通道輸入、八通道輸出多服務線路卡自適應時鐘轉換器技術手冊

FPGA中的時鐘相關概念

FPGA中的時鐘相關概念

評論