說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。高層次的概念代表的是硬件描述語言里面較高的抽象層次,只是隨著軟件硬件語言的共同發展,這樣的高抽象度的行為描述語言來到了C/C++/System C 這樣的層次。

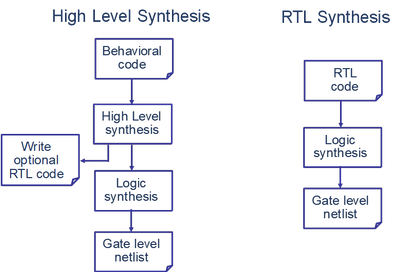

以下是南加州大學的DANIEL D.GAJSKI教授在1994年出版的期刊時對高層次綜合技術的描述[1]:High-level synthesis systems start with an abstract behavioral specification of a digital system and find a register-transfer level structure that realizes the given behavior. 下圖揭示了高層次綜合工作的基本流程,以及它于傳統的RTL綜合流程的對比。接下來將對行為描述,行為綜合,分析與優化三個主要子流程詳細描述。

1、行為描述

當我們把HLS技術的起點立為一種行為描述語言的時候,就需要軟件語言遵循特定的行為描述規范,并且剔除一些源自于軟件系統的的思維理念。雖然各個HLS工具的行為綜合都有自己的規范,但是關于動態內存分配的約束是共通的:禁止遞歸和動態指針。

函數遞歸意味著需要能夠動態生成電路模塊,動態指針是指運行時指針值可以任意變化的指針變量。 硬件不像軟件具有大塊的主內存,只有分布在局部的內存,所以比較適合并行實現。動態指針要求作為對象的訪問實體在運行時變化,超出了數字電路概念的一種功能。同樣,超出了數字電路概念的還有管理系統內存分配的系統調用函數等,在此不一一列舉了。

行為描述的概念,讓我們明確了針對數字電路特性使用高層次語言去編寫行為代碼的這一設計基本準則。而后探討代碼風格(coding style),系統優化都由這一基本準則延申。這就是為什么我們寫的C語言代碼會有一種介于硬件與軟件設計風格之間的根本原因。

行為描述的基本對象有輸入輸出接口,數據位寬,并行化描述等等,在 Vitis HLS 中有行為描述的規范和推薦的寫法等等,在展開介紹之前,我們先明確行為綜合的流程。

2、行為綜合

在行為綜合的過程中,行為描述中使用的變量,數組,運算分別用寄存器(FF,LUT),局部內存(URAM,BRAM,DRAM),運算器(DSP,ALU)等數字電路單元來實現。行為描述中的處理流程(順序執行, 分支,循環則以有限狀態機(FSM)的形式來呈現。通過分析行為描述,可以將運算的依賴關系表示為數據流圖(DFG),將控制流程表示為控制流圖(CFG)。

分析到這里兩個非常重要的行為綜合概念出現了,就是調度(scheduling)和綁定(Binding).

根據數據流圖和控制流圖來決定運行順序和運行速度的過程稱為調度。

將變量和運算映射到寄存器或運算器的過程稱為綁定。

下圖簡潔明了地介紹了從C語言設計到導出RTL設計過程中,依據HLS庫和用戶指令進行調度和綁定的過程。

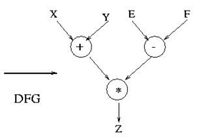

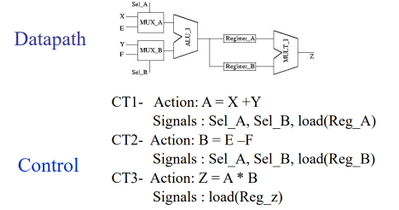

這里我們使用一個非常簡單的例子描述一下行為綜合的過程

(1) Compilation and Transformation 將一個行為描述代碼的轉化為數據流圖DFG

數據流圖由很多數據節點組成,最重要的是表達出了各個節點上數據的依賴關系,這是后面調度和綁定的基礎。

在這個步驟中,代碼風格是一個比較關鍵的因素。HLS在轉化過于繁復高層次語言表達的時候,極個別情況會無法識別一些嵌套非常深的軟件算法,也會增加編譯時間. 所以盡量簡潔,邏輯明晰的硬件友好代碼會提升開發效率。

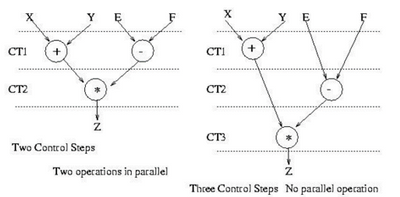

(2) Scheduling 調度

在數據流圖中,我們看到XY和EF數據之間沒有依賴,他們可以選擇在同一個Control Step里面并行執行,或者在兩個ST里面順序執行.

這個過程中調度的并行性由HLS編譯器,用戶指令共同作用影響著,比如編譯器會主動發現可以并行的優化點自動優化,也會誤以為某些表達式存在數據依賴無法并行優化等,所以仍需要用戶加入指令說明情況。 當然追求更高的并行性對資源也有更大的需求,所以并不是一切調度都以最大并行性為目標。

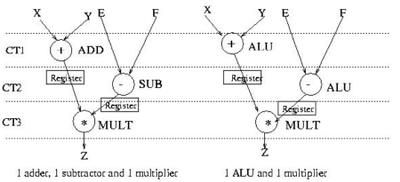

(3) Binding

在早期的HLS研究中,Allocation 和 Binding 是分開的兩個步驟。其中Allocation 鎖定了資源的數量和類型,Binding完成了運算到資源的映射。現在我們就統稱這些操作在Binding步驟完成。早期FPGA中的含有一種集成的算法單元ALU,如今DSP這樣的硬件模塊已經包含了ALU和乘法器模塊等等。

下圖基于早期的ALU單元揭示了Binding 的可能性, 將加減法操作映射到寄存器還是ALU模塊,呈現了兩種不同的方案.

以下是選擇了使用一個ALU、兩個寄存器、一個乘法器的綜合結果。對于既定的調度方案,可以通過行為綜合來生成相應的狀態機。HLS在行為綜合的過程中,除了達到算法的基本功能,更重要的是選擇不同的綁定和調度方案在資源、性能、吞吐量等各個指標中做權衡和取舍。

3、分析和優化

電路的規模和運行時間存在權衡關系,所以產生最優化的RTL描述需要開發者提供大致的優化方針,甚至是明確的優化仿真。

因此Xilinx的高層綜合工具提供了一系列性能評估的功能和向編譯器指向優化方式的途徑。針對行為描述進行行為綜合,可以獲取如下多種性能指標:

?面積(電路規模):根據資源實施設計所需的硬件資源量

在FPGA中可用,包括查找表(LUT),寄存器,Block RAM和DSP48。

?延遲:函數計算所有輸出值所需的時鐘周期數。

?初始化間隔(II):函數可以接受新輸入數據之前的時鐘周期數。

?循環迭代延遲:完成循環的一次迭代所需的時鐘周期數。

?循環啟動間隔:下一次循環迭代開始處理數據之前的時鐘周期數。

?循環延遲:執行循環所有迭代的循環數。

這些性能指標的行為綜合結果都會在HLS工具的報告中指出,開發者需要找出性能瓶頸或者性能過剩的部分。針對循環的優化方式由流水線(pipeline)或展開(unroll). 此外還有指示運算器的并行或共享,指示數組的拆分(partition)和訪問調度,指示功能函數的內聯(inline)等等。這些優化指令相互作用,需要從全局出發確定優化指令。

當進行詳細的優化指令也無法達到預期的指標時,就需要考慮代碼本身的優化。這就需要開發者在設計模塊(函數、循環等)時靈活運用并行、流水線等架構,并在充分理解行為綜合機制的基礎上編寫更容易生成高效硬件行為描述的代碼。

4、接口連接

行為描述后的模塊需再和其他模塊群整合,所以就過渡到考慮如何設計端口類型與其他IP進行實例化連接了。

在RTL設計中,數據通過端口進出IP,這些端口可以使用固特定的IP接口協議(AXI-Master/ AXI-lite)來進行操作. 進出IP的每一條數據,都應該將其指定為主源文件中的一個獨立函數實參。該函數實參將會被綜合為硬件RTL中的一個端口。

數據端口的類型大概分為以下三個大類:

1、直接讀寫數據值的寄存器式

2、按照隊列收發數據的數據流式

3、指定地址進行讀寫的內存總線模式

不同接口能夠為不同設計提供最優性能,比如數據流接口更適合于數據驅動型應用,為了更高效地傳輸數據經常在發送和接收雙方之間插入FIFO緩沖器。這樣的使用規則為FPGA硬件開發者所熟知,軟件開發者仍需要深入理解。

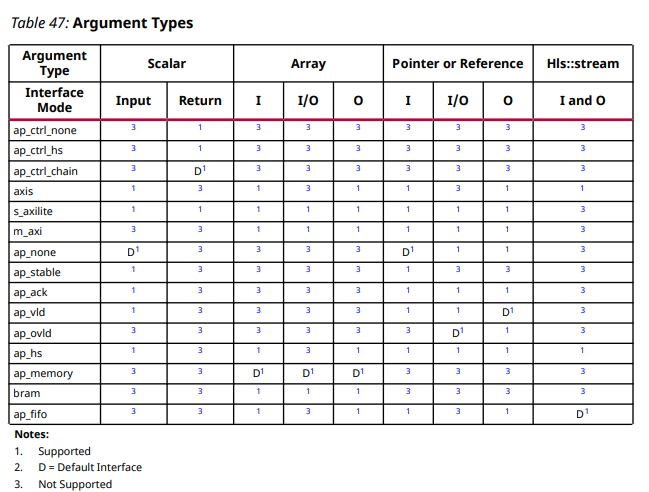

下表為Vivado Design Flow 下的接口類型已經變量類型的關系。 其中標量,數組,指針和hls數據流格式對應的默認接口模式標注為D,支持的接口標注為1,不支持的接口標注為3, ,是一個重要的設計參考表格。

本章節通過揭示HLS工作的基本概念讓大家對技術有了宏觀上的理解。這一份宏觀上的理解雖然淺顯易懂,但是它將基于CPU的架構的軟件程序與在高層次綜合這項技術上行為描述語言做出了明顯的區分。賽靈思的HLS官方手冊中,對文中提到了端口協議,優化指令,數據類型等都有非常詳細的解釋。本系列以后的文章將適合HLS加速的應用場景出發,重點講解數據傳輸的架構優化以及如何編寫高效的硬件描述C代碼。

寫在最后:

"為現場可編程門陣列的高層次綜合建立的算法基礎”曾獲IEEE計算機分會年度技術成就獎的叢京生教授在ASPDAC 會議上對高層次綜合技術未來的展望:

一個性能優于CPU的優秀的高層次綜合設計的HLS C/C++代碼可能會很長,甚至和原始代碼相比面目全非。類似這樣對于一個軟件程序員進行常年的HLS C/C++代碼的訓練并不是可推廣和有效率的模式。但是在可定制計算技術的長河中,科學家和研究者們希望無論軟硬件工作人員,都只要經過一些基本優化理論的訓練就可以通過寫軟件代碼得到優于通用CPU的設計。這樣大家才能廣泛體會到可定制計算能夠帶來的好處[4]。

審核編輯:何安

-

C++

+關注

關注

22文章

2116瀏覽量

74612

發布評論請先 登錄

【「零基礎開發AI Agent」閱讀體驗】+ 入門篇學習

北大攜智元機器?團隊提出OmniManip架構

使用HLS流程設計和驗證圖像信號處理設備

從Level1 Model到Level3 Modle來感受器件模型是如何開發的

《大話芯片制造》閱讀體會分享_1

求助,ISO7721用于485隔離遇到的疑問求解

云知聲榮獲上海市優秀專家工作站稱號

新思科技再獲臺積公司多項OIP年度合作伙伴大獎

高厚徑比HDI板電鍍能力研究

雙閉環PID先調內環還是外環

nlp邏輯層次模型的特點

西門子推出Catapult AI NN軟件,賦能神經網絡加速器設計

西門子推出Catapult AI NN軟件

西門子推出Catapult AI NN軟件,加速神經網絡在ASIC和SoC上綜合

各類常用混頻器的高層次設計和優缺點

高層次綜合技術(High-level synthesis)的概念

高層次綜合技術(High-level synthesis)的概念

評論