近日,荷蘭的光刻機制造商阿斯麥(ASML)發布2020年度財報,全年凈銷售額達到140億歐元,毛利率達到48.6%。ASML同時宣布實現第100套極紫外光刻(EUV)系統的出貨,至2020年年底已有2600萬片晶圓采用EUV系統進行光刻。隨著半導體技術的發展,光刻的精度不斷提高,2021年先進工藝將進入5nm/3nm節點,極紫外光刻成為必修課,EUV也成為半導體龍頭廠商競相爭奪采購的焦點。未來,極紫外光刻技術將如何發展?產業格局如何演變?我國發展半導體產業應如何解決光刻技術的難題?

半導體大廠

競相購買EUV

在摩爾定律不斷挑戰物理極限的當下,半導體先進工藝領域的競爭形勢,用“得EUV者得先進工藝”來形容并不為過。臺積電、三星電子等廠商均加速了導入EUV的進程。也是這個原因,EUV正在成為半導體巨頭在先進工藝領域爭奪優勢地位的焦點。

近期,三星電子與ASML高層互訪消息頻出。2020年10月,三星電子副會長李在镕訪問ASML,與ASML CEO Peter Wennink、CTO Martin van den Brink進行會談。2020年年底又傳出Peter Wennink回訪三星電子的消息。

有業界人士指出,這樣頻繁的互訪,核心當然在于EUV設備。三星電子希望ASML提供更多的EUV設備,同時希望ASML協助三星電子更加順利地使用已經購買的EUV。據了解,ASML 2021年EUV產能約為45~50臺。而臺積電就搶下當中的30臺,剩下的才由三星、英特爾及SK海力士等競爭對手瓜分。如此一來,三星電子勢必在2021年EUV設備數量上輸給臺積電。三星電子此前提出“半導體愿景2030計劃”,計劃于2030年在晶圓代工領域趕超臺積電。這是三星高層親自出訪ASML的主要原因。

事實上,半導體邏輯制程技術進入到7納米以下后,由于線寬過細,需要使用EUV作為曝光媒介。全球當前有能力并且有意愿進入7納米世代的晶圓廠僅剩臺積電、三星和英特爾,加之EUV設備供給有限,ASML便成為三大半導體巨頭爭相拉攏的重要對象。

5nm/3nm

極紫外光刻成為必修課

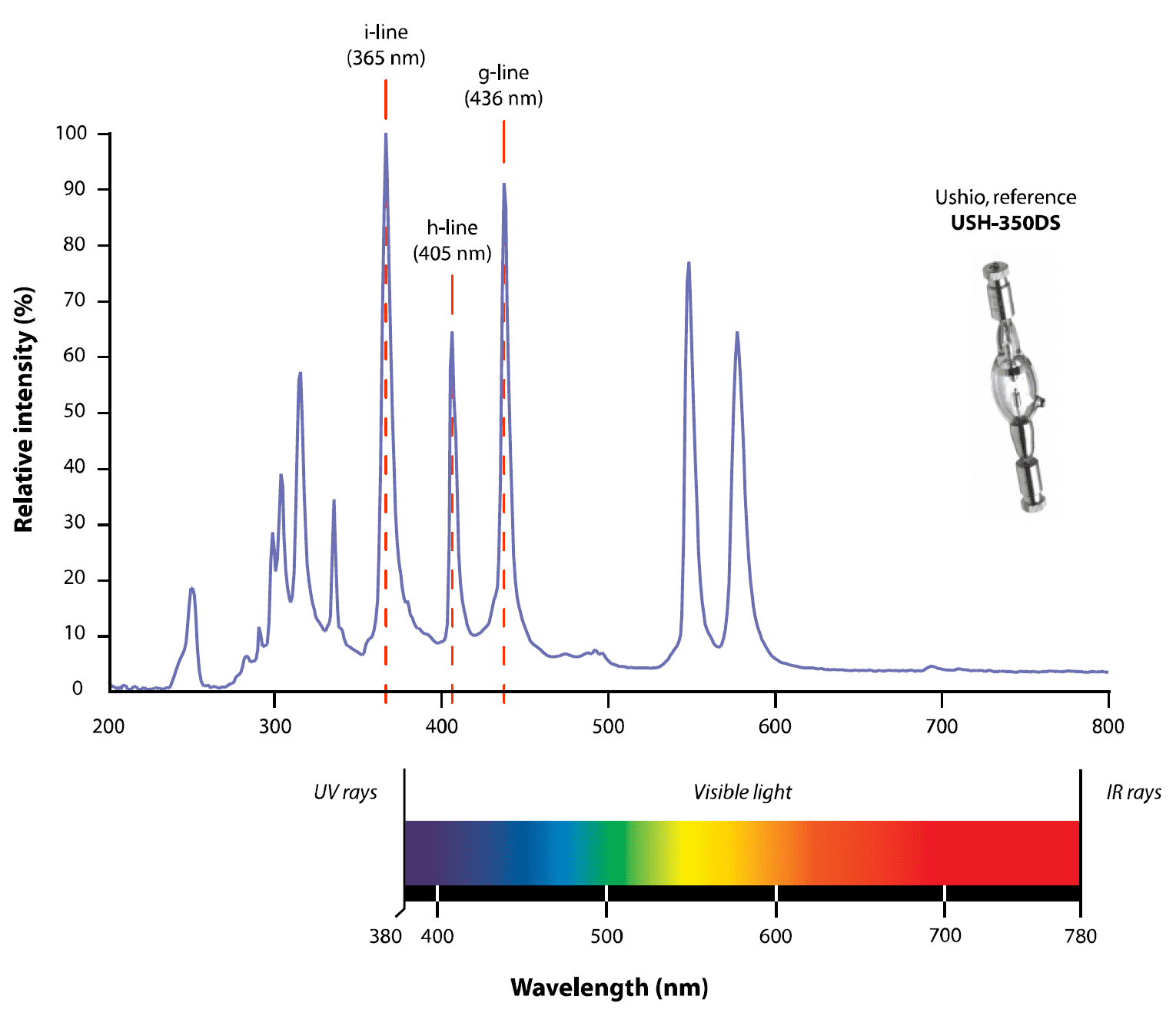

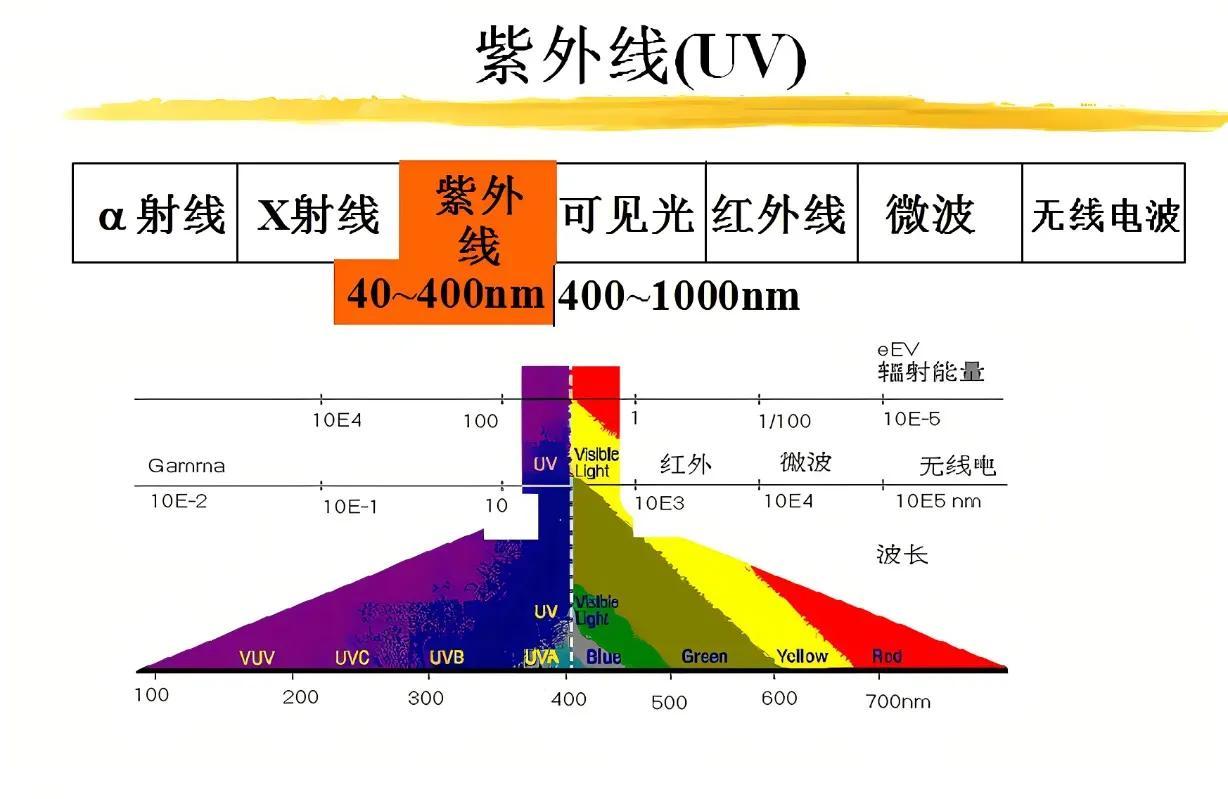

隨著半導體技術的發展,光刻的精度不斷提高,已由微米級、亞微米級、深亞微米級,細化到當前的納米級,曝光光源的波長也由436納米(G線)、365納米(Ⅰ線),發展到248納米(KrF)、193納米(ArF),再到13.5納米(EUV)。

EUV是線寬突破10納米,甚至之后的7納米、5納米、3納米工藝的關鍵。華創證券調研報告顯示,半導體芯片生產的難點和關鍵點在于將電路圖從掩膜上轉移至硅片上,這一過程需要通過光刻來實現。光刻的工藝水平直接決定芯片的制程水平和性能水平。芯片在生產中需要進行20~30次的光刻,耗時占到IC生產環節的50%左右,占芯片生產成本的1/3。如果采用EUV,晶圓廠可以減少將芯片設計縮小所遇到的光學麻煩,并在此過程中省去一些多重圖形曝光(multi-patterning)步驟,在理想情況下能夠節省成本和時間,提高良品率。也正是這個原因,盡管ASML的EUV售價高達1.2億美元,三星和臺積電等廠商依然積極采購。

臺積電在日前舉行的法說會上宣布,2021年主要用于設備采購的資本支出約為250億至280億美元,較2020年的172億美元增長了45%~62%。臺積電首席財務官黃仁昭表示,為應對先進工藝與特殊工藝技術發展,并順應客戶需求的增長,公司將上調2021年資本支出,其中80%將用于3nm、5nm及7nm等先進工藝。

資料顯示,臺積電的5納米節點相比7納米節點,可以使性能提高15%(在相同的功率和復雜度下),功耗降低30%(在相同的頻率和復雜度下),晶體管密度最高提高1.8倍(并非適用于所有結構)。此外,5納米節點將在十層以上的設備上使用EUV,這使臺積電減少了掩膜的使用數量,減少了多重圖形曝光的使用次數。

未來,先進工藝將繼續推進,至3納米、2納米,甚至是1納米。屆時,EUV將發揮更大的作用。半導體研究機構imec CEO兼總裁Luc Van den hove指出,imec通過與ASML通力合作研發并實現新一代高解析度EUV光刻技術(高NA EUV Lithography),將促使摩爾定律繼續發揮作用,即使工藝微縮化達到1納米后,摩爾定律也會繼續適用。

存儲芯片

下一個EUV大戶

不僅邏輯芯片制造工藝需要使用EUV設備,未來美光、SK海力士等存儲芯片大廠在量產DRAM時也將采用EUV設備。半導體專家莫大康指出,存儲器主要分為兩種:一種是DRAM,另一種是3D NAND。3D NAND目前的競爭主要集中在層數上,雖然也需要線寬的微縮化,但需求不那么迫切。而DRAM存儲器則不同,如果做到1z(12~14nm)以下,就有可能需要用到EUV光刻機。屆時,存儲器廠商訂的EUV設備將有大的爆發。

據悉,三星電子目前已經嘗試將EUV應用于1z DRAM的生產當中。2020年8月,三星電子宣布在平澤工廠新建的第二座生產線開始生產16Gbit LPDDR5移動DRAM。三星電子采用EUV生產的第四代10納米級別的DRAM晶圓出貨量達到100萬個。

在內存業內,目前的代際劃分是1x、1y、1z、1α和1β。SK海力士表示,正在為使用EUV的DRAM的大規模生產做準備。SK海力士計劃從2021年起將EUV應用于1αDRAM,2022年將EUV應用于1βDRAM。SK海力士規劃升級M14晶圓廠的設備,同時在即將啟用的新廠——M16晶圓廠中安裝EUV光刻系統。

美光也在布局對EUV的使用。有消息稱,美光正在尋找管理EUV設備的工程師。美光科技高級副總裁兼移動產品事業部總經理拉杰·塔魯里認為,是否采用EUV考量的關鍵在于芯片生產的成本和效率。“我們現在使用的多重圖形曝光技術相比使用EUV在成本和效率上的優勢更加明顯。現在我們已經推進到1α節點,我們覺得做到1β、1γ節點,現有的多重圖形曝光技術在成本上都會更加有優勢。但是在1γ之后,我們有可能會嘗試采用EUV。我們會進行成本效率分析,如果證明成本效率更優就會考慮采用。當然,前期我們會投入資金進行相關工藝的探索和開發。”

極紫外光刻產業

不僅只有EUV

光刻機供應商除ASML之外,還有日本廠商尼康和佳能。隨著EUV變得越來越重要,ASML的優勢正變得越來越明顯。佳能和尼康僅能在“深紫外線”(DUV)光刻系統上與之競爭。可即使在DUV領域,ASML也擁有62%的市場份額。

然而,極紫外光刻產業又并不僅僅只有EUV光刻機。根據半導體專家莫大康的介紹,與EUV相關的還包括光掩膜缺陷檢測和涂覆顯影等周邊設備,以及光刻膠等關鍵材料。光掩膜缺陷檢測設備可檢測光掩膜中存在的缺陷,如果承載原始電路的光掩膜存在缺陷,則芯片的缺陷率將相應增加。因此該設備也十分重要。日本Lasertec是這一領域的主要制造商。Lasertec公司的經營企劃室室長三澤祐太朗指出:“隨著微縮化的發展,在步入2納米制程時,DUV的感光度可能會不夠充分。”采用EUV光源的檢測設備的需求有望進一步增長。

EUV涂膠顯影設備用于將特殊的化學液體涂在硅片上作為半導體材料進行顯影。作為光刻機的輸入(曝光前光刻膠涂覆)和輸出(曝光后圖形的顯影),涂膠/顯影機的性能直接影響到細微曝光圖案的形成,其顯影工藝的圖形質量和缺陷控制對后續諸多工藝(諸如蝕刻、離子注入等)圖形轉移結果也有著深刻的影響。東京電子是該領域的主要供應商。東京電子的河合利樹社長指出,如果EUV的導入能促進整個工序的技術進步的話,與EUV沒有直接聯系的工序數也會增加。國內設備廠芯源微日前表示,公司前道涂膠顯影機與國際光刻機聯機的技術問題已經攻克并通過驗證,可以與包括ASML、佳能等國際品牌,以及上海微電子(SMEE)的光刻機聯機應用。

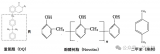

光刻膠對分辨率、對比度、敏感度,以及粘滯性黏度、粘附性等要求極高。目前全球光刻膠主要企業有日本合成橡膠(JSR)、東京應化(TOK)、住友化學、信越化學、美國羅門哈斯等,所占市場份額超過85%,市場集中度非常高。目前,中國已經可以量產G線、I線、KrF三大類光刻膠。南大光電計劃通過3年的建設、投產及實現銷售,達到年產25噸193nm(ArF干式和浸沒式)光刻膠產品的生產規模,未來將攻關EUV光刻膠。

解決光刻難題

從非核心開始起步

我國發展半導體產業,光刻技術是繞不開的課題,以國內目前薄弱的基礎,短期內攻克EUV設備并不現實。對此,莫大康指出,高性能光刻技術對中國企業來說成本高昂,但是其戰略意義不容忽視。中國要推進完整的光刻工業體系的發展,只能采取從低到高的策略,比如193nm深紫外ArF干式光刻機、浸沒式光刻機,以及周邊設備材料等,EUV是整套體系中最困難的一塊。

“要實現強大的功能,EUV就必須克服電能消耗以及光源等因素的影響。”中國電子科技集團公司第四十五研究所集團首席專家柳濱表示,EUV雖然售價超過了一億美元,但是高額的價格并不是它最大的問題。EUV最大的問題是電能消耗。其電能消耗是傳統193nm光刻機的10倍,因為極紫外光的波長僅有13.5nm,投射到晶圓表面曝光的強度只有光進入EUV設備光路系統前的2%。在與7nm成本比較中,7nm的EUV生產效率在80片/小時的耗電成本將是14nm的傳統光刻生產效率在240片/小時的耗電成本的一倍,這還不算設備購置成本和掩膜版設計制造成本。

除了電能以及光源,光刻膠也是EUV技術另一個需要面對的問題。據專家介紹,光刻膠本身對于光的敏感度就十分高,但是對于不同波長的光源,光刻膠的敏感度也有差異,這就對EUV光刻機產生了一些要求。光刻機選擇的波長必須和光刻膠對應的波長處于同一個波段,這樣才能提升光刻膠對于光源的吸收率,從而更好地實現化學變化。

莫大康表示,極紫外光刻雖然領先,但正因如此也存在許多需要改進的空間。因此,國內廠商先在DUV等領域站住腳跟,從周邊設備與材料切入,逐步解決產業中存在的問題,把產業做扎實,不失為一個有效的策略。

責任編輯:tzh

-

芯片

+關注

關注

459文章

51855瀏覽量

432701 -

半導體

+關注

關注

335文章

28266瀏覽量

229057 -

晶圓

+關注

關注

52文章

5066瀏覽量

128932 -

EUV

+關注

關注

8文章

609瀏覽量

86663

發布評論請先 登錄

相關推薦

納米壓印光刻技術旨在與極紫外光刻(EUV)競爭

193nm紫外波前傳感器(512x512高相位分辨率)助力半導體/光刻機行業發展!

最新CMOS技術發展趨勢

紫外光源的分類

紫外能量計的技術原理和應用場景

日本大學研發出新極紫外(EUV)光刻技術

n型硅太陽能電池組件產品的紫外光衰(UVID)及可靠性評估

友思特分享 完美聚光:用于光刻曝光的UV-LED光引擎

買臺積電都嫌貴的光刻機,大力推玻璃基板,英特爾代工的野心和危機

光刻機的基本原理和核心技術

未來極紫外光刻技術將如何發展?產業格局如何演變?

未來極紫外光刻技術將如何發展?產業格局如何演變?

評論