一、概述

IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發器設計的,用于評估和監控GTX收發器。IBERT包括在FPGA邏輯中實現的模式生成器和檢查器,以及對端口的訪問和GTX收發器的動態重新配置端口屬性,還包括通信邏輯,以允許設計在運行時通過JTAG進行訪問。

IBERT工具用于對Xilinx FPGA芯片的高速串行收發器進行板級硬件測試。通過IBERT可以獲取誤碼率,觀察眼圖,調節串行收發器的參數,從而有助于判斷可能存在的問題,便于驗證硬件的穩定性和信號完整性。

二、測試原理

GTX接收和發送方向均由PMA和PCS兩部分組成,PCS提供豐富的物理編碼層特性,如8b10b編碼、時鐘校準等功能,PMA部分為模擬電路,提供高性能的串行接口特性,如預加重、均衡等功能。GTX同時還提供動態配置接口,用于動態的修改GTX的配置。

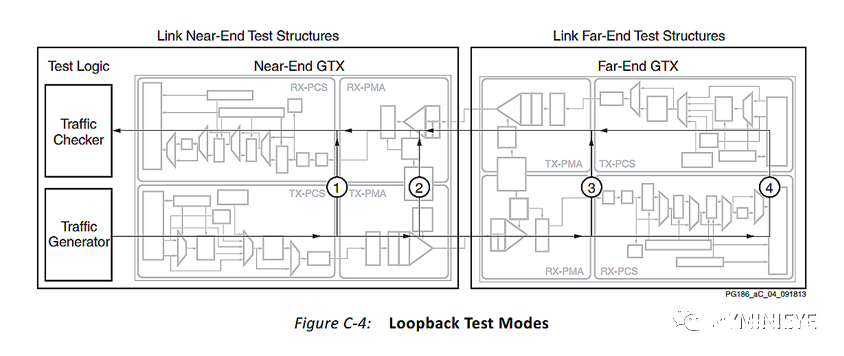

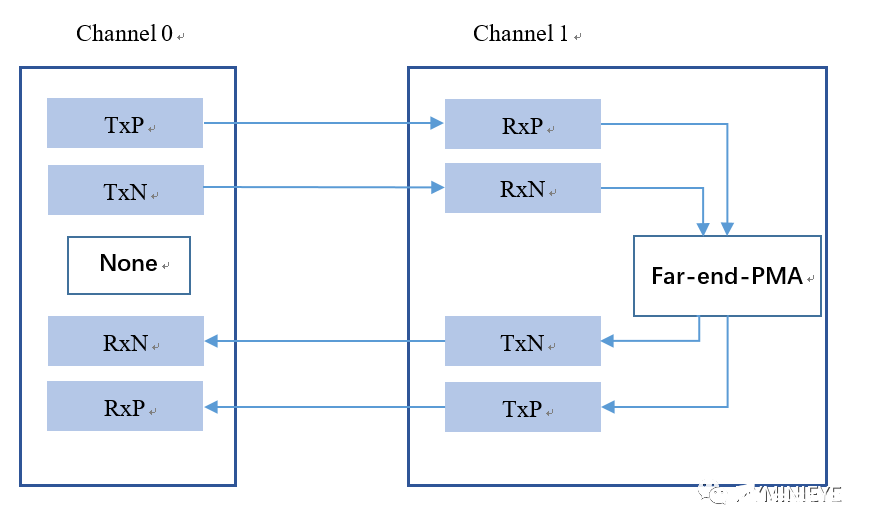

IBERT 工具的環回模式有近端PCS環回測試(路徑①),數據流僅通過近端GTX的PCS部分,可用于驗證近端GTX中PCS收發雙向的設置;近端PMA環回測試(路徑②,數據流通過近端GTX的PCS、PMA,可用于驗證近端GTX收發雙向的設置;遠端PMA環回測試(路徑③),數據流通過近端GTX的PCS和PMA,遠端的GTX的PMA部分,通過兩個GTX之間的物理連線,驗證兩個GTX之間物理聯系的可靠性,以及驗證兩個GTX的PMA部分設置的正確性;遠端PCS環回測試(路徑④)驗證近端收發器和遠端收發器的通信狀況;以及None無環回模式即通過外部連接發送和接收。

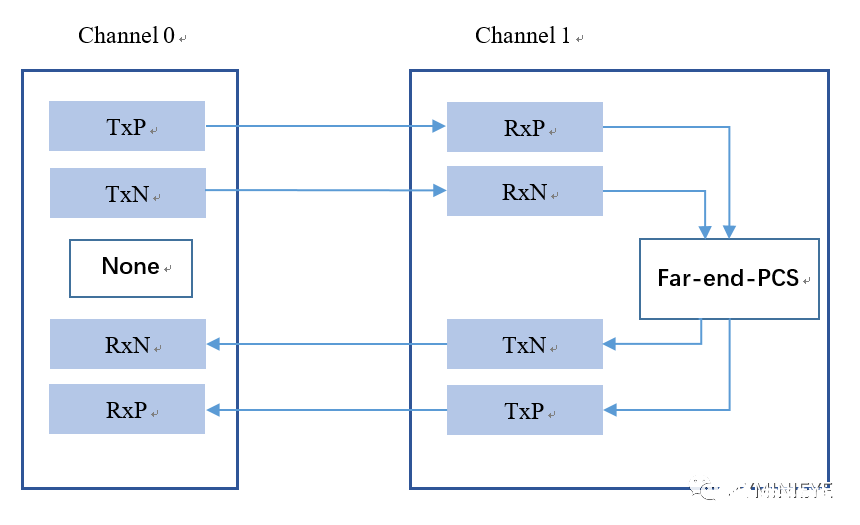

遠端PCS或PMA環回測試時板卡下載IBERT核生成的bit文件,通過兩個通道上的Tx和Rx接口互相連接,其中一個通道上的模式設置為Far_End_PMA或Far_End_PCS模式,另一個通道設置為默認的None模式并監測誤碼率。

Vivado中IBERT默認模式為None模式,收發器通過外部連線由外部環回進行自收自發而實現。可將同一組收發器的TX和RX進行短接,在RX接收端接收TX發送的數據后,通過比對發送和接收的數據,從而得出接收端誤碼的統計值。

三、測試過程

1、器件支持速率說明

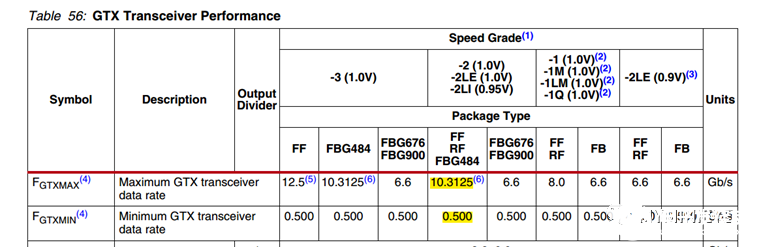

GTP , GTX , GTH都是串行收發器,區別在速率不一樣,在不同的器件中叫的名字不同而已,由于在vivado創建工程時選擇對應的器件型號,使用IBERT時會自動根據器件型號檢查所選的線速是否在器件支持的線速范圍以內。

在示例中使用器件型號為xc7z030ffg676-2,在數據手冊中根據7系列-2的速度等級和FF封裝可查到該器件GTX的數據率范圍為0.5~10.3125G,因此在測試的過程測試速率應在此范圍內。(參考文檔DS182)

2、IBERT IP核配置

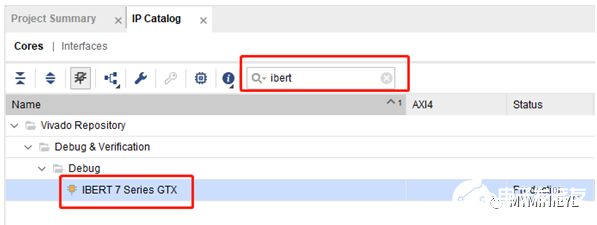

(1)首先打開vivado,新建工程后從IP Catalog找到IBERT并雙擊打開;

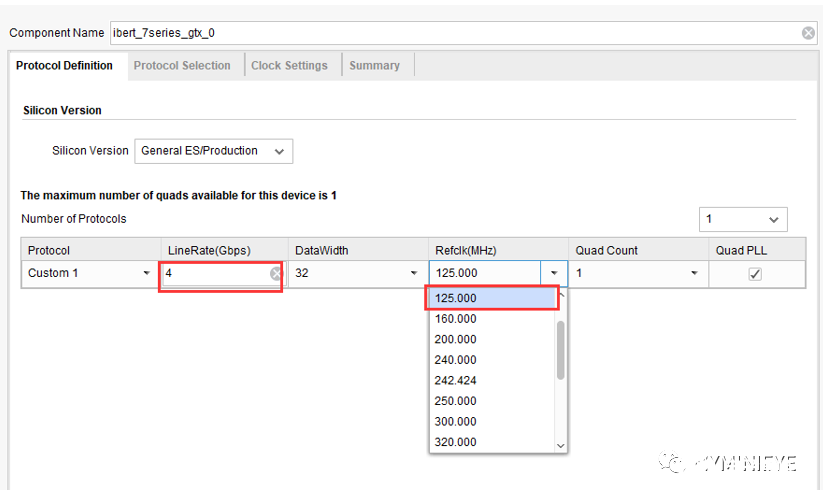

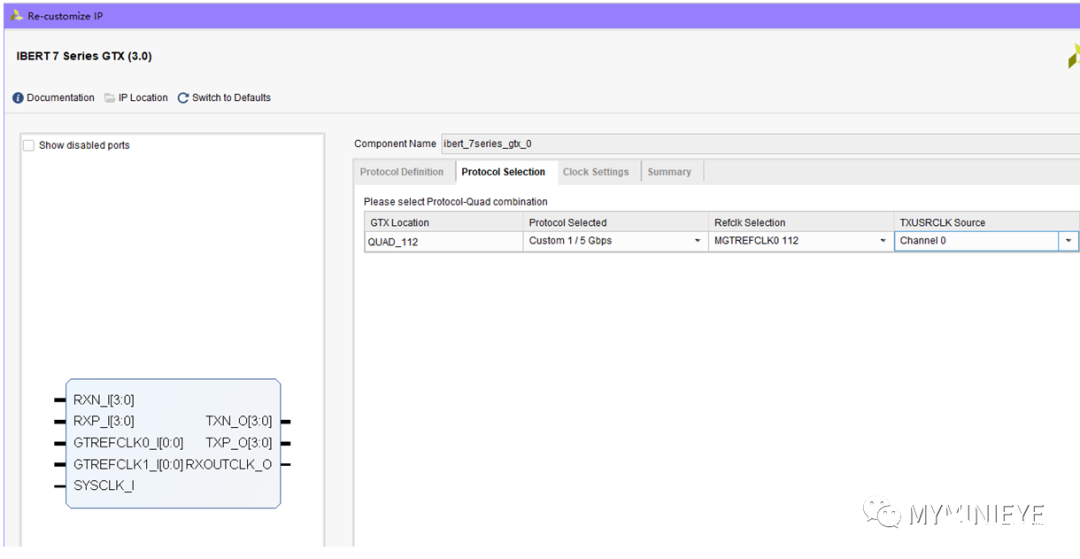

(2)IBERT測試協議選擇Custom1,GTX參考時鐘選擇頻率為125MHz,在配置的過程中,Refclk可選的頻率是由LineRate決定,由于在板卡上Refclk已固定為125MHz,因此測試所選擇的線速應支持125MHz的參考時鐘。(以4G線速為例)

(3)在開發板中,差分時鐘與MGTREFCLK0112連接,因此參考時鐘選擇MGTREFCLK0112。

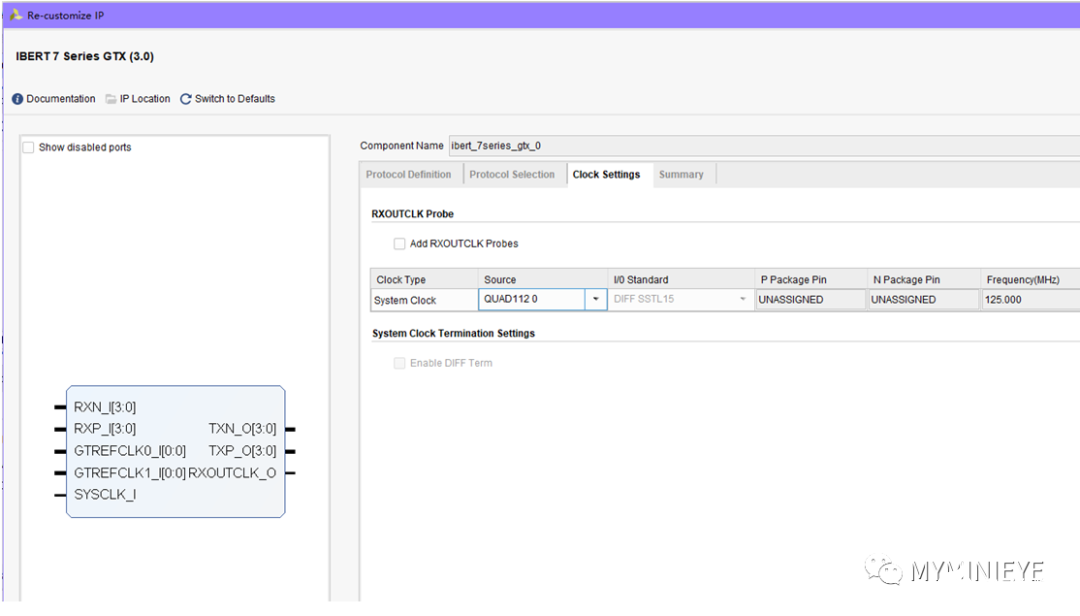

(4)將GTX輸入的125MHz的時鐘同時作為IBERT內部邏輯的工作時鐘,這樣就可以不使用額外的外部時鐘。

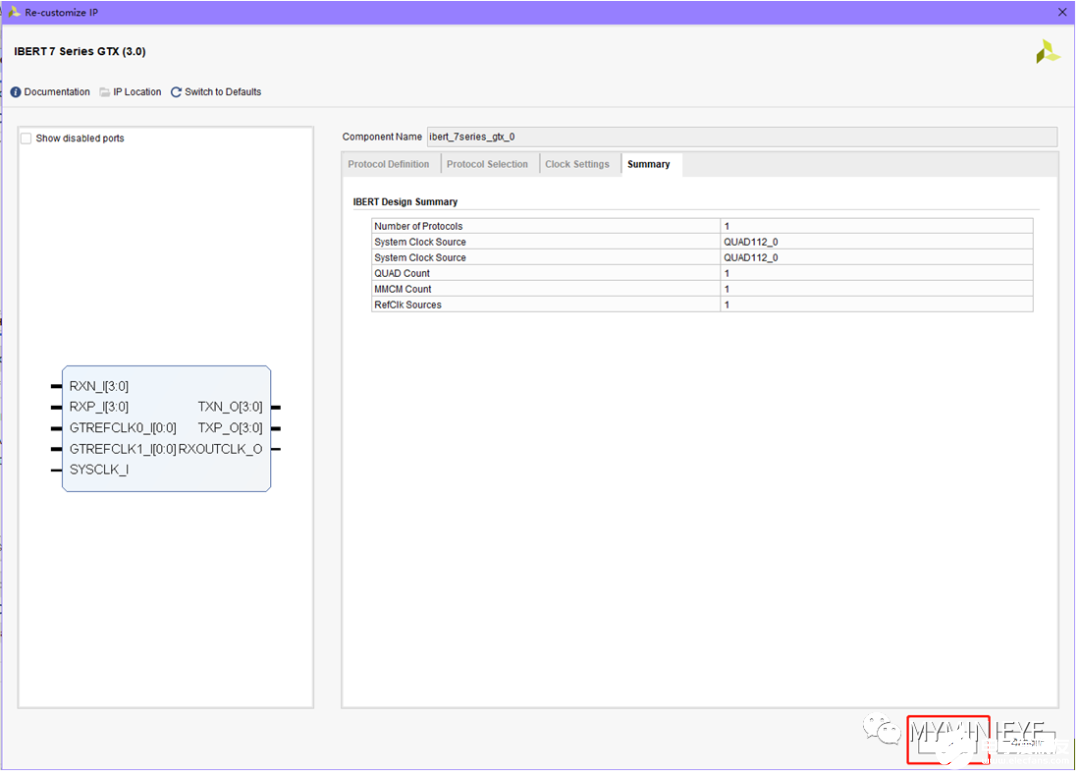

(5)配置結束后點擊OK

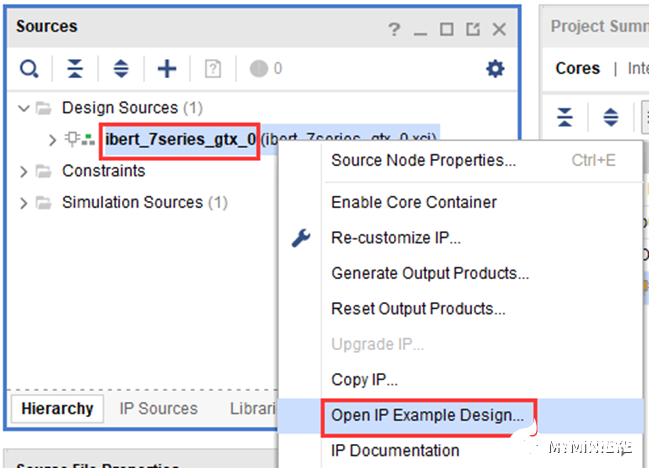

(6)完成配置后,右擊打開exampledesign工程

(7)打開exampledesign工程后,經過Synthese、Implementation,生成bit文件即可進行燒錄。

3、測試

(1)近端PCS或PMA環回測試(Near-End PCS/PMA loopback)

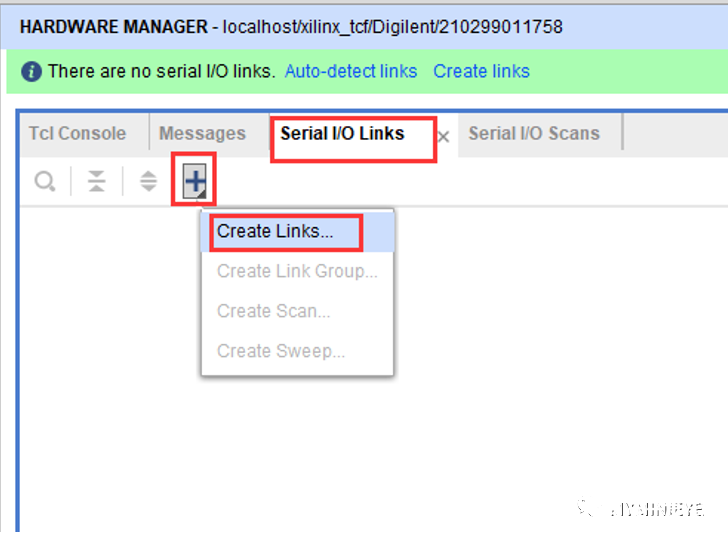

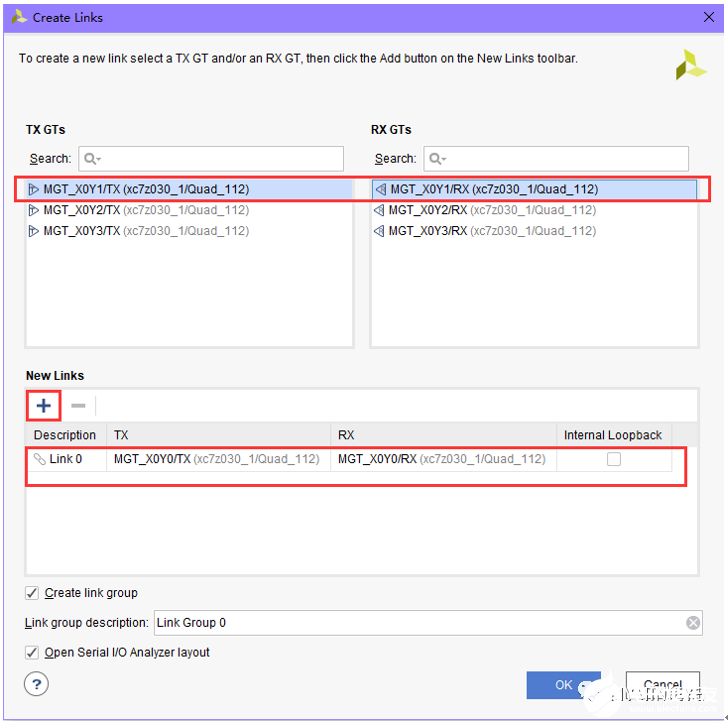

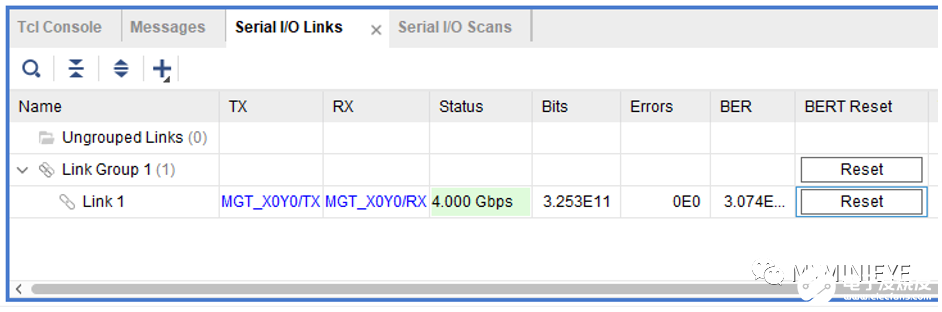

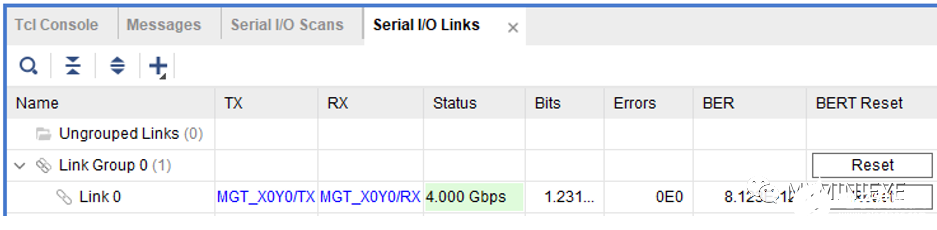

無需外部連線,燒錄成功后,在Serial I/O Links窗口創建連接,將同1個GTX中同一個通道的TX和RX建立link。(也可以選擇auto-detectlinks)

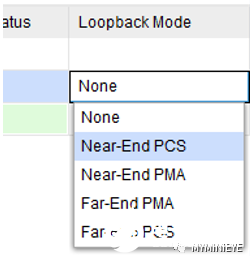

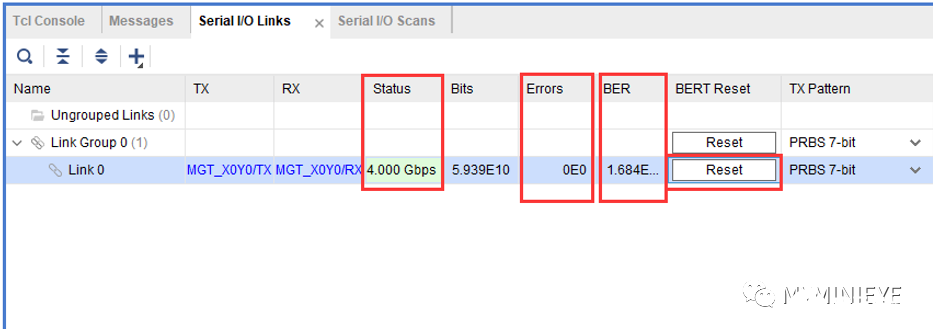

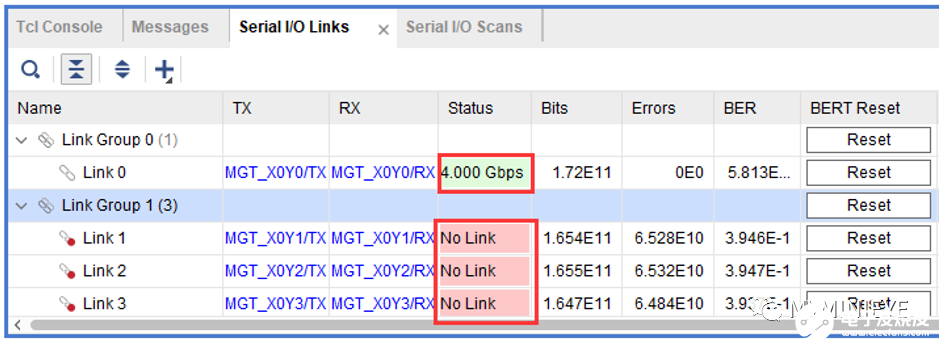

建立link后,若鏈路中連續五個數據傳輸成功,則認為鏈路連通,否則為未連通。在serial I/O link最右端的loopback mode選擇近端PCS(或PMA)環回模式,在改變模式時可能會出現誤碼,需要點擊reset重新監測。

經過一段時間測試, Errors的數值一直為0,表明測試過程中沒有出現誤碼,說明板級層面的GTX硬件工作穩定。

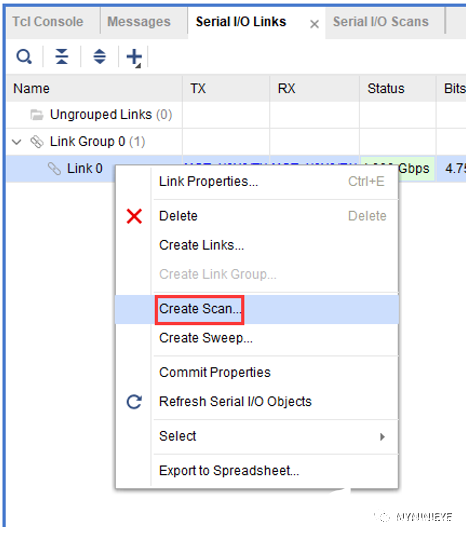

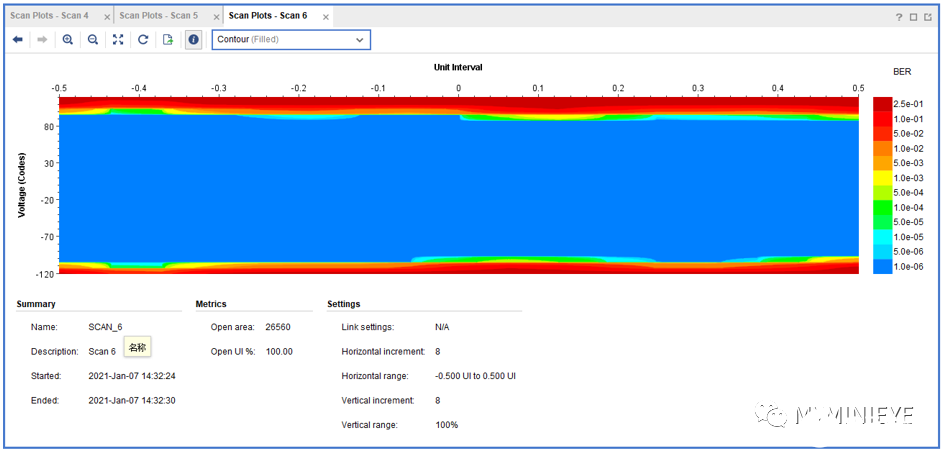

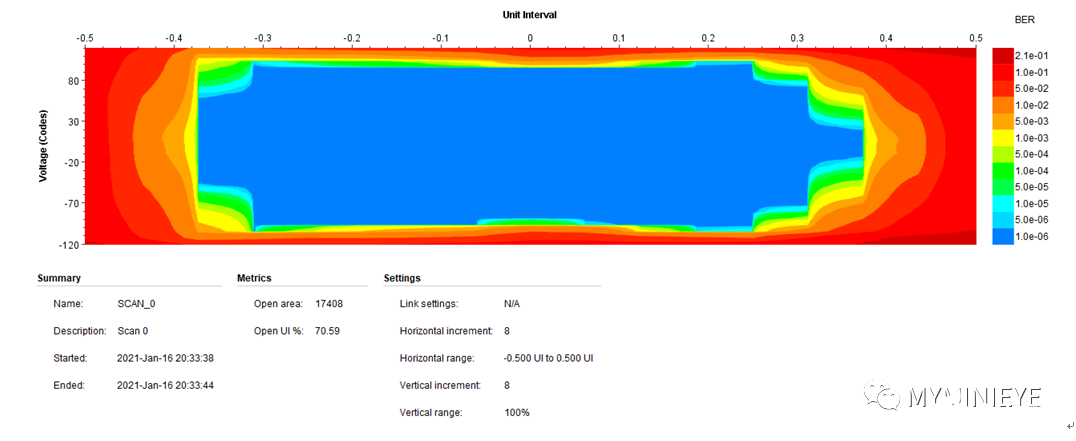

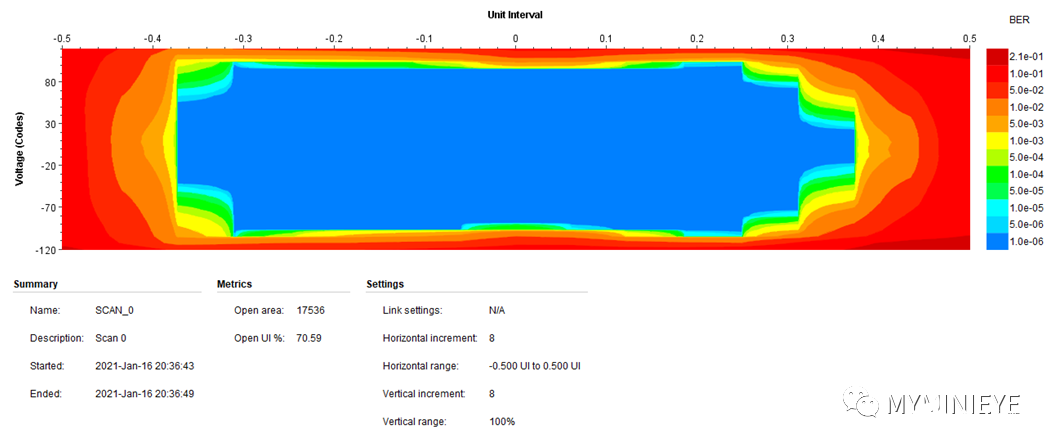

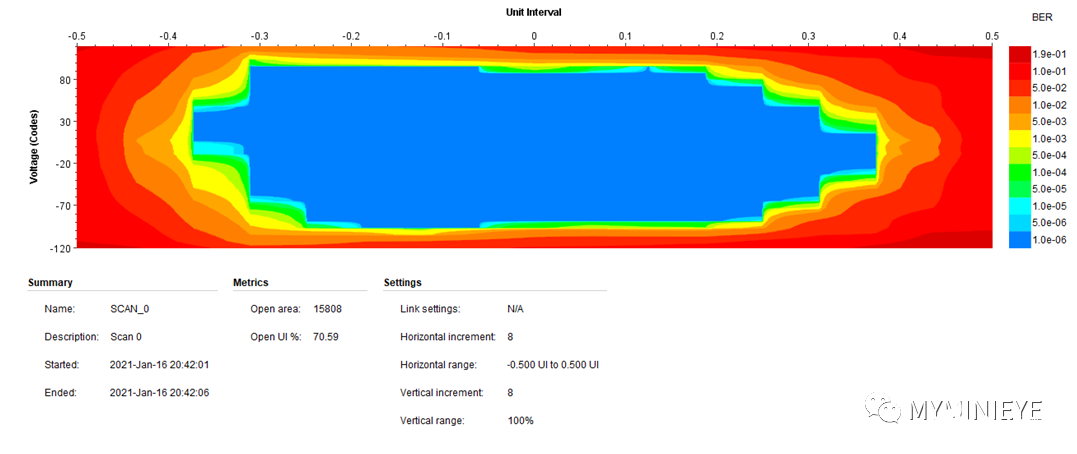

眼圖可以更直觀的觀察GTX的信號完整性,右鍵所連接的link,選擇create scan,便可以生成眼圖。

在Serial I/O link窗口中,errors為誤碼個數,BER為誤碼率,在reset之后,errors和BER會恢復為0重新統計,通常在改變其他的參數后可能會出現少量的誤碼,此時需要reset后重新統計誤碼。TX Pre-Cursor和TX Post-Cursor為預加重和后加重,TX Diff Swing為擺幅,RX Pattern和TX Pattern為輸入、輸出數據類型,提供不同位寬的偽隨機碼、慢時鐘(101010……)和快時鐘(11111111110000000000……),需要注意的是輸入和輸出的數據類型應設置為同一種類型,Loopback Mode為環回模式,默認為None無環回模式,Near-End PCS為近端PCS環回模式,Near-End PMA為近端PMA環回模式,Far-End PCS為遠端PCS環回模式,Far-End PMA為遠端PMA環回模式。若信號傳輸質量不夠理想,可以通過在serial I/O link的參數設置進行調整,再重新掃描眼圖查看是否有改善。

為了測試GTX四個通道的誤碼率,創建多個links,對四個通道都進行近端環回測試

(2)遠端PMA環回測試(Far-End PMA loopback)

在一個板卡上燒錄ibert生成的bit文件,將其中兩個通道的Tx和Rx接口互連,一個通道設置為Far-EndPMA模式,另一個通道設置為None模式并監測誤碼情況和眼圖。

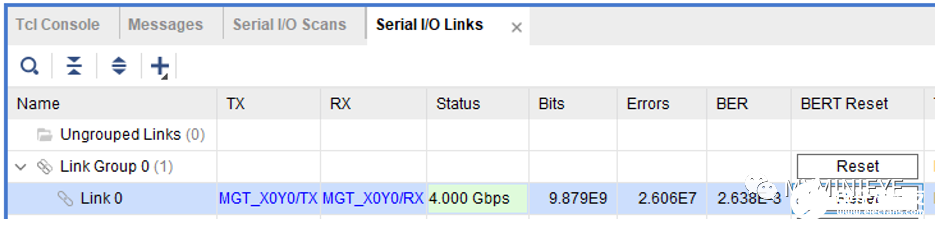

創建對應連接的link并查看誤碼率和眼圖

(3)遠端PCS環回測試(Far-End PCS loopback)

在一個板卡上燒錄ibert生成的bit文件,將其中兩個通道的Tx和Rx接口互連,一個通道設置為Far-End PCS模式,另一個通道設置為None模式并監測誤碼情況和眼圖。

創建對應連接的link并查看誤碼率和眼圖

(4)None模式的測試方式

板卡下載IBERT核生成的bit文件,然后將同一通道的Tx與Rx接口連接起來,環回模式設置為None,實現自發自收。

四、總結

通過環回和開環方式的誤碼率測試,可判斷出存在的問題以及測試出板卡實際支持的速率。IBERT可在運行過程中設置高速串行收發通道的各項參數,并提供了多種環回模式及多種測試激勵源,并可通過自動掃描測試,確定收發的最佳參數。可以滿足硬件測試時對高速串行收發通道信號測試的大部分需求,在故障定位等場合均可使用。

編輯:lyn

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614798 -

收發器

+關注

關注

10文章

3660瀏覽量

107506 -

檢查器

+關注

關注

0文章

16瀏覽量

3592

發布評論請先 登錄

gtx是光纖嗎

納芯微推出汽車級CAN收發器芯片NCA1145B-Q1

無線收發器工作原理,無線收發器怎么使用

高速接口7系列收發器GTP介紹

AN149 GD32VW553射頻性能和收發器功耗測試指南

高速串行總線系列-IBERT使用介紹

關于利用IBERT核對GTX收發器板級測試的原理與過程詳解

關于利用IBERT核對GTX收發器板級測試的原理與過程詳解

評論